一种航天接口芯片静电防护电路的软击穿现象*

马有为,温兆伦,李 猛,陈天培,王 楠

(上海航天控制技术研究所·上海·201109)

0 引 言

航天产品相对于普通产品具有一定的特殊性,如投入成本高、发射后不便维修、流程管控严格等特点。因此,航天产品尤其是深空探测器上的产品,必须能长期稳定运行,对可靠性要求极高[1]。电子设备是产品研制和生产过程中易受损的部分。航天产品全流程中对电子设备的防护,对提高产品可靠性具有重要意义。

除对电子设备的防护外,对外部影响的防护也十分重要。随着大规模、超大规模集成电路在航天电子设备上的广泛应用,产品性能不断提升、功能越来越复杂,对静电放电现象也越来越敏感,一旦电子设备被静电损伤,将延长产品的研制周期,增加研制成本,并使产品存在潜在的风险隐患。调查研究表明,有30%的芯片失效原因为静电放电(Electrostatic Discharge,ESD),因此ESD对产品的危害越来越受到重视[2]。相应地,对芯片静电防护的设计以及对芯片静电受损特性的研究也具有重要意义。

如在集成设计上,齐钊[3]提出了两种ESD保护器件新结构,实现了具有低电容的ESD保护阵列;卿乙宏[4]研究了25nm工艺的ESD防护电路设计;向洵等[5]提出了全芯片ESD保护电路设计方案。在外围电路设计上,宋文强[6]实现了ESD保护电路的抗闩锁设计;郑英兰等[7]提出了一种具有ESD防护功能的接口电路设计方案;M.Ker等[8]提出了改进的ESD钳位电路;Wang Z.等[9]提出了一种应用于高压的ESD防护电路。在专用ESD器件设计上,Zhang S.等[10]提出了一种应用于ESD的GGSCR器件。Lai D.等[11]提出了一种高压ESD防护器件;Liang H.等[12]提出了一种LDMOS-SCR-HHC的ESD防护器件;Du F.等[13]提出了一种改进的SCR用于ESD防护;Chen W.等[14]提出了一种新布局的nLDMOS器件;Chuang C.等[15]提出了一种DSCR器件用于ESD防护;Qi Z.等[16]提出了一种新型HTC-NPN用于ESD防护。在ESD测试上,吴昱旻等[17]阐述了测试ESD的方法;M.Rigato等[18]对射频开关的ESD行为进行了分析。

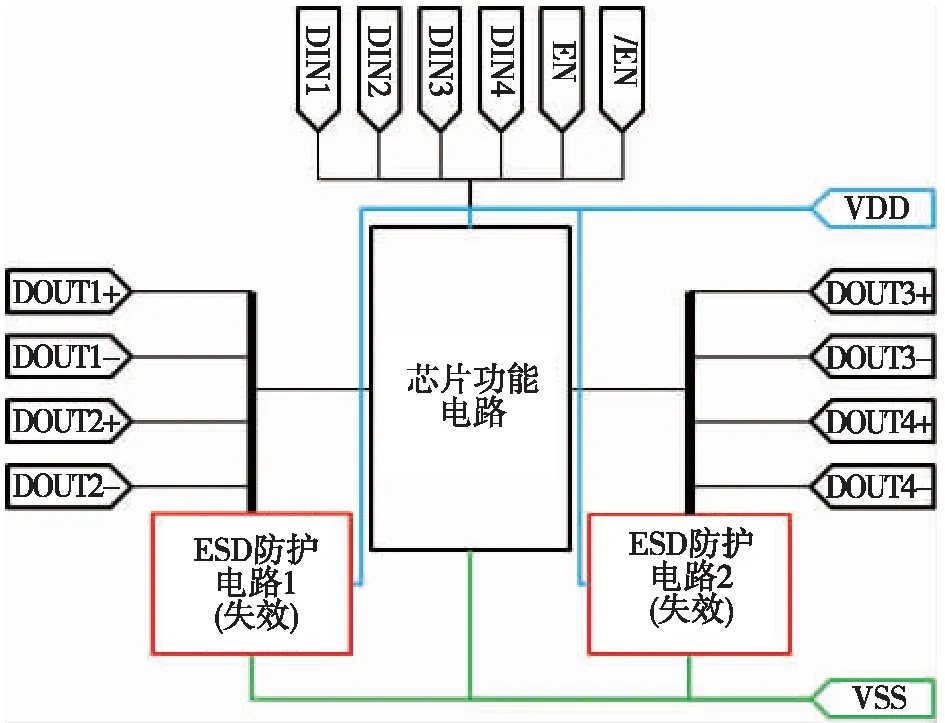

本文针对LVDS发送芯片进行了静电防护电路分析,LVDS芯片用于多探头星敏感器产品,每个探头均使用该芯片与线路盒独立进行通信,互为备份[19]。该芯片在航天产品的研制过程中,出现因静电损伤导致输入阻抗异常的现象,但该芯片上电后工作能力未出现异常,属于静电损伤中的软击穿。对该芯片的元器件失效分析结果将受损部位定位为芯片内部ESD防护电路。本文对该电路建立失效模型并进行深入分析,将失效点定位于电路内部某MOSFET在静电冲击下被击穿,等效为电阻。本文提出的静电软击穿现象,有助于航天电子设备中对静电现象的分析以及对产品影响的评估。

1 接口芯片异常分析

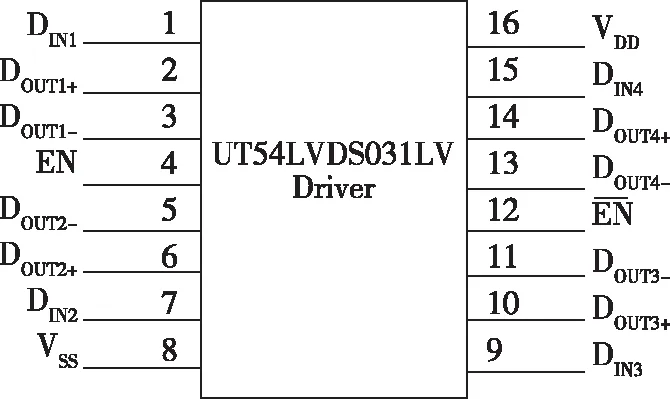

某航天产品在经过转运以及焊接板上其他器件的操作后,发现接插件上数个接点对地阻抗出现异常,经确认异常点均位于某接口芯片上,发现异常前后产品均未上电。该接口芯片为AEROFLEX生产的LVDS发送芯片UT54LVDS031LVUCC,质量等级为V级。该芯片引脚定义及内部逻辑如图1所示,共4路LVDS差分发送,每路存在一对差分输出信号,其中设计上使用3路差分信号完成与头部的SpaceWire通信,多余1路的输入端通过1kΩ电阻接地。

(a) 引脚定义

(b) 内部逻辑图1 芯片引脚定义与内部逻辑Fig.1 Definition and logic of chip

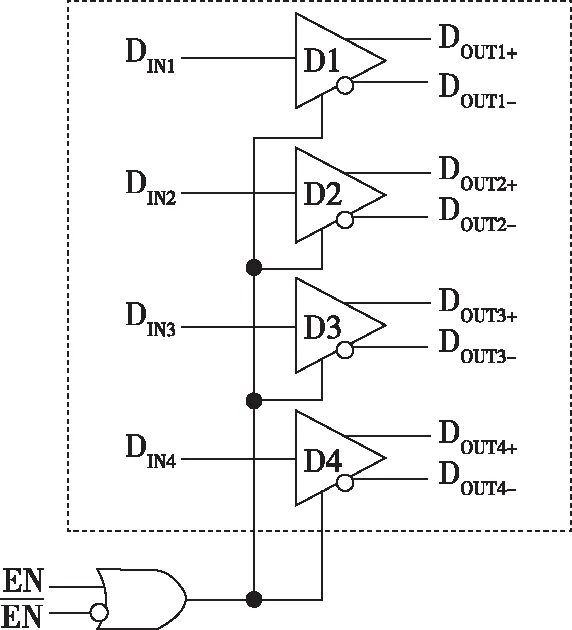

该芯片在产品上共有6片,且6片芯片外围电路一致,在产品测试过程中,仅此芯片出现异常,其余芯片测试结果均正常,发现异常前,该芯片已随产品正常工作超过600h。芯片在产品上的外围电路原理图如图2所示。

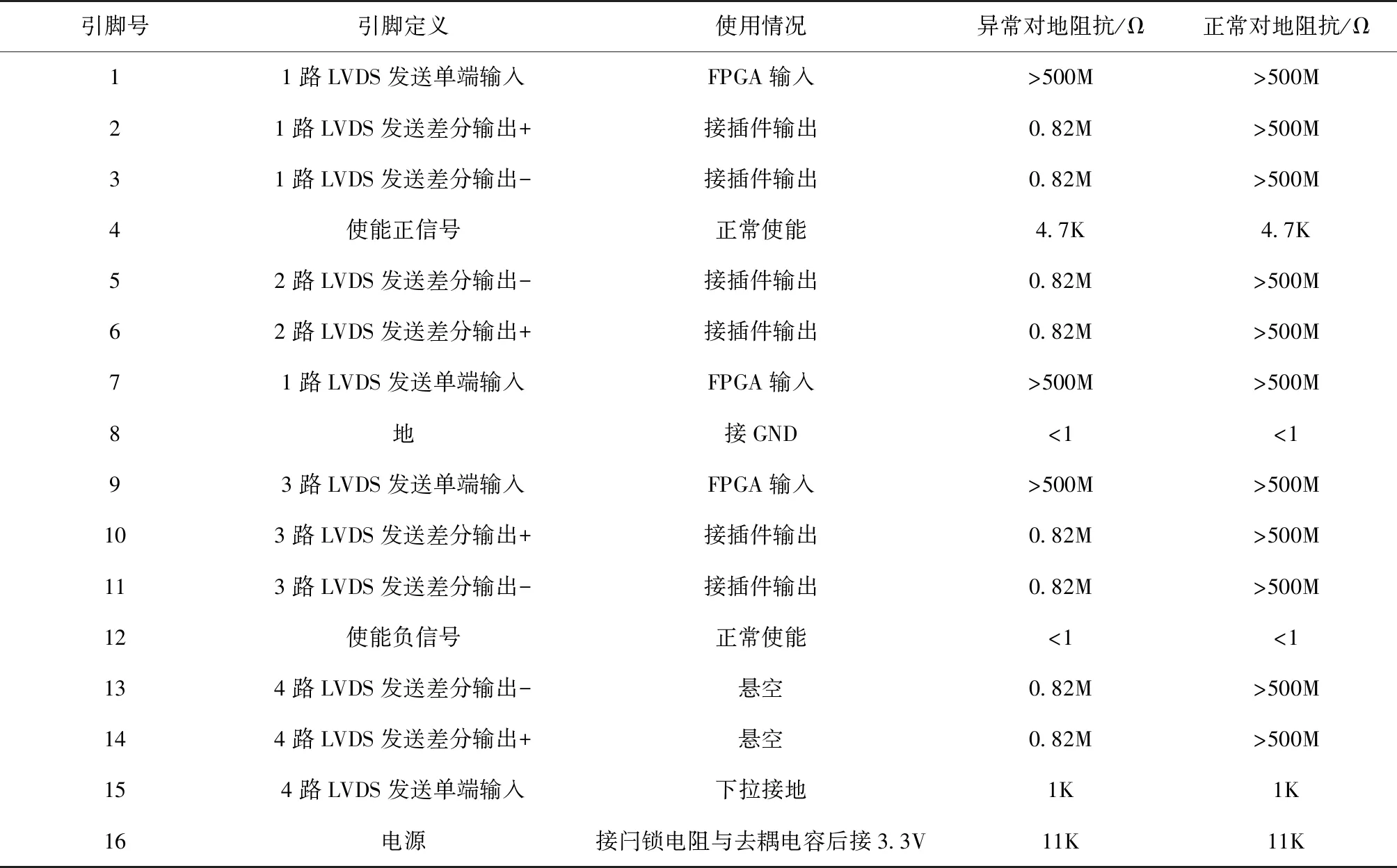

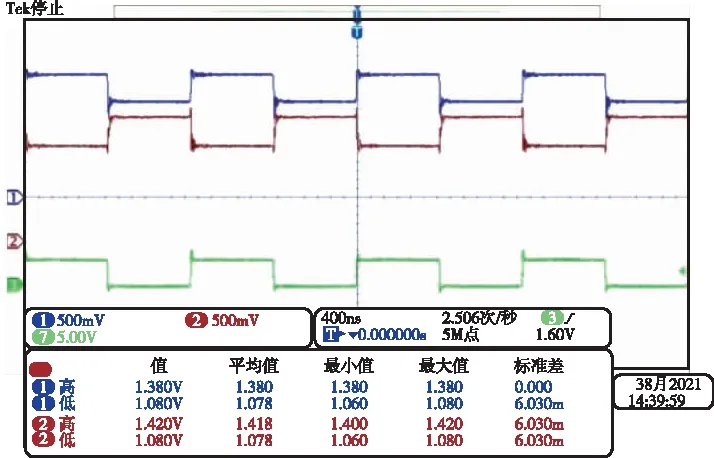

该芯片各引脚使用情况、测得的对地阻抗值与正常芯片对地阻抗值如表1所示。

图2 异常芯片电路原理图Fig.2 Circuit schematic of abnormal chip

表1 芯片阻抗异常现象对比

对该芯片阻抗异常现象分析发现,其存在以下几个特征:

1)异常管脚对地阻抗值高度一致,均为0.82MΩ;

2)除使用的3路通道外,剩余1路未使用的通道亦出现相同的阻抗异常现象;

3)产品在发现异常前后的时间内,始终处于未上电状态。

2 元器件失效分析

2.1 形貌对比

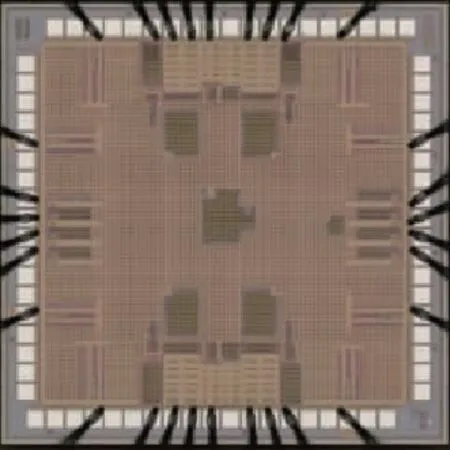

在对该芯片的整个失效分析流程中,均使用了一片与该芯片同批次的全新芯片用于对比,以分析该芯片的具体失效情况,异常芯片与样品形貌如图3所示。

(a) 异常芯片

(b) 同批次对比样片

对芯片进行外观检查,密封焊区未见明显腐蚀、开裂形貌,陶瓷壳体未见开裂、崩损,芯片外观未见异常形貌。使用X光设备对芯片进行X射线检查,其内部亦未见多余物、大面积黏结空洞等异常形貌。同时,按GJB548B—2005微电子器件试验方法和程序,方法2020.1试验条件A,对芯片粒子碰撞噪声检测(Particle Impact Noise Detection,PIND),芯片未见异常噪声爆发。依据GJB548B—2005方法2023.2非破坏性键合拉力试验对芯片进行测试,测试结果显示所有键合丝均合格。

使用机械方法对芯片开封后,对芯片内部进行内部目检。检查结果显示:芯片内部采用铝丝键合,未见键合丝塌丝、断裂,未见键合点脱落、腐蚀等异常形貌,芯片玻璃表面钝化层良好,未见互连断裂、桥连等缺陷,未见过热、过电损伤或机械损伤,典型形貌如图4所示。

(a) 芯片开封后形貌

(b) 芯片样品全貌

(c) 芯片1、2输出通道形貌

(d) 芯片3、4输出通道形貌

可见,该芯片在形貌与机械属性上状态良好,即芯片的阻抗异常并未带来机械损伤,或芯片的阻抗异常并非由机械损伤引起,即芯片的机械特性仍然正常,无法通过上述失效分析定位该芯片的失效位置。

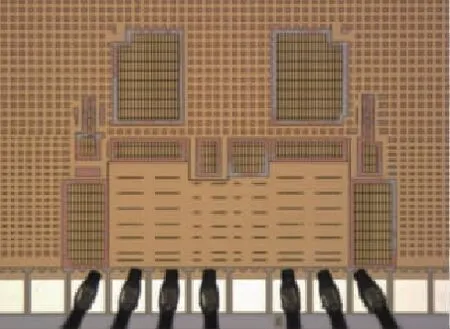

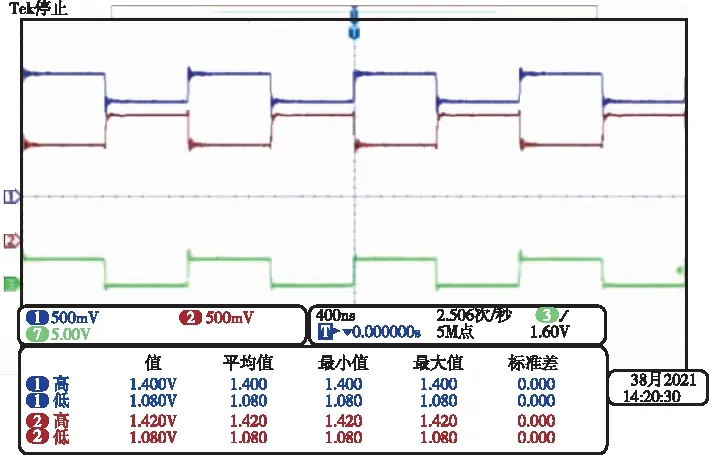

2.2 电特性测试

对芯片正常上电(3.3V),并对各个通道输入1MHz的方波信号,使用示波器捕捉输出,各个通道输出波形基本一致,试验结果如图5所示,其中蓝色信号为DOUT+、红色信号为DOUT-、绿色信号为DIN。可见该芯片在正常供电时,输出信号正常,满足LVDS电平要求,与产品测试过程中功能正常的现象一致,证明该芯片功能正常。

(a)异常芯片

(b)同批次对比样片图5 芯片输入输出波形测试Fig.5 Input and output waveform test

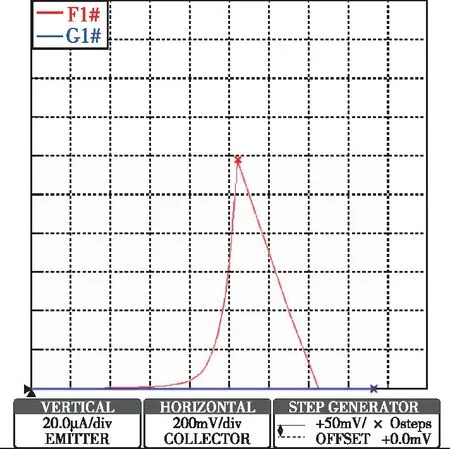

使用I-V图示仪对芯片各个引脚的电特性进行测试,芯片VDD对VSS之间的I-V特性曲线与良品对比存在差异,在电压升高后(约1.0V),出现跳变现象,跳变后,电压在约1.3V后回落,曲线与良品基本一致,如图6所示。该现象证明芯片在低压段存在漏电情况。

图6 VDD对VSS间I-V特性曲线图Fig.6 I-V characteristic curve from VDD to VSS

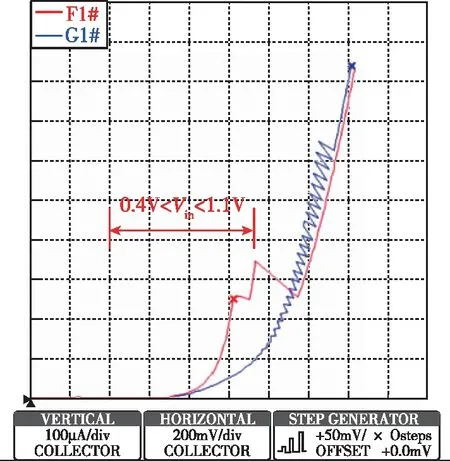

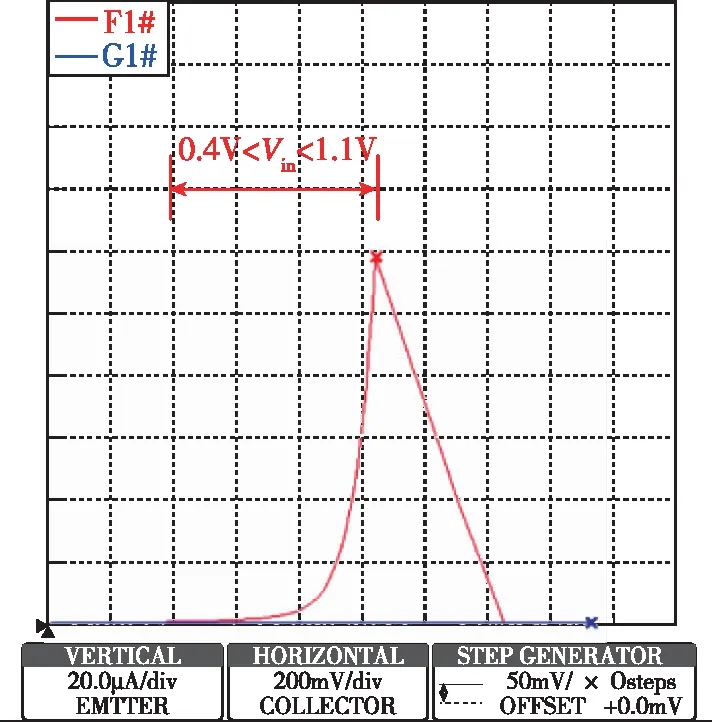

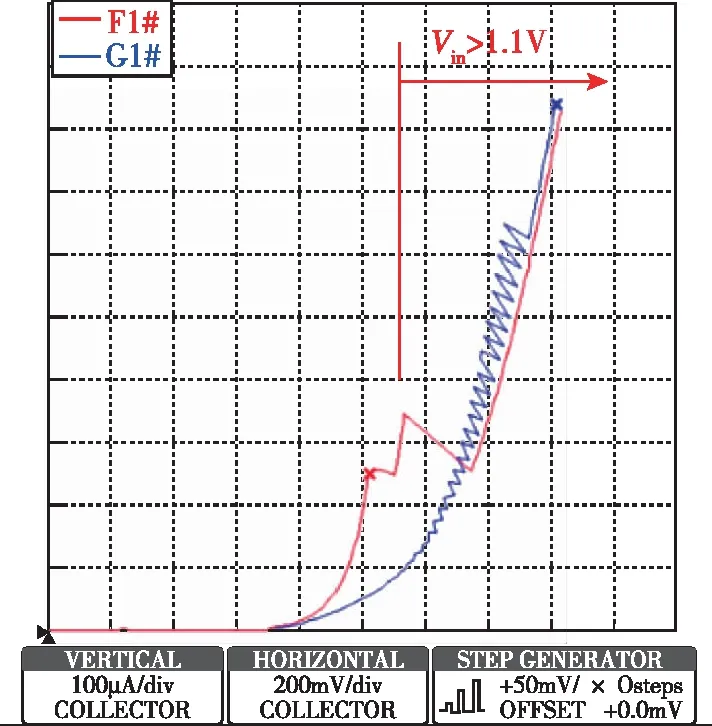

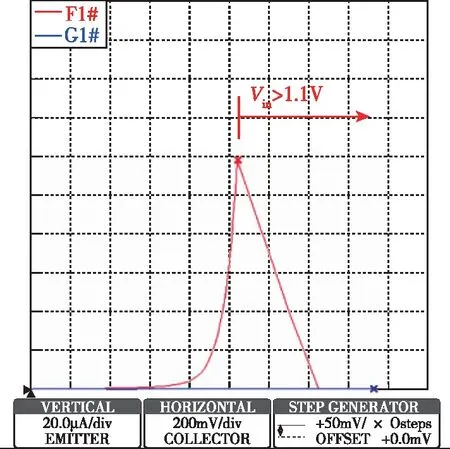

芯片8个差分输出端与VSS之间的I-V特性曲线与良品对比存在差异,典型曲线如图7所示。样品呈现正向导通特性,导通现象在约1.1V时跳变恢复至不导通状态,导通时最高电流约为120μA。

图7 输出管脚对地I-V特性曲线图Fig.7 I-V characteristic curve from output pins to VSS

对于图6和图7中的直线段,需要说明的是:由于I-V图示仪等效为功率源,故当其增加输出电压时,如果电路系统出现跳变,则图示仪会控制功率,导致I-V曲线出现跳变,到达该功率对应的下一个点,在图像中显示为两点间的一条直线。

通过上述试验可以说明,该芯片功能正常,但其VDD与输出管脚在低压段对地存在漏电现象,且该漏电在1.1~1.3V左右消失,远低于芯片正常的工作电压。该漏电正好与万用表测量电流重合,从而导致观测到阻抗异常,但功能正常现象。

2.3 OBIRCH定位分析

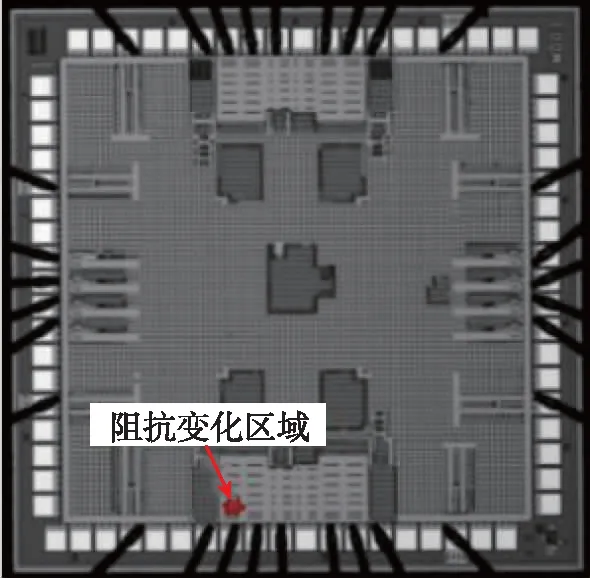

对芯片进行OBIRCH技术定位发现:

当样品通道输出端DOUT1+对VSS加电压1.04V(电流约92μA),其芯片DOUT1+端口晶体管位置存在阻抗变化,典型形貌如图8所示。对其他通道加压现象一致,阻抗变化区域均为其对应的输出晶体管。

图8 DOUT1+对VSS加电压1.04V时OBIRCH形貌Fig.8 The appearance of OBIRCH when DOUT1+ applies a voltage of 1.04V to VSS

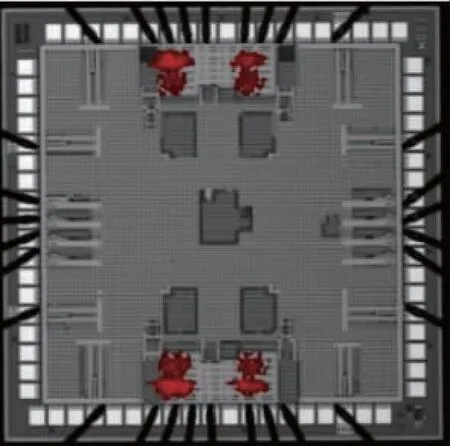

当VDD对VSS施加电压1.0V时,电流约221μA(良品为50μA,存在漏电),在4个通道共8个输出端口,芯片晶体管位置存在阻抗变化,典型形貌如图9所示。由芯片设计可知,该阻抗异常的区域为该芯片的ESD防护电路。

图9 VDD对VSS加电压1.0V时OBIRCH形貌Fig.9 The appearance of OBIRCH when VDD is applied to VSS with a voltage of 1.0V

当VDD对VSS施加电压升高至1.3V/3.3V时,电流约201μA/2.37mA(良品为221μA/2.38mA,电流基本一致),芯片的阻抗变化区域相比良品未见明显差异,输出晶体管处未见阻抗变化,典型形貌如图10和图11所示。

(a) 失效芯片

(b) 同批次对比样片

(a) 失效芯片

(b)同批次对比样片

由上述测试结果可总结以下情况:

1)该芯片在远低于正常工作电压的低压段(1.3V以下),相比良品出现了漏电(约0.4V开始)至漏电跳变消失(约1.1V)的现象,在1.3V以上至正常工作电压段的测试结果与良品一致;

2)根据图8和图9的现象,可以证明ESD防护电路在低压段存在漏电现象;

3)根据图8~图11的现象,可证明低压段存在阻抗异常的区域为芯片ESD防护电路,且仅在低压段存在阻抗异常区域,在高压段该阻抗异常区域消失;

4)输出端口对除ESD防护电路外的其他电路为隔离状态,因此对差分输出端口加压时,反映的I-V特性为ESD防护电路的I-V特性,结合图4和图5,可证明ESD防护电路在低压段确有漏电现象。

2.4 失效分析结论

经本章对该芯片的元器件失效分析试验,可见该芯片测得的阻抗异常,但功能正常现象,并非由机械损伤引起,结合产品在异常发生前后未上电的情况,判断该芯片表现的异常现象为静电致损。

由于芯片功能正常,仅在手持式万用表下测得其输出管脚对地阻抗异常,判断该芯片的静电损伤类型为静电软击穿。具体表现为:该芯片输出管脚在远低于正常工作电压的低压段(1.3V以下)出现了漏电现象,且该漏电现象在1.1~1.3V左右消失,在1.3V以上至正常工作电压段,该芯片特性正常。

3 电路机理分析

3.1 芯片电路设计与功能概述

经分析,确定导致阻抗异常的原因发生在该芯片的ESD防护电路上,其内部功能区域的简化划分如图12所示。片内共有2块ESD防护电路,对称分布,每块ESD防护电路被2对4路差分输出共用,即每4路差分输出端口到芯片功能电路之间的线路上并联了1块ESD防护电路。芯片输出阻抗异常系差分输出端口的ESD防护电路中第三级NMOS管出现损伤,导致ESD防护电路无法正常工作。而输入端口与使能端口未经过ESD防护电路,在此次静电中并未受到影响,芯片功能电路亦未被损伤,因此芯片功能依然正常。

图12 芯片内部功能区块情况Fig.12 The functional blocks of the chip

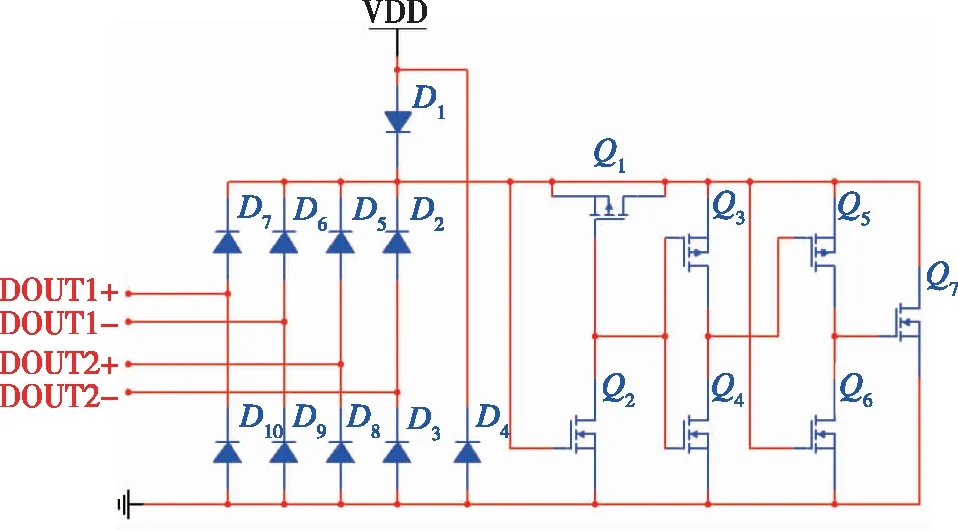

差分输出端口的ESD防护电路如图13所示。虚框中的电路是4个差分端口共用的,即虚框中的电路有异常时将影响到4个端口的阻抗特性。该芯片对称的有2个这样的电路,分别被4个差分端口共用。同时为防倒灌,输出管脚与芯片功能电路设计为二极管隔离状态,即从差分端口加电压时,只要电压不高于二极管的反向击穿电压,输出端口进入的电压不会对芯片功能电路产生影响。

图13 LVDS差分输出端口ESD防护电路Fig.13 The ESD protection circuit of LVDS differential output port

由于该部分电路为4个端口共用,由二极管进行隔离,且输出阻抗特性一致,因此发生损伤处应为公共部分,可简化为一路差分输出端口进行分析,以DOUT2-为例。

图13中的反向后,使Q5关断,进而使Q7关断,使低阻通路消失,以避免该电路影响芯片功能电路的正常工作。

MOS管分为四级电路,第一级为Q1、Q2管,第二级为Q3、Q4管,第三级为Q5、Q6管,第四级为Q7管。其中,Q1、Q3、Q5为P沟道MOS管,Q2、Q4、Q6、Q7为P沟道MOS管。且这些MOS管设计为漏极(D)、源极(S)不分,即对于NMOS管,两极中电压更低的一极为S极,另外一极为D级;对于PMOS管则相反。在这种情况下,MOS管的体二极管始终反偏。

其中,Q1管将D极、S极接在一起时,MOS管等效为G极与D、S极之间的一个平板电容器;其余MOS管均为开关(电阻)接法。此外,Q7管相比其他管体积更大。

静电防护电路的机理为:当静电进入时,Q1快速反应(1~10ns),在其他电路未建立通路时,提供一个低阻通道将静电电流由ESD防护电路泄放掉。

静电防护过程为:当静电到达Q1的D、S极时,Q1将D、S极的上升沿电压耦合至G极,使其G极变为高电平,使Q7导通,静电通过Q6、Q7同时泄放,进而完成ESD保护功能。

Q2的作用为:当电压到达电路的稳态工作电压后,Q2打开导致Q1、Q3、Q4的G极为低电平,进而使Q7关断,低阻通路消失,以避免该电路影响芯片功能电路的正常工作。

3.2 失效机理分析

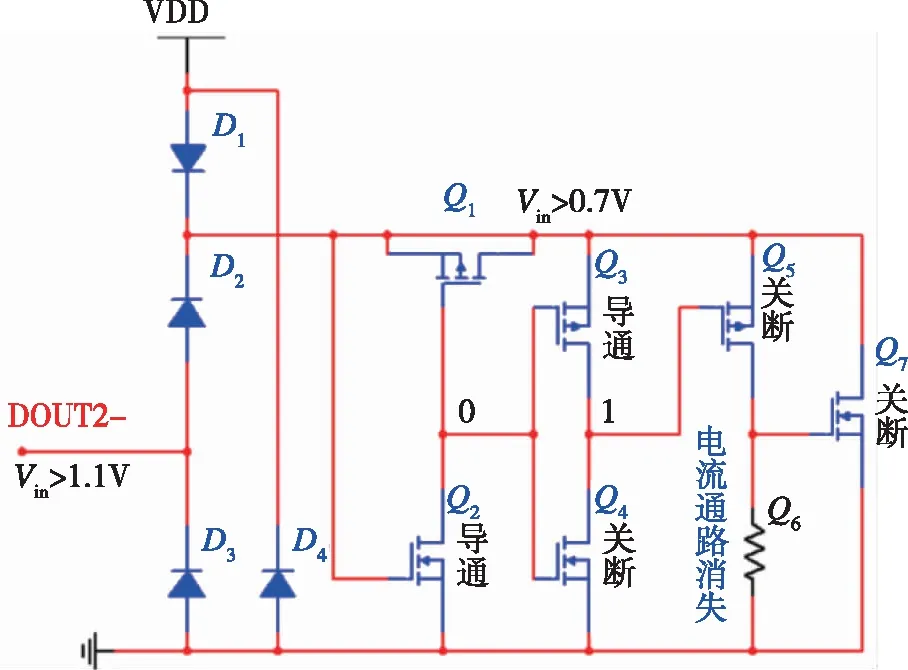

导致异常的MOS管为Q6管,并击穿为一个电阻状态,等效电路如图14所示。

图14 Q6击穿后的等效电路Fig.14 The equivalent circuit after breakdown of Q6

对Q6击穿后的等效电路分析有以下前提:

1)图中二极管导通电压不定,存在亚阈值区域,与工艺、面积、电流等均有关系,一般在0.4~0.6V左右完全导通;

2)图中的MOS管强导通电压阈值为0.7V,即在G、S极之间加电压超过0.7V时(NMOS管栅源电压Vgs>0.7V,PMOS管Vgs<-0.7V),MOS管的D极与S极导通,等效为一个极小的电阻;

3)图中PMOS管存在亚阈值区,即当Vgs电压处于亚阈值区内时,D与S极之间存在微弱导通现象,有微弱电流流过(漏电),并随着G极的电压逐渐增大,漏电逐渐增加,直至达到强导通状态;

4)初始状态下,可认为MOS管的G极接近零电平电位。

基于上述前提,对异常电路进行分析,以对DOUT2-输出管脚加正向电压Vin为例,设定二极管导通电压均为0.4V:

1)Vin<0.4V时,D2不导通,该电路中无电流流过。

2)Vin>0.4V时,D2导通,经过D2压降后,电压为V=Vin-0.4。

3)Vin>0.4V,但<1.1V时,此时电路状态为:

Q1等效为电容,可忽略;

Q2由于Vgs未达到阈值电压0.7V,不导通,其D极等效为断路/零电位状态;

Q3由于G极为断路/零电位状态,即使发生弱导通,也会因Q4的G极为断路/低电平的不导通状态而没有电流通路,故Q3、Q4无电流流过;

Q5由于G极为断路/零电位状态,而S极电压0.4V 图15 0.4V 该段亚阈值区的微弱漏电现象对应失效分析试验中测得的I-V特性曲线,标注如图16所示。 (a) VDD对VSS I-V特性曲线 (b)输出端口对VSS I-V特性曲线图16 0.4V Q7由于G极未达到导通阈值,不导通。即Vin处于该范围内时,Q6上有电流流过,万用表测得该电流,即会造成测得阻抗降低的现象。由于弱导通现象在越接近强导通阈值时越强,因此在输出管脚处测得的电流随着输入电压的增大而逐渐增大,与电压大于0.4V后I-V特性曲线相比,良品出现大幅度偏高的试验现象匹配。 4)Vin>1.1V时,由于D2压降导致Q2的G极刚达到0.7V的导通阈值,此时Q2立即导通,D极被拉至低电平,使Q3与Q4组成的反相器输出高电平,即加在Q5的G极上的电平为高。此时,由于Q5的S极电平也为高,即Vgs趋近于0,因此Q5关断,消除了电流通路,Q6上没有电流通路流过,Q7此时也由于G极为低电平而不导通,如图17所示。 即Vin>1.1V时,该电路上的电流通路消失,与在1.1~1.3V时管脚的I-V特性曲线恢复到与良品一致的现象相匹配,如图18所示。 图17 Vin>1.1V时的电路情况Fig.17 Circuit when Vin>1.1V (a) VDD对VSS I-V特性曲线 (b) 输出端口对VSS I-V特性曲线图18 Vin>1.1V时的I-V特性曲线Fig.18 I-V characteristic curve when Vin>1.1V 经上述电路分析,当Q6被击穿为一个电阻时,电路现象与测得的情况一致,可认为阻抗异常情况与上述分析一致。 基于上述分析,进行NMOS管Q6被击穿的可行性分析,主要判据有: 1)因测试中发现8个端口都出现了同样的问题,因而基本可以排除电应力来自于差分端口,电应力预计来自于如VDD、VSS这样的公共端口,可以从二极管直接加载到ESD防护电路中; 2)由于在测试发现异常前后电路未上电,且焊接电阻的操作与地密切相关,故怀疑导致电路损伤的电应力来自于VSS; 3)NMOS管本身相对PMOS管更容易被击穿,且如电应力来自于VSS,则首先受到冲击的也是与地更近的NMOS管,更加容易使NMOS管被击穿; 4)Q6被击穿后的电路模型符合试验现象:如果是Q2、Q4被击穿,则由于其D极与S极之间没有电流通路无法产生电流,如果是Q7被击穿,则电流通路一直存在,应始终存在漏电现象,而不会在电流增大后漏电消失; 5)由ESD防护机理分析可知,在对静电进行泄放时,Q6与Q7将承受相同的电压与电流,而Q7相比Q6面积更大,承受能力更强,因此当静电进入时,Q6比Q7更容易被击穿。 结合电路机理分析与上述可行性分析,该芯片使用过程中存在Q6被击穿的可能。结合发现异常前后产品未上电的情况,推断该芯片阻抗异常的原因为静电导致Q6被击穿。 推测可能性最大的静电来源为:电荷为从VSS加载进电路的负电荷,由于电荷为负,故击穿时的电流流向与前文分析的ESD防护电流流向相同,且电荷直接冲击Q6、Q7。同时,由于印制板外部装配有机壳,且机壳地与印制板GND平面联通,机壳地存在大面积区域可以引入外部静电至印制板GND平面,因此,该种静电途径发生概率最大。即Q6是在对静电进行泄放时被击穿的,静电途径如图19所示。 图19 静电(负电荷)进入途径与等效电流Fig.19 Static (negative charge) entry path and equivalent current 经本节电路机理分析,定位该芯片的阻抗异常现象产生的原因为:该产品在转运和焊接过程中印制板受到静电冲击,导致LVDS驱动芯片内部ESD保护电路中的一个NMOS管被击穿为等效的电阻(由于片内有2块一样的NMOS管,故实际有2个对称的NMOS管被击穿)。且推测该静电大概率为从印制板GND平面进入的负电荷静电。 此外,在此种失效模式下,该芯片在一定程度上可以认为未失效: 1)该芯片在正常工作电压下,通信能力仍然正常,即内部主要功能电路未受损; 2)在本文中的失效模式下,ESD防护电路中虽然一个NMOS管(Q6)被击穿成为一个等效电阻,但该等效电阻并不影响该ESD防护电路在静电进入时的启动,Q6与Q7仍然可以作为静电泄放通道来释放静电,即该ESD防护电路仍然具有静电防护作用; 3)该芯片的漏电现象在1.3V以上消失,故不影响该芯片在正常工作电压下的工作,即该芯片在正常工作电压下与正常芯片没有差异。 本文研究了一种接口芯片在静电打击下的静电软击穿现象,具体表现为该芯片的输出引脚对地阻抗从正常的>500MΩ降低至0.82MΩ,但该芯片上电后,功能正常,并未产生失效。基于元器件失效分析的方法,将异常区域定位到了该芯片的ESD防护电路。基于对该ESD防护电路的分析,确定了受到静电影响的器件为静电防护电路中第三级中的NMOS管被击穿,并等效成为一个电阻。该击穿使得该芯片在1.1V以下时,其上方的PMOS管在亚导通状态下的漏电经过该NMOS管流经芯片的地信号,从而被手持式万用表测得,使得表显阻抗明显降低。 但该失效模式下,该芯片的功能电路未受损,且受到一定影响的ESD防护电路依然具有静电防护功能。仅因低压段漏电使手持式万用表测得其对地阻抗降低,且该漏电现象在芯片正常工作电压下消失,故不能充分认定该芯片已经失效,即阻抗异常并不是芯片失效的充分条件。 目前,航天基于接口芯片测量的方法对产品状态进行初步判定,当发现阻抗异常时,则认为相关器件已经失效。但本文研究显示,芯片受到静电影响后,依然具备正常功能,但阻抗测试出现异常。因此,阻抗测试的异常不代表芯片失效。在实际应用中,应该根据芯片实际表现与产品使用需求进行处置。例如,若该产品为航天飞行件,则为避免存在未被发现的失效情况,保证产品的可靠性,应更换该器件;若该器件为地面试验件,则可在芯片工作能力正常的情况下,继续使用该器件,以节省研发成本,缩短研发周期。

3.3 静电击穿可行性与静电来源分析

3.4 小结

4 结 论