一种低载噪比突发扩频信号的快速捕获方法实现

张兰粉,王 迪,张亚林,杨再秀

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.北京卫星导航中心,北京 100094)

0 引言

突发扩频信号如卫星无线电定位业务[1-4](Radio Determination Satellite Service,RDSS)是北斗卫星导航系统的特色,是在系统提供RDSS定位授时服务的基础上,借助短报文的形式为用户提供位置报告或双向短报文交互。基于RDSS短报文通信建设的民用服务平台将与地面公共移动通信、卫星通信和互联网等系统互联互通,通过市场化方式运作,面向大众市场开展商业化服务,有力提升北斗系统特色优势和质量效能,带动北斗产业发展,推动北斗产业在经济社会发展各行业各领域的规模化应用。结合实际需求,突发扩频信号具备大容量、低载噪比和高动态等特点。针对这些特点,开展低载噪比突发扩频信号快速捕获技术研究,其性能将直接决定入站信号接收的成功率,同时也是整个系统接收能力的直接体现。

传统扩频信号的捕获方法[5-7]包括线性搜索法、并行码相位搜索法、并行频率搜索法等。线性搜索法在时域内进行搜索捕获,方法简单,硬件实现容易,但搜索速度慢,无法满足实时捕获的需求[8-10]。并行码相位搜索法可将多次码相位搜索通过傅里叶变换一次性完成,搜索更快捷,但需要完成2次傅里叶变换和一次傅里叶反变换,运算量很大,不利于硬件实现[11-15]。并行频率搜索法是对每一个码相位的搜索都进行一次傅里叶变换,搜索速度和运算量适中[16-18]。

针对大容量、低载噪比、高动态的突发扩频信号特点,提出了一种分段匹配滤波器加多普勒并行相干积累的方法。该方法基于硬件实现从算法到工程进行全流程优化设计,以实现最优的捕获性能,捕获结果能够实时计算,载噪比可达39.5 dBHz,多普勒搜索范围可达±6 kHz,多重信号重叠错开时间3码片,检测概率高达99%,虚警概率小于10-6,通过Virtex-7 690T进行实现,硬件资源占用小于65%。

1 模型分析

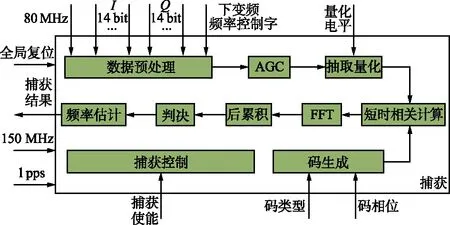

分段匹配滤波器加多普勒并行相干积累的快速捕获单元原理如图1所示。

图1 快速捕获单元原理Fig.1 Principle of fast acquisition unit

该结构针对大容量、低载噪比、高动态的突发扩频信号进行设计,二次量化压缩输入信号的比特数,二次量化的数据用3 bit表示;匹配滤波器用分段匹配滤波器替换,各个通道可以共享;多普勒并行相干积累用快速处理方法也能进一步提高运算效率。以上变形处理都会带入额外的处理损耗,但能大幅提高运算效率。

快速捕获单元专门配置了噪声通道估计模块,用来实时估计通道噪声。由于干扰等因素,可能会导致噪声通道出现波动,只有实时估计噪声通道的功率,才能保证捕获和虚警概率性能达到最优。

为了消除相关峰可能出现的“拖尾”、畸变,取大判决还需要对相关峰进行整形处理,然后与捕获门限比较,若超过门限,则向跟踪单元发出捕获脉冲信号。

2 硬件设计原理

快速捕获单元在FPGA上设计实现,型号为Xilinx Virtex-7 690T。快速捕获单元整体硬件结构框图如图2所示,由载波搜索和码相位二维并行搜索组成。采用基于分段短时相关的并行捕获搜索算法,在此算法基础上根据功能划分各个子函数,分别进行设计,最终完成整个捕获方案的设计实现。划分的各个子函数主要包括数据预处理函数、AGC函数、抽取量化函数、码生成函数、分段短时相关计算函数、FFT函数、后累积函数、捕获判决函数和频率估计函数。

图2 快速捕获单元整体硬件结构框图Fig.2 Overall hardware structure of fast acquisition unit

在数据预处理函数[7]中,首先对数据信号进行直流分量去除,再通过与本地产生的正弦、余弦信号进行混频实现下变频,然后进行FIR滤波。去除直流分量通过累计求和取平均的方式实现对直流分量的计算,求和计算的数据个数为29=512。下变频首先实现本地载波的正余弦信号产生,再通过与信号相乘实现频谱搬移。正余弦信号产生通过坐标旋转数字计算机(Coordinate Rotation Digital Computer,CORDIC)算法实现。数字下变频示意如图3所示。

图3 数字下变频示意Fig.3 Schematic diagram of digital down conversion

CORDIC算法原理的核心思想是规定旋转角度,然后通过不停迭代逐步逼近实现数学求解。具体实现方法为,设置迭代次数为16,则x0=0.607 253,y0=0,并输入待计算的角度z0=θ,θ∈[-99.7°,99.7°]。根据3个迭代公式进行迭代:

经过16次迭代计算后,得到的x16和y16分别为cosθ和sinθ。

FIR低通滤波器是基于Kaiser窗设计实现的[19],采样频率为80 MHz,截止频率为16.32 MHz,设计滤波阶数为62。

通常AGC[20]处于接收机的数字下变频之后,通过反馈的形式,以AGC的输出数据能量为标准,对输入AGC的数据幅度进行调整,达到控制功率的目的。

从具体的实现方式来看,AGC的输入数据首先经过能量平均函数,计算出一段时间的采样点平均能量。设这段时间内的采样点数为N,为了保证平均能量的准确估计,N的值应当取得足够大。同时,为了保证N个采样点之间的信号能量不发生显著变化,N的值又应当取得足够小。设计中可以把该值设为可调,根据实际情况测定,本文N=512。

平均能量输入对数查找表函数,对能量值取对数之后将该对数能量与参考值的对数值相减,所得的结果送入运算判决函数,该函数的输出作为指数查找表的输入地址,输出的数据就是取2的指数次方的输出,然后将该输出与输入数据进行复数乘法,实现功率控制。数字AGC运算流程如图4所示,初始增益为1。

图4 数字AGC运算流程Fig.4 Operation flow of digital AGC

抽取量化函数的主要功能是将AGC之后80 MHz的数据进行抽取,抽取之后的频率为16.32 MHz,然后再将I,Q两路数据分别进行3 bit量化。数据抽取通过查找表的方式实现,设定250抽取51的查找表,避免长时间积累导致的数据相位偏移。量化通过外部设置固定的量化电平,最优量化电平通过仿真计算获得。

分段短时相关计算函数[21-22]将15 ms的同步头分割成3段,每段作256点的FFT运算,每段的FFT结果求包络之后进行后积累(即后积累3次)。用于FFT运算的5 ms数据又分割成约136小段作基本的匹配滤波处理,即每小段包括150个码片(600个采样点),其流程如图5所示。

图5 分段相关计算函数Fig.5 Segment correlation function

FFT计算函数采用Matlab系统函数,通过补零完成256点FFT运算。捕获判决函数对单次FFT运算结果进行取大运算,然后再与判决门限做比较。由于频率搜索范围为±6 kHz,故FFT的输出频域值X(k)(k取0~255)只有一半的数据有效,k的有效范围[0~63,191~255],即对128点复数进行取大运算。FFT运算是并行实现的,故同时对128点复数求平方和,获得128点实数,然后两两进行比较运算,经过7次比较运算即可获得最大值,求最大值的过程同时保留相对应的kmax值,最终输出kmax值和频域值X(kmax),X(kmax-1),X(kmax+1)。

频率估计函数对136个点补零作256点的FFT运算,则FFT结果的频率步进106.25 Hz。FFT的输出为-128~+127,-128对应-136 001 Hz,+127对应+13 494 Hz。由于只需要处理±6 000 Hz,因此实际感兴趣的FFT输出在-64 ~+63。

假设某次检测,最大值Pkmax超过判决门限,其左边值记为Pkleft(若Pkmax出现在第0,1,2或3,则Pkleft从第3,0,1或2中提取),右边值记为Pkright(若Pkmax出现在第0,1,2或3,则Pkright从第1,2,3或0中提取)。然后对kmax修正得到:

最后按照信号处理终端的频率分辨率计算频率信息,则上述结果乘以系数106.25/16,然后四舍五入获得最终的信息。

3 仿真与硬件设计

突发扩频信号的同步头时长15 ms,扩频码速率为4.08 Mc/s,载噪比为39.5 dBHz,多普勒频偏为±6 kHz,多重信号重叠错开时间为3码片。

根据设计方案,在Matlab中实现数学运算模型,运算实现的过程全部基于定点位宽,与Verilog的计算精度保持一致。FFT运算在Verilog的实现上采用Spiral DFT/FFT IP,此IP没有对应的运算模型,故验证模型关于FFT的运算部分直接采用Matlab系统函数实现。其余运算模型均与Verilog模块保持1∶1的一致性。

4 结果分析

Virtex系列FPGA采用28 nm工艺实现,具有丰富的逻辑资源和优越的运行性能,该快速捕获方案在Virtex-7 690T上设计实现,使用的资源如表1所示,快速捕获单元硬件板卡机箱如图6所示。

表1 快速捕获模块资源占用

(a) 快速捕获单元板卡

传统捕获方法只能成功捕获一个用户后跟踪处理完成再进行下次捕获。该快速捕获方法在设计上可实现多重信号重叠错开时间3码片,捕获与跟踪实时进行无需等待,从而大大提高捕获速度。

如果采用9 ms的同步头捕获,在Virtex-7 690T芯片上设计,FPGA硬件资源占用65%以上。为了满足载噪比39.5 dBHz,多普勒搜索范围±6 kHz的要求,本方法采用15 ms同步头捕获,如果采用传统的分段相干积分和FFT并行计算方法,FPGA硬件资源占用将达到108%。

为节省FPGA资源占用,本方法采用了2项改进措施:① 相干积分器奇偶复用。通过分析相干积分实现算法得知,如果通过合理设计基带数据的采样率,能够实现相干积分器的复用,从而降低积分器的资源占用率。例如采用2倍码率对输入基带数据进行重采样,则奇数和偶数相关器可以通过时分的方式复用,减少近50%的相关器资源。② 全流水式分段积分和FFT计算。分段积分和FFT计算是捕获的两大关键部分,传统捕获设计在分段积分完成后,再启动FFT计算。因为二者共用了相关值的存储空间,因此只有等待所有相位的FFT计算完成后,才能启动下一次分段积分计算,即在FFT计算期间,分段相干积分器是处于空闲状态,造成了逻辑资源的闲置。本方法采用相关值交织存储的技术,实现了分段相干积分和FFT的全流水计算,可以进一步节省FFT和相关器的资源。

通过上述设计,最终15 ms同步头快速捕获实现在Virtex-7 690T芯片上硬件资源占用率小于65%。

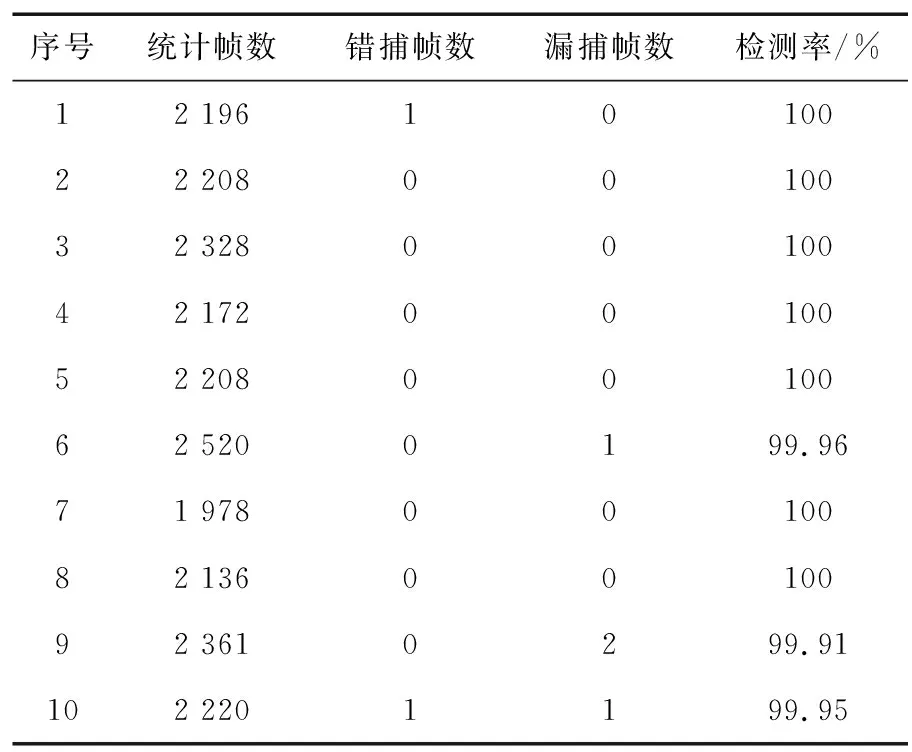

信号源产生载噪比为39.5 dBHz的信号,频率覆盖-6 000~6 000 Hz,间隔620 Hz,通过上述捕获设计,获得捕获频率结果如表2所示,快速捕获单元捕获检测率如表3所示(多普勒±6 kHz)。

表2 捕获频率结果

表3 快速捕获单元捕获检测率

由表2和表3可以看出,对于载噪比为39.5 dBHz,频率覆盖-6 000~6 000 Hz的信号,快速捕获频率精度即频率估计误差小于50 Hz,检测率即错捕帧数与统计帧数比大于99%,虚警概率即漏捕帧数与采样频率16.32 MHz比远远小于1×10-6。

本文方法通过硬件实现,捕获结果实时计算,载噪比可达到39.5 dBHz,多普勒搜索范围可达±6 kHz,多重信号重叠错开时间3码片,检测概率高达99%,虚警概率小于1×10-6,Virtex-7 690T硬件资源占用小于65%。

5 结束语

突发扩频信号利用并行频率搜索法,原理简单易于实现,但在硬件实现过程中资源消耗较大,尤其对于大容量、低载噪比、高动态扩频信号的实时捕获存储和逻辑资源消耗更高。本文提出分段匹配滤波器加多普勒并行相干积累的改进方法,根据具体应用需求和硬件平台资源,采用相干积分器奇偶复用和相关值交织存储2种技术,实现硬件资源占用率降低。

未来北斗短报文通信由传统专用终端应用,迈入面向大众手机直接提供服务的新阶段,届时提高系统服务容量,降低终端发射功率将成为设计的重点,本文方法可以为大容量、低载噪比和高动态扩频信号的实时捕获提供参考。