双电层氧化锌薄膜晶体管偏压应力稳定性

王 聪, 刘玉荣, 彭 强, 黄 荷

(1. 汕尾职业技术学院 海洋学院, 广东 汕尾 516600;2. 汕尾市海洋产业研究院 新能源材料与催化工程研究中心, 广东 汕尾 516600;3. 华南理工大学 微电子学院, 广东 广州 510640)

1 引 言

近年来,采用环保可降解的天然生物材料制备生物兼容性功能器件越发受到关注,其中用天然生物材料制备薄膜晶体管(Thin-film transistors,TFTs)器件就是该领域重要应用之一。TFTs作为核心驱动部件已广泛应用于平板显示器领域,同时在生物传感器、便携穿戴式电子器件、一次性电子产品等领域也具有极大的潜在应用前景。但是,TFTs 器件的电学性能不稳定性问题和低功耗问题已成为亟需解决的主要瓶颈问题。目前已有不少报道[1-4],其中采用电解质材料作为器件的栅介质层,利用其双电层效应,可大幅度降低工作电压,实现超低功耗。

双电层薄膜晶体管(EDL-TFTs)以电解质作为栅介质层,与传统绝缘栅介质材料不同的是,电解质栅介质层与有源层界面处在电场作用下形成纳米级厚度的双电层效应,相当于在界面处形成了一个超大的双电层电容。该双电层电容的单位面积电容可大于1 μF/cm2,从而使EDL-TFTs能在更低的电压下工作,极大地减少了器件能耗[5];另外,电解质材料大都可以在室温下制备,可更好地满足穿戴式柔性电子器件对低温制备的工艺要求[6-8]。基于上述特性,双电层薄膜晶体管在便携式传感器、印刷电子技术、柔性电子器件、神经形态工程等领域展现出较大的应用潜力[9-11]。

目前,以天然生物电解质材料作为栅介质层的EDL氧化物TFT有较多报道,主要集中在不同电解质与不同氧化物半导体之间的组合方式,制备的器件性能存在较大的差异。Liang 等以天然鸡蛋清作为栅介质层,采用磁控溅射法制备双电层薄膜晶体管,该器件工作电压低至1.5 V,开关电流比高达2.4×108[12]。Guo 等以鸡蛋蛋白为栅介质层在柔性纸基底成功制作出双电层(EDL)氧化物基薄膜晶体管,并展示了该器件在逻辑电路中的应用[13-14]。Zhu 等以鸡蛋清作为开关层制备了电阻随机存取存储器(RRAM),该器件具有可靠的存储性能[15]。Kim 等以鸡蛋白为栅介质制备了纸基非易失性存储器薄膜晶体管,该器件高开关电流比约为1.1×106,饱和迁移率为11.5 cm2/(V·s),器件在分层和弯曲状态下其特性也没有明显退化[16]。Jeon 等以鸡蛋白为栅介质制备了纸基氧化物薄膜晶体管,该器件沟道迁移率和亚阈值斜率分别为6.48 cm2/(V·s)和1.28 V/s[17]。此外,采用海藻酸钠、蜂蜡、壳聚糖以及葡聚糖等天然生物可降解材料制备薄膜晶体管器件应用于脑启发神经形态、湿度传感领域、突触仿生等技术领域也有相关报道[18-22]。然而,关于双电层薄膜晶体管稳定性的研究报道极少。本文采用射频磁控溅射法在以天然鸡蛋清作为栅介质层上沉积氧化锌薄膜形成有源层,制备出低栅顶接触型双电层氧化锌薄膜晶体管,并对其电特性进行了表征,研究了该ZnO-TFT在栅、漏偏压应力作用下电特性的稳定性及其物理机制。

2 实 验

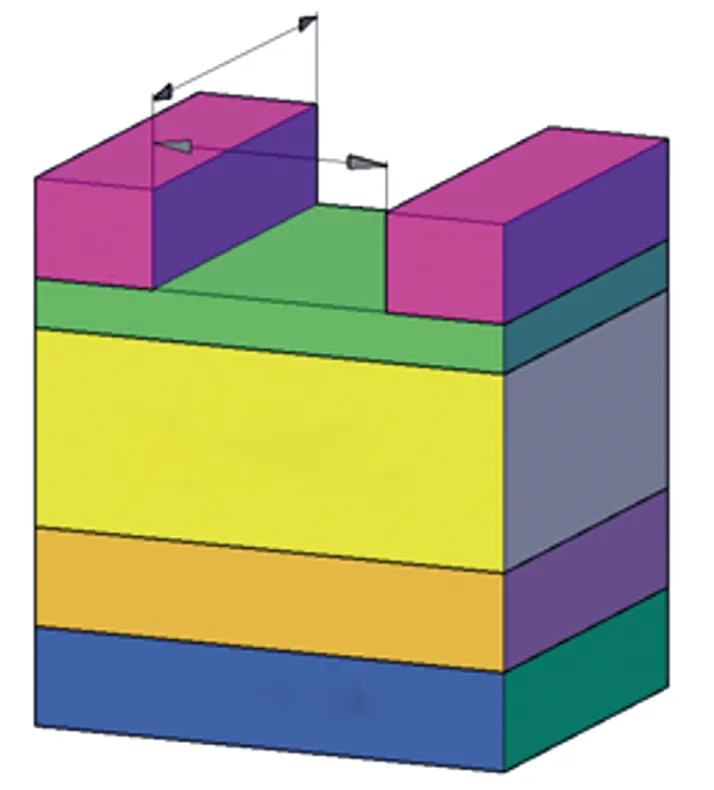

双电层氧化锌基薄膜晶体管实验样品采用氧化铟锡(ITO)导电玻璃作为衬底和栅(G)电极,样品的主要制备工艺步骤如下:首先依次使用无水丙酮、无水酒精、高纯水对ITO玻璃基片进行超声清洗;接着采用旋涂工艺在ITO玻璃基片上均匀旋涂一层天然鸡蛋清薄膜,并放置于真空干燥箱中使鸡蛋清从液态变成固态电解质;随后采用射频磁控溅射(RF)法在鸡蛋清栅介质层上沉积氧化锌薄膜有源层,RF功率设置为100 W,Ar与O2的流量比调控为30∶30(mL/min);最后利用掩膜版采用真空镀膜技术蒸发Al形成漏(D)极和源(S)极,最终制得底栅顶接触型氧化锌基薄膜晶体管。该器件的结构示意图如图1所示,样品的沟道长度(L)与宽度(W)由所用掩膜版图形来确定,分别是80 μm和400 μm。

图1 ZnO-TFT 器件结构图

鸡蛋清栅介质层厚度由台阶仪测得,约为850 nm;有源层氧化锌薄膜的厚度利用德国Ocean Optics公司的光反射薄膜测厚仪进行测量,其值为100 nm;单位面积栅介质电容(Cox)采用Agilent 4284A电容分析仪测得;ZnO-TFT 器件的电特性使用Agilent 4156C 半导体参数分析仪及CASCADE RF-1探针台组成的测试系统进行测试[23]。

3 结果与讨论

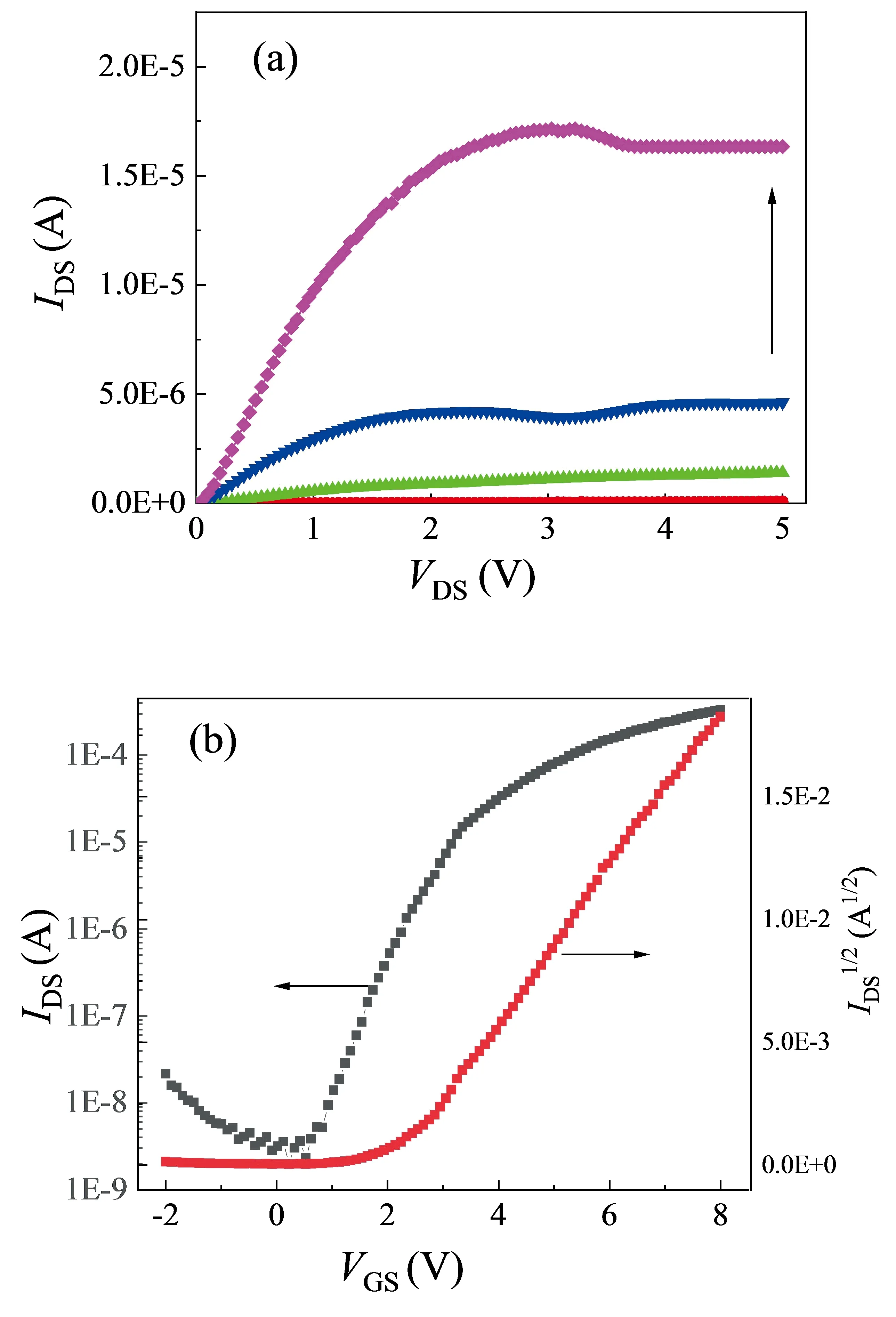

图2 给出了该ZnO-TFT 器件典型的输出特性和转移特性曲线。如图2(a)所示,器件在源漏电压(VDS)处于0 V附近时漏极电流(IDS)不存在拥堵现象,表明ZnO有源层和Al源漏电极之间具有良好的欧姆接触特性。当该器件和VGS均为 2 V左右时达到饱和状态,此时饱和漏电流达到15 μA,表明该器件可以在较低电压下达到较大的驱动电流。这是由于该ZnO-TFT 器件的栅介质层(天然鸡蛋清)中含有可自由移动的H+,当在ZnO-TFT 器件上加上栅源电压时形成电场,H+在其作用下向有源层和栅介质层的接触面移动并在栅介质层表面处集聚形成正电荷层;同时有源层中的电子被H+形成的正电荷层吸引,在ZnO-TFT 器件的栅介质层及有源层的界面处感应形成了H+层和电子层,即两界面处形成双电层(EDL);该双电层仅纳米级厚度,其电容非常大,所以可以使器件在比较小的电压下产生较大的电流,即可以有效地减小器件的工作电压。

薄膜晶体管器件工作于饱和区时源漏之间的饱和电流ID,sat通常可表示为

(1)

图2 EDL ZnO-TFT的电特性。(a)输出特性曲线;(b)转移特性曲线。

(2)

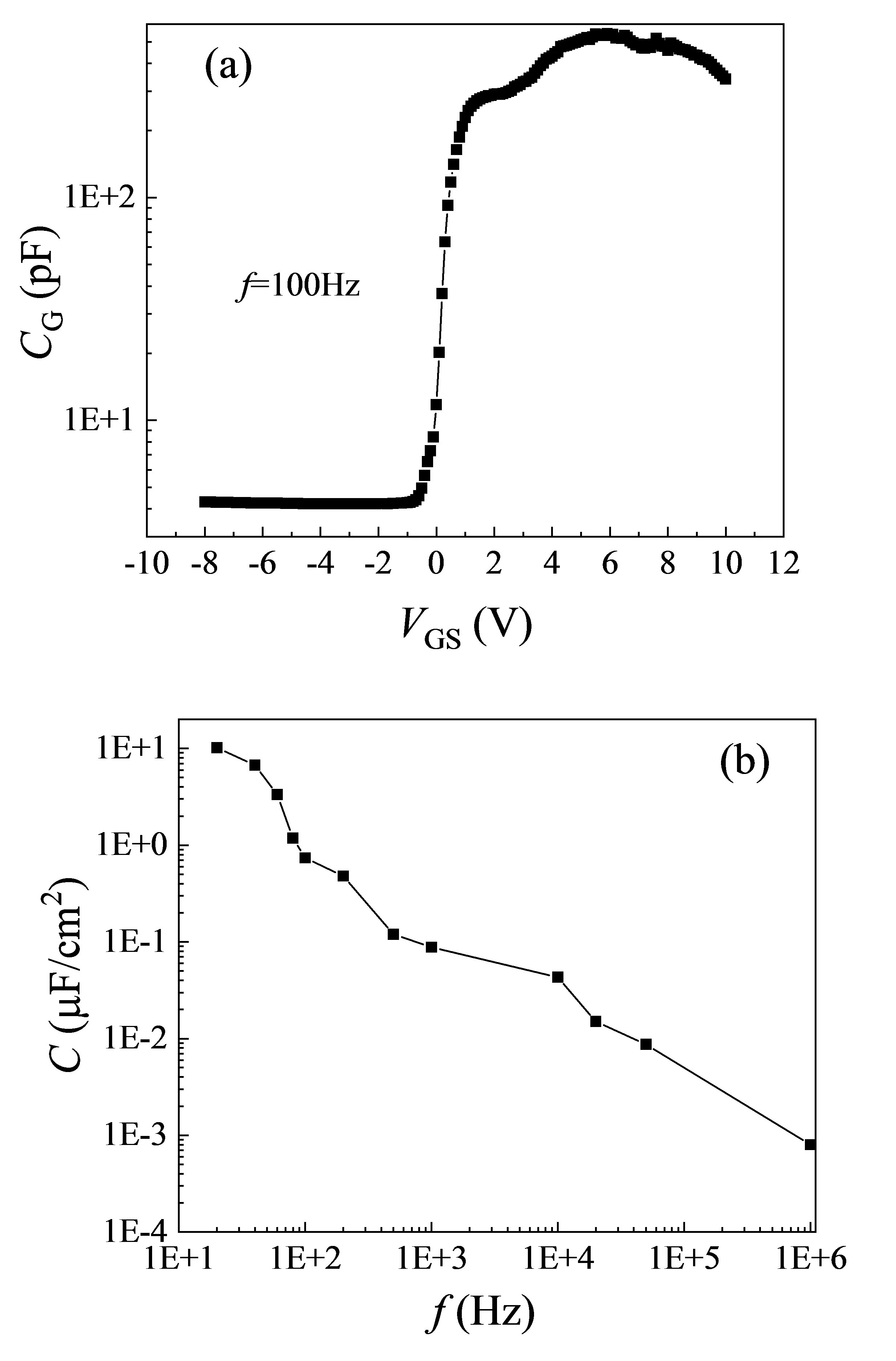

图3 给出了实验中双电层ZnO-TFT器件的电容-电压(C-V)和电容-频率(C-f)特性曲线。由图3(a)看出,当器件处于正栅压时,该器件的电容值迅速增加了近3个数量级;而普通栅介质形成的电容器件,其变化率只会小幅度同数量级的变化。表明所制备的ZnO-TFT器件施加正栅压时,由于形成了双电层,使器件的电容大幅度的增加。由图3(b)的C-f关系可知,在低频区附近(>100 Hz)电容随着频率的增加迅速减小,这与常规氧化物栅介质器件特性明显不同,对于常规栅介质,通常低频区电容随频率基本不变。样品的C-f特性表明EDL-TFTs器件在较低的工作频率下工作才可以实现低功耗特性,这是因为器件栅介质层中的可移动H+离子只有在较低的频率下响应外加电场的变化,从而呈现出双电层电容特性;在高频电场条件下H+离子的移动跟不上频率的变化,因此鸡蛋清栅介质层就失去了双电层电容特性,与传统介电层的电容特性相当。

图3 EDL ZnO-TFT的C-V特性曲线(a)和C-f特性曲线(b)

3.1 栅偏压应力稳定性

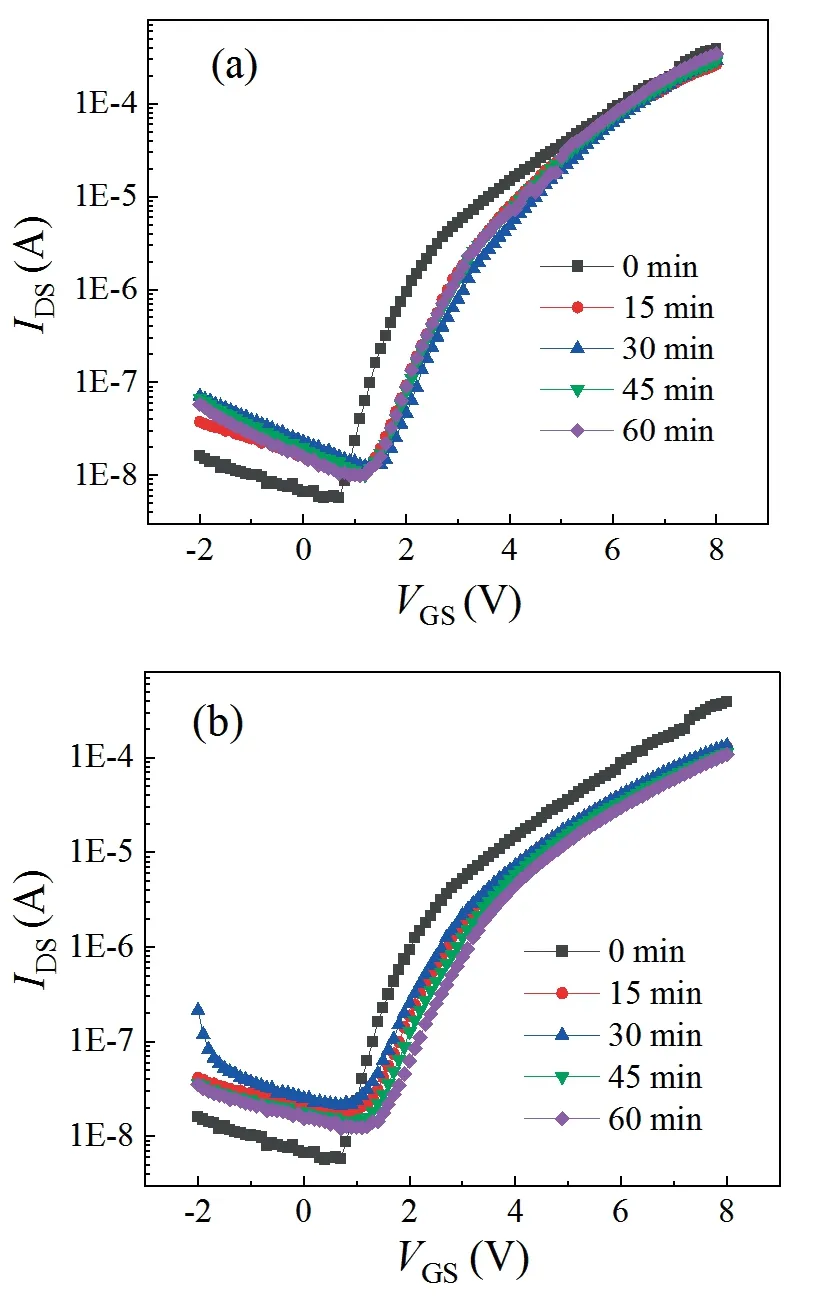

图4 给出了ZnO-TFT在源漏偏压VDS为0 V、栅偏压应力VGS分别为2 V和6 V时不同应力时间后的转移特性曲线。由图4 可以看到,在不同的栅偏压应力作用下,转移特性存在不同程度的变化,说明其电特性存在栅偏压应力不稳定性,且6 V的栅偏压应力要比2 V栅偏压应力的影响要大。

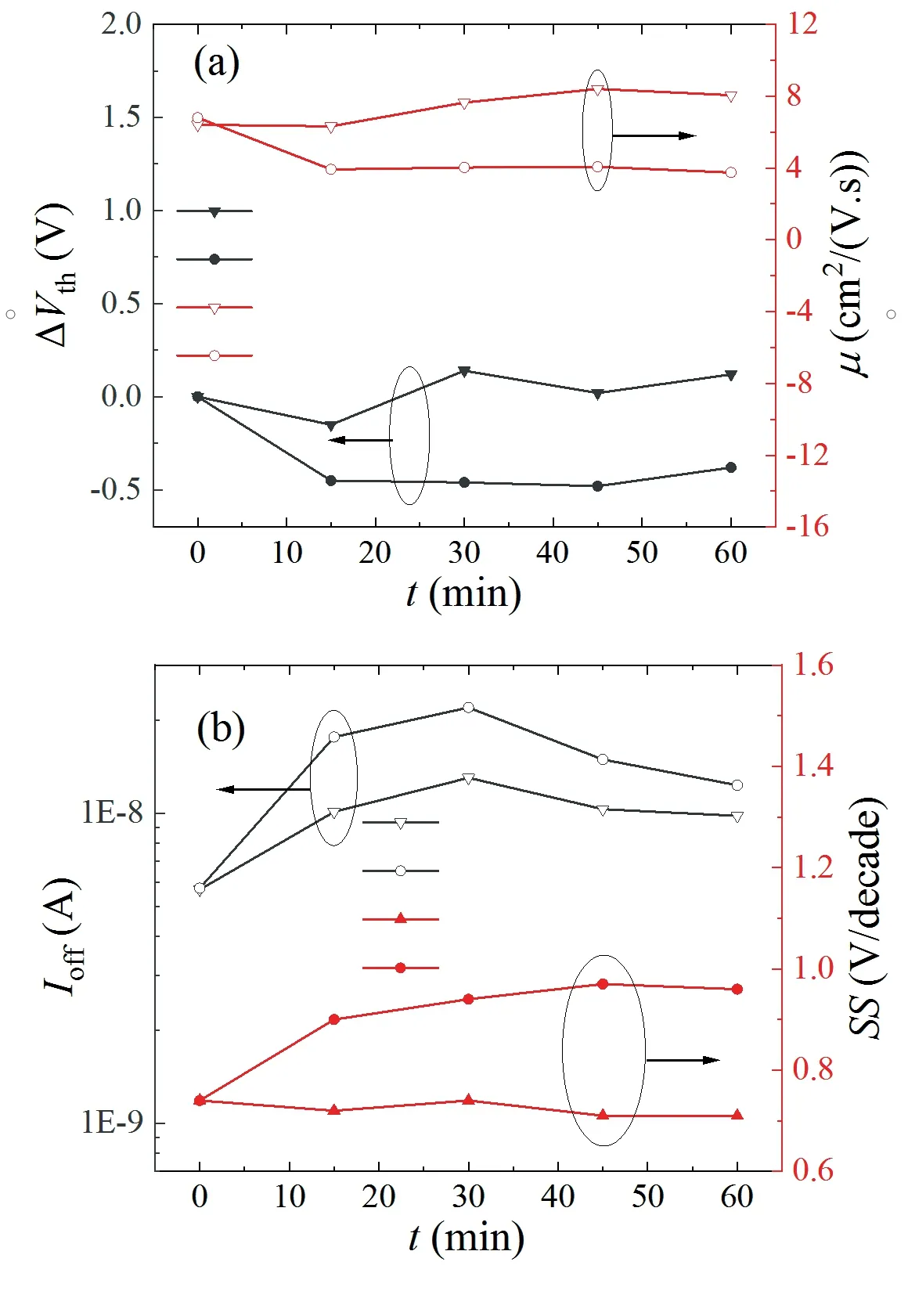

为了进一步分析栅偏压应力与电性能的依赖关系,从图4中提取出不同应力时间下的电性能参数。图5给出了器件在偏压应力VGS分别为2 V和6 V下阈值电压偏移量(ΔVth)、场效应迁移率(μ)、关态电流(Ioff)、亚阈值摆幅(SS)随应力时间的变化曲线。

图4 不同栅偏压应力下ZnO-TFT 转移特性随应力时间变化曲线。(a)VGS=2 V;(b)VGS=6 V。

由图5可观察到,对于VGS=2 V的正栅压应力,器件的ΔVth、μ和SS随应力时间的增加保持相对稳定,变化较小。其中Vth存在少量波动,μ随应力时间的增加有少许增加,SS保持较好的稳定性。这是因为VGS=2 V的栅偏压应力小于初始阈值电压,此时半导体表面导电沟道层可动电荷(沟道自由电子)还极为稀少,栅应力电压感应的电子大都被沟道中缺陷态所俘获。另外,当栅偏压应力较小时,栅介质中电场和半导体表面电场都相对较弱,不足以引起栅介质体内和界面产生新的缺陷态。对于VGS=6 V的正栅偏压应力,随着应力时间的增加,Vth先快速减小而后趋于稳定(即向负栅偏压方向漂移),这可解释为电解质中的正电荷(如Na+)在栅应力形成的电场作用下向栅界面处靠近所致;μ亦先快速减小而后趋于稳定,15 min 应力减小了近1倍,这说明在较大的栅偏压应力作用下器件的迁移率发生明显的退化;而SS则表现为不断增大的趋势,这说明在栅偏压应力作用下器件沟道区及界面处产生了少量的新缺陷态[24]。无论是VGS=2 V还是VGS=6 V的栅应力下,随应力时间增加,Ioff皆表现先明显增大而后又有所恢复。这可能是双电层等效于超级电容器,短时应力作用时相对于电容充电,应力结束转移曲线测试时产生放电效应,故导致Ioff增加;应力作用一定时间(30 min)后,以放电效应为主,所以Ioff又有所减小。栅偏压应力越大,充电电荷越多,Ioff增加也就越大。

图5 不同栅偏压应力下ZnO-TFT的电学参数随应力时间变化曲线。(a)ΔVth 和μ随t的变化曲线;(b)Ioff 和SS随t的变化曲线。

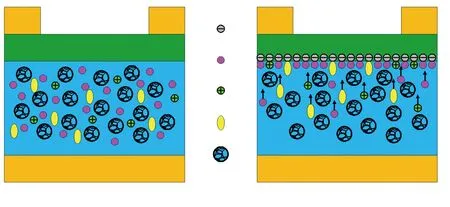

基于以上分析,器件的正栅偏压应力引起的电性能不稳定性的物理机制可由图6 示意给出,无栅应力时,蛋清电解质中质子(H+)、带负电的大分子、杂质离子(如Na+、K+等)随机分布在栅介质层中(如图6(a));当器件施加正栅偏压应力作用时,由于应力时源漏电极短接,应力作用产生一个由栅极指向沟道界面的垂直电场,这个电场将鸡蛋清电解质中的H+推向栅介质界面处,同时蛋清中的Na+、K+等正电荷离子也会在栅介质与有源层界面处聚集,甚至进入沟道中引起掺杂效应,如图6(b)所示。正电荷从电解质体内向界面聚集导致阈值电压向负栅压方向移动,而界面处缺陷增加导致亚阈值摆幅增大;其次,界面处因H+引起的双电层效应,在界面处沟道中产生大量电子积累,部分沟道载流子(电子)被栅介质层或栅介质层和有源层的界面陷阱态所俘获成为电荷中心[25-26],从而对沟道中载流子的输运起散射作用,导致载流子迁移率降低;另外,在栅偏压应力下,尤其是栅偏压较大的情况,沟道电子在电场作用下会注入到栅介质体内,在这个过程中可能对栅介质层内部及界面处弱键产生破坏,导致新缺陷态形成,从而引起迁移率减小。因此,正栅偏压应力作用下,器件电性能的变化主要是栅介质附近及界面处的正电荷聚集、充放电效应及新陷阱态产生的复合效应。

图6 ZnO-TFT 栅偏压应力工作原理图。(a)无栅偏压应力;(b)有正栅偏压应力。

3.2 漏偏压应力稳定性

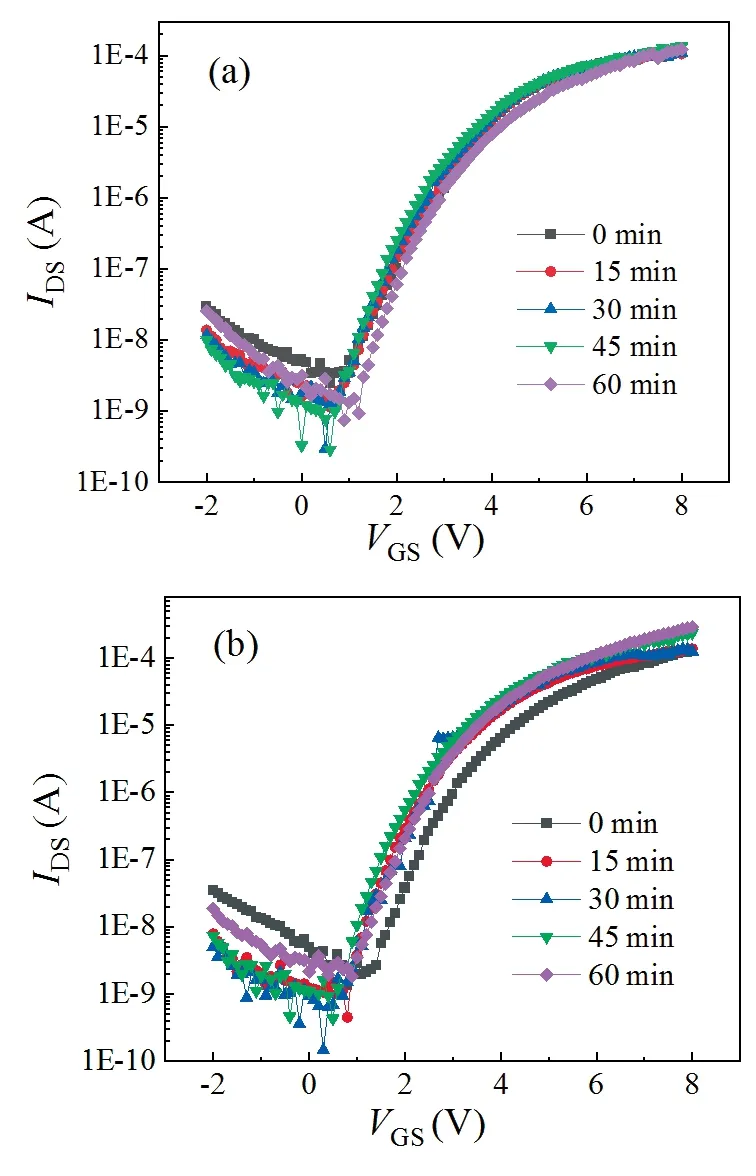

图7 给出了器件在VGS为0 V、VDS分别为2 V和6 V的偏压应力下不同应力时间的转移特性曲线。由图7 可以发现,随着应力时间的增加,转移特性曲线并没有出现单一方向的漂移,而是呈现一定的来回波动,漏偏压应力越大波动的范围也增大。对于VDS=2 V的漏偏压应力,随应力时间的增加,转移曲线先左漂移而后向右漂移,且在60 min应力时间后转移曲线位于初始曲线的右侧;而对于VDS=6 V的漏偏压应力,随应力时间的增加,转移曲线先左漂移而后向右漂移,但在60 min应力时间后转移曲线仍位于初始曲线的左侧。

为了更清晰地揭示漏偏压应力作用对器件电性能的影响,从图7可以提取出该EDL ZnO-TFT器件的电性能参数。图8给出了在VDS分别为 2 V和6 V的偏压应力作用下不同应力时间的电参数ΔVth、μ、Ioff和SS随应力时间的变化曲线。

图7 不同漏偏压应力下ZnO-TFT 转移特性随应力时间变化。(a)VDS=2 V;(b)VDS=6 V。

由图8(a) 可以看出,对器件施加漏偏压应力时,随着应力时间的增加Vth先减小而后再增加,且相比于VDS=2 V时的漏偏压应力,VDS=6 V时的漏偏压应力引起Vth的变化量增大;在较小的漏偏压应力(VDS=2 V)下,器件的μ随应力时间的增加没有明显的变化,而对于较大的漏偏压应力(VDS=6 V)时,μ随着应力时间的增加而增大,60 min应力时间后μ增加近2倍;从图8(b)可以看出,在不同的漏偏压应力作用下,Ioff随应力时间的增加先有少许减小,45 min后又有所增加;SS随应力时间的增加略有减小,但并没有随漏偏压应力的增加而增加。

图8 不同漏偏压应力下ZnO-TFT的电学参数随应力时间变化曲线。(a)ΔVth 和μ随t的变化曲线;(b)Ioff 和SS随t的变化曲线。

器件在漏偏压应力下引起的电参数的不稳定性可作如下解释:当器件施加漏偏压应力作用时,由于此时栅源短接(VGS=0 V),因此应力作用时器件内部会诱导两个电场,一个是沟道层的漏极端指向源极端的横向电场,另一个是沟道有源层指向栅极的垂直电场。横向电场使电子从源端注入沟道,并在沟道电场作用下向漏端迁移形成沟道电流,可导致有源层ZnO中因焦耳热而产生新的氧空位,从而使沟道中的电子浓度增加[27];另一方面,源端注入的电子也可能会被沟道中的陷阱态所捕获,产生充放电效应。垂直电场将鸡蛋清电解质中的H+、Na+和K+等可动正电荷推向栅极一侧,且其中的Na+和K+等正电荷在应力释放后的测试期间来不及恢复初始状态,从而削弱了对器件的不利影响。基于以上分析,可以认为在漏偏压应力作用下器件的Vth的不稳定性主要来源于沟道内陷阱态对电子的捕获效应,在撤消应力测试时沟道中被陷阱的电子来不及释放,因此相当于沟道中的有效陷阱态减小,对栅压感应的沟道电子陷阱作用减弱,即阈值电压减小。但随着应力时间的增长,由于栅电极与源电极接地,漏偏压在栅介质层产生由沟道指向栅极的垂直电场,该电场可将电解质中的负电荷(Cl-、带负电的蛋白等)驱赶至界面附近,故导致阈值向右漂移(ΔVth减小)。对于较大的漏偏压应力(VDS=6 V),随着应力时间的延长,沟道电流形成的焦耳热增多,使器件温度上升,因而产生新的氧空位越为明显,氧空位释放电子引起沟道中电子浓度增大,从而导致迁移率随应力时间增加而有所增大,因此引起器件的开态电流增加。

4 结 论

本文采用射频磁控溅射法,以天然鸡蛋清作为栅介质层,以氧化锌作为有源层,制备得到EDL ZnO-TFT,研究了ZnO-TFT在栅、漏偏压应力下电性能的稳定性。该ZnO-TFT器件呈现出良好的电学性能,载流子饱和迁移率为5.99 cm2/(V·s),阈值电压为2.18 V,亚阈值摆幅为0.57 V/dec,开关电流比约为1.2×105,工作电压低于3 V。由于采用了天然鸡蛋清电解质作为器件的栅介质层,在沟道与栅介质界面处形成双电层效应,从而有效降低了器件的工作电压。通过对EDL ZnO-TFT器件在偏压应力效应的测试与分析,发现该器件存在一定的偏压应力不稳定性。其中,较大的栅偏压应力作用下主要表现为阈值电压向负栅压方向移动,迁移率有所减小,亚阈值摆幅增大,关态电流先增加后减小;较大的漏偏压应力作用下表现为迁移率增加,关态电流减小,阈值电压向负栅压移动。

本文专家审稿意见及作者回复内容的下载地址:http://cjl.lightpublishing.cn/thesisDetails#10.37188/CJL.20210324.