功率管高频驱动回路参数优化研究

谢佳明,金建辉,谢鹤龄,杨 宽,李盛洪

(昆明理工大学信息工程与自动化学院,云南 昆明 650500)

0 引言

对于功率电路而言,提高工作频率有利于提高效率、减小电路体积,因此高频一直是功率电路的发展方向。目前,提高频率的方法主要有两种。一是从功率管着手,通过更新迭代新技术、新材料的应用缩小其输入电容大小,例如最新绝缘栅双极型晶体管(insulated gate bipolar transistor,IGBT)芯片以厚铜替代铝材,并且在第五代产品基础上改进沟槽栅结构,输入电容较前代产品从十几纳法到现在的几纳法甚至更小,且具有更强的耐压能力、应力承受能力。二是从驱动电路着手,设计具备反馈检测、保护电路等驱动功率增强的电路,提升工作频率及其可靠性[1]。2019年,徐俊设计一种IGBT闭环驱动芯片,通过分阶段控制IGBT开关过程,在保证IGBT电流、电压过冲安全的情况下,以最大的电流驱动IGBT,负载接10 nF电容测试下,输出驱动电流约为±2.5 A,实现驱动频率约为50 kHz[2]。2019年,许东升利用半桥驱动方式,在负载接1 nF电容测试下,驱动电流峰值为2.8 A,实现驱动频率为500 kHz[3]。

本文基于功率管有源等效模型,对功率管驱动回路参数进行理想化建模、分析和仿真。从理论上分析了驱动回路参数值对功率管高频工作的影响,提出一种在不改变功率管及驱动电压的情况下,通过优化驱动回路参数和提升驱动电路性能(即优化驱动电路拓扑)大幅提升驱动电路输出电流、减小驱动电路延时和加固驱动电路电磁兼容(eletromagnetic compatibility,EMC)的设计。该设计可有效提高功率管工作频率及其可靠性。通过仿真和自主设计的驱动电路驱动IGBT管的实测,证明这些综合措施有一定效果。本文以Infineon中FS75R12KT3模块为例,通过PLECS软件仿真,验证了优化后的驱动回路参数可有效提高IGBT管开关频率,且可靠性显著增强。

1 IGBT有源等效驱动回路模型

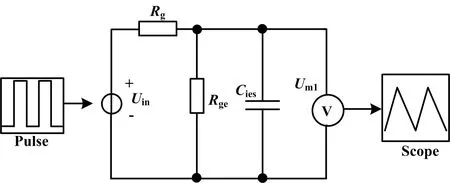

IGBT有源等效驱动回路如图1所示。

图1 IGBT有源等效驱动回路Fig.1 IGBT active equivalent drive loop

图1中:Rg为串联栅极电阻;L1为栅极引线等效电感;Rge为并联栅射电阻;Lg、Lc、Le分别为栅极、集电极、发射极寄生电感;Cge、Cgc、Cce分别为栅射、栅集、集射寄生电容[4],Cgc随外加电压变化;Rgin为内部栅极电阻,集射可等效为一个压控电流源;Uin为驱动信号。

输入电容Cies为:

Cies=Cge+Cgc

(1)

驱动回路中除电阻Rg、Rge及电容Cies,其余皆为寄生参数,在IGBT选型及走线后无法改变。Rg控制IGBT开关速度及消振。栅射氧化膜耐压差,Rge的作用是避免氧化膜被静电击穿[5-6]。通常取Rg为10 Ω,Rge为10 kΩ(下文将此二值称为传统参数)。Cies电压决定IGBT的开关状态,即IGBT的开关是驱动电流对Cies充放电。开通过程中,当Cies上电压充至IGBT门槛电压时,IGBT微导通。此时,导通损耗大、管压降大。通常,在Cies上电压充至12 V时,认为其处于完全导通状态。此时,管压降最低、损耗最小。不考虑寄生参数时,驱动回路中影响工作频率的主要有Rg、Rge和Cies。因此,可将驱动回路模型进一步理想化。下文对驱动回路理想化模型进行分析。

2 理想驱动回路模型分析

2.1 理想开通回路模型分析

基于上述分析,驱动回路的理想开通回路模型如图2所示。图2中:Uc为Cies电压;Uin为驱动电路输出的驱动电压;Ig为驱动电路输出的驱动电流;Ige、Ic分别为流经Rge、Cies的电流;SW为开关。SW闭合时,模拟Ic对Cies充电直至12 V,开通过程完成。

图2 理想开通回路模型Fig.2 Ideal open loop model

设Cies初始状态为0。当SW闭合后,根据拉氏变换对Cies进行暂态分析,再反变换转换为时域Ig(t)。其式为:

(2)

Uc(t)为:

(3)

Cies取模块FS75R12KT3的输入电容5.3 nF。当IGBT开关频率达1 MHz时,半个周期为500 ns。保留充足的死区时间,设为100 ns,有效高电平脉宽为150~200 ns,剩余脉冲上升、下降沿时间为200~250 ns。由于分析的是理想回路模型,不考虑实际存在的寄生参数,为保留充足余量,开通波形上升沿时间t取50 ns较为理想[7-8]。如果t取值大于50 ns,则会造成实际电路开通不可靠,使得频率达不到1 MHz[9-10]。因此,下述皆按照50 ns为上升沿时间进行分析。

当Uin=12 V、Rge=10 kΩ、Cies=5.3 nF,根据式(2)得到不同Rg值对应的、0时刻的Ig值,根据式(3)得到t=50 ns时刻的Uc值。Rg和Ig、Uc的对应关系如表1所示。

表1 Rg和Ig、Uc的对应关系Tab.1 Correspondence between Rg and Ig、Uc

由表1可知,Rg的减小有利于电容快速充电,所以对驱动回路参数进行优化,Rg取值为0.5 Ω,Rge取值为8 Ω(下文将此二值称为优化参数)。同时也可看出,Rg的减小使Ig增大。当Rg=0.5 Ω时,初始电流Ig=24.0 A。这对驱动电路输出初始驱动电流提出了更高的要求。而在如此高频且大电流输出的情况下,现有的驱动电路中的寄生参数会引发振荡、延时、EMC问题,使驱动电路不稳定且无法使IGBT管工作在1 MHz。

当Uin=12 V、t=50 ns时,可根据式(3)得出传统参数下不同Cies对应的电压Uc1,以及优化参数下对应的电压Uc2。不同Cies对应的电压如表2所示。

表2 不同Cies对应的电压Tab.2 Voltages corresponding to different Cies

由表2可知,Cies的减小有利于电容快速充至驱动电压,所以减小Cies一直是IGBT提高频率的发展方向。此外,在驱动电路相同及Cies大小相同的情况下,优化参数较传统参数更有利于IGBT的快速、完全开通。

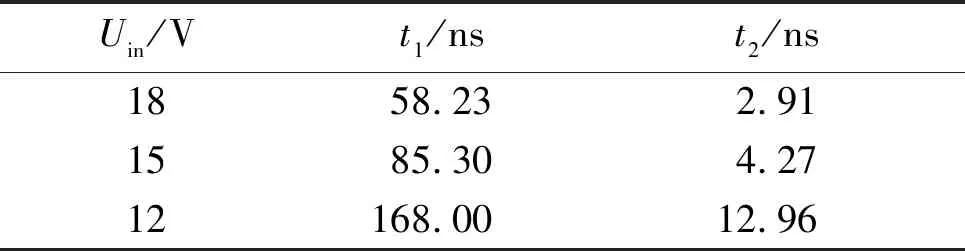

当Uc=11.9 V,t=50 ns、Cies=5.3 nF时,根据式(3)计算传统参数及优化参数下,不同Uin对应所耗时间,分别为t1、t2。不同Uin对应的耗时如表3所示。

表3 不同Uin对应的耗时Tab.3 Time consumption corresponding to different Uin

由表3可知,传统参数下增大Uin有利于Cies快速充至驱动电压,但改善不显著。综合分析可知,在Cies及Uin一定的情况下,唯有优化驱动回路参数才能使Cies快速充至12 V。

2.2 理想关断回路模型

与开通过程相反,IGBT关断过程的实质是驱动电流对Cies进行放电。理想关断回路模型如图3所示。

图3 理想关断回路模型Fig.3 Ideal turn-off loop model

图3中:I′g为驱动电路输出的泄放电流;I′ge、I′c分别为流经Rge、Cies的电流;U′c为Cies两端电压;U′in为驱动电路输出的关断电压。当SW闭合时,U′c放电至约为0 V,关断过程完成。

初始值U′c=12 V、Cies=5.3 nF时,当U′c放电至0.1 V,传统参数下不同U′in所耗时间为t′1、优化参数下所耗时间为t′2。不同U′in对应的耗时如表4所示。

表4 不同U′in对应的耗时Tab.4 Time consumption corresponding to different U′in

由表4可知,在驱动回路参数不变的情况下,U′in为负值可加快电容放电;在U′in不变的情况下,优化参数较传统参数可明显加快电容放电速度。

2.3 驱动回路中传统参数与优化参数对比分析

鉴于上述数据对比分析,可得出以下结果。

①在驱动电路确定的情况下,提升IGBT工作频率有提高驱动电压、减小输入电容及优化驱动回路参数3种方法。驱动电压受限于栅射氧化膜耐压值,所以提高幅度有限。输入电容与IGBT材料、加工及选型有关,而我国IGBT的生产、创新较为落后,所以在IGBT选型确定后,优化驱动回路参数可有效提高工作频率,即减小Rg、Rge的阻值。表1~表4的数据表明,此法更为实用、有效。

②通过参数优化后的驱动电路,对驱动电路输出的初始瞬态电流能力提出了更高的需求;同时,在高频、大功率负载情况下,由于EMC、分布参数、寄生参数的影响,对驱动电路的稳定性也提出了更高的需求。对此,需要对驱动电路拓扑进行优化,例如将传统的全桥或半桥驱动拓扑结构换成不对称式图腾柱结构,以增强瞬态驱动电流;选用功率大、延时小、额定电流大的三极管作为驱动管;通过印刷电路板(printed circuit board,PCB)多层板布局,将信号回路面积最小化,完善EMC、信号完整性(signal integrity,SI)及电源完整性(power integrity,PI),以增强驱动电路及驱动回路的整体抗干扰能力。

3 驱动回路的仿真及实测分析

3.1 理想驱动回路仿真分析

使用电力电子领域较为专业的PLECS软件进行仿真。理想驱动回路Uc仿真电路如图4所示。

图4 理想驱动回路Uc仿真电路Fig.4 Simulation circuit of ideal drive circuit Uc

图4中:Pulse与Uin组成一个频率为1 MHz、高电平为12 V、低电平为0 V或-5 V、占空比为50%的方波发生器,用于模拟驱动电路输出的驱动波形。器件Um1与Scope组成一个测量Cies两端电压(即Uc)的示波器。当方波发生器为高电平时,即开通过程,其对Cies的充电原理如图2所示。当方波发生器为低电平时,即关断过程,其对Cies的放电原理如图3所示。

3.2 仿真结果

当方波发生器以高电平/低电平对Cies作充/放电时,理想驱动回路开通和关断时的Uc波形如图5所示。当方波发生器为12 V时,传统参数及优化参数开通过程Uc对比波形如图5(a)所示,可见相较传统参数,优化参数后Uc几乎垂直上升,即优化参数比传统参数更有助于IGBT管快速开通,与表1数据所得结论相符。当方波发生器为低电平对Cies放电时,示波器波形如图5(b)所示,可见驱动电路输出-5 V时与0 V时相比,Cies放电更快,即IGBT管关断更快。图5(c)是低电平为-5 V时传统参数及优化参数波形对比,可见优化参数中Cies放电速度快于传统参数,即优化参数较传统参数更利于IGBT管关断,与表4数据所得结论相符。

图5 理想驱动回路开通和关断时的Uc波形Fig.5 Uc waveforms when ideal drive circuit on and off

3.3 实际参数等效栅射端电压仿真分析

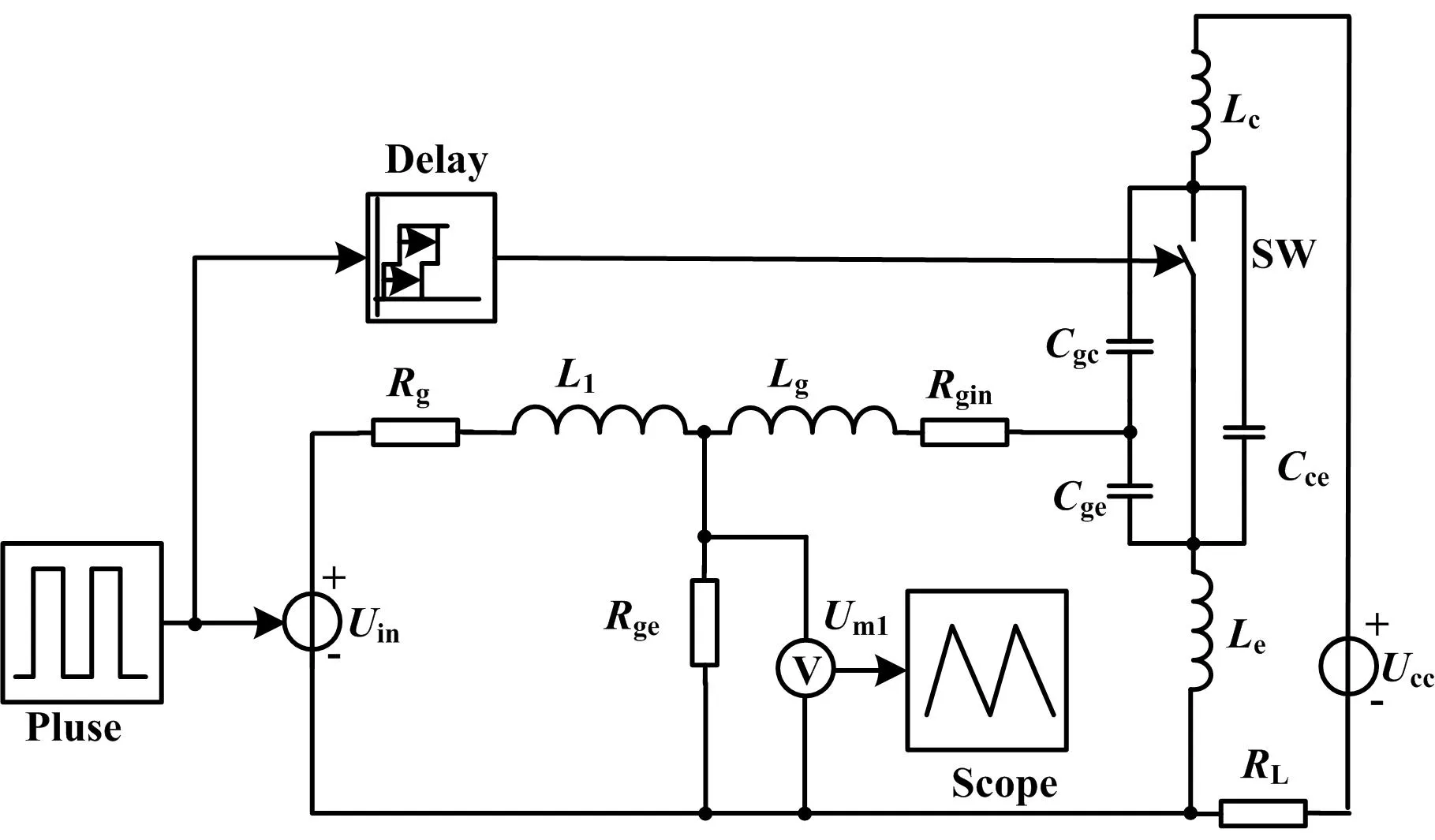

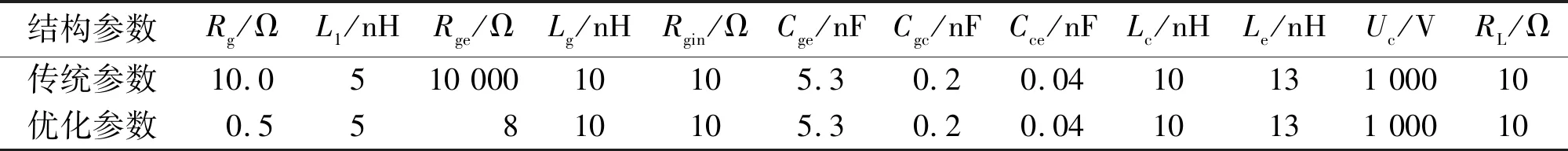

实际驱动回路GE端电压仿真电路如图6所示。

图6 实际驱动回路GE端电压仿真电路Fig.6 Simulation circuit at GE end of actual dive circuit

图6中,器件Pulse与Uin组成频率为1 MHz、高电平为12 V、低电平为0 V、占空比为50%的方波发生器。电压表与Scope组成测量GE端电压的示波器。开关SW延时于方波发生器高电平50 ns后闭合,RL为负载电阻。当方波发生器为高电平,对Cies充电50 ns后,SW闭合,以模拟IGBT导通负载工作。

电路各仿真参数取自Infineon的FS75R12KT3模块。实际电路中各参数如表5所示。表5中:L1、Lg、Rgin、Lc的取值为具有普适性的数值。

表5 实际电路中各参数Tab.5 Parameters in the actual circuit

3.4 仿真结果及实测

实际驱动回路开通和关断时GE端电压波形如图7所示。

图7 实际驱动回路开通和关断时GE端电压波形Fig.7 GE end voltage waveforms when the actual drive loop switch on and off

图7(a)为方波发生器为高电平时的开通过程。对比传统参数及优化参数曲线可明显看出,相较传统参数,优化参数能更快地使GE端电压达12 V,即IGBT管开通更快。图7(b)为方波发生器为低电平时的传统参数下关断过程,可见GE端电压振动显著且振幅大。图7(c)为优化参数下关断过程,可见GE端振荡变小且振幅小。对比图7(b)和图7(c)可知,相较传统参数,优化参数可使GE端关断电压波形振荡明显减少且振幅减小。这是因为优化参数中改用了小的Rge,使关断瞬间的干扰及位移电流能以更大I′ge进行泄放,从而最大程度地避免误开通及栅氧化层被击穿的可能性。

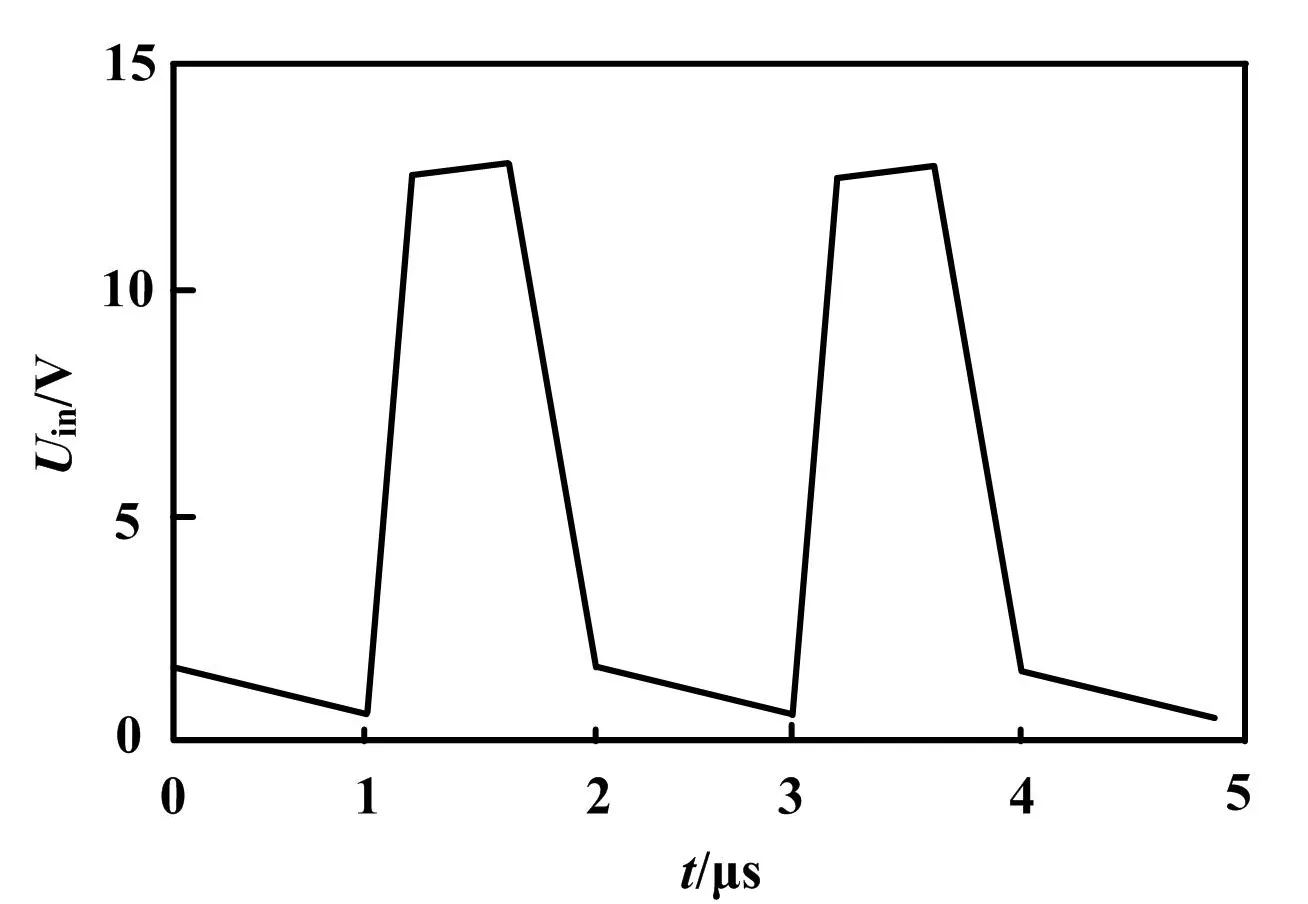

实测驱动波形如图8所示。实测中,自主设计驱动电路采用图腾柱驱动拓扑结构,对电源系统进行全面的电源完整性改善,且通过多层PCB布板完善驱动电路整体SI、EMC,采用优化驱动回路参数。功率管工作频率大于500 kHz时,驱动波形陡峭且振荡小。

图8 实测驱动波形Fig.8 Measured drive waveform

4 结论

本文从功率管等效开通和关断驱动回路模型方面,研究了影响功率管开通和关断的因素,提出了当等效输入电容一定时,在不提高驱动电压的情况下,要让功率电路在高频、大负载下稳定工作,相对经济、可靠、实用的方法为优化驱动回路参数和提升驱动电路性能。

仿真结果显示,该方法可以实现参数优化后驱动电流变大,驱动频率提升,同时有效地削弱了由母线电压传输导致的干扰、减小了驱动信号振荡,保护了驱动电路。

优化驱动回路参数时,必须先提升驱动电路性能指标,再提升功率管工作频率。其有效性已由电路仿真和实测予以验证。本文中的自主设计驱动电路,优化了驱动电路拓扑,大幅提升了驱动电路输出电流,减小了驱动电路延时,加固了驱动电路EMC设计。后续将对自主设计的驱动电路作进一步研究。