3D结构低相位噪声移频锁相源设计

张献武,吴佳佳

(中国电子科技集团公司 第十三研究所,河北 石家庄 050051)

0 引言

目前微波电子产品对小型化需求日益迫切,对其体积要求越来越严格。三维(3D)电路结构的出现使产品体积大大缩小,小型化改进得到较大幅度的提升。在3D电路结构中,上层基板和下层基板之间的互联工艺是实现电路性能的关键技术。本文提到的设计采用BGA植球工艺来实现上下基板互联,即利用锡球充当连接点,实现按电气性能的互联以及上层基板的固定支撑。对于微波系统中的本振频率源,为了提高整个系统信噪比,相位噪声要求越来越低,甚者接近理论相位噪声。

本文使用3D结构和同轴介质振荡器(CRO),用于低相位噪声移频锁相频率源的研制,体积缩小到原来改版前盒体的7.5%,在频偏1KHz处相位噪声只比理论倍频值差约4-7dB。

1 3D电路小型化设计

1.1 3D结构的互联

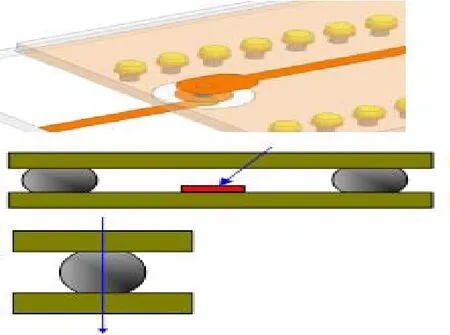

在3D电路结构中,上下层基板之间的互联工艺是实现电路性能的关键技术,本结构采用BGA植球工艺,即将焊锡球焊接在上下层基板之间来实现电气互联和上层基板的固定支撑[1]。本设计采用了两层结构如图1所示,基板采用多层陶瓷基板,可以更容易实现表贴器件与裸芯片混合布局,以及复杂布线。基板之间由于锡球直径的限制,对下层基板上的芯片和表贴器件高度有更高要求。底层基板主要为芯片和阻容器件,上层基板可以贴装塑封集成电路[2]。

图1 两层陶瓷基板互联

1.2 3D结构中微波信号传输方式

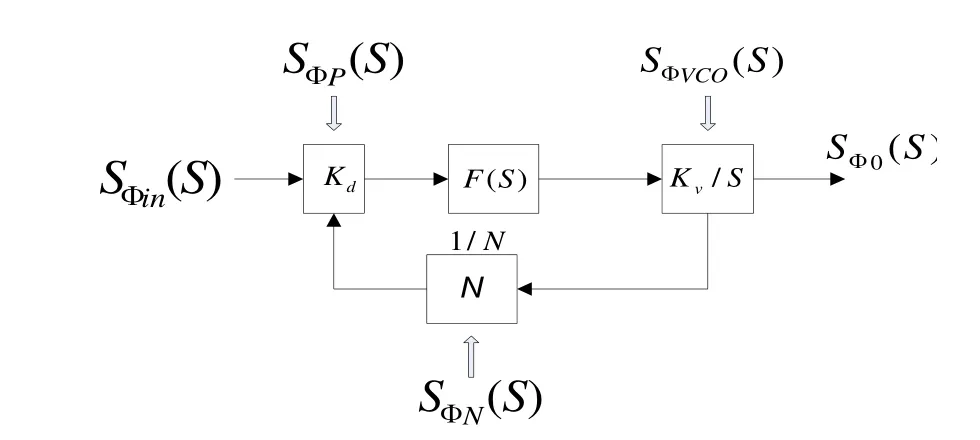

在3D电路结构中,微波信号的传输至关重要,其传输方式主要有三种:利用过孔的直通结构;微带线与锡球、上下层基板组成的类共面波导结构,如图2所示;利用上下基板互联锡球形成的类同轴结构。利用仿真软件进行优化设计后,仿真这三种信号传输模式的驻波系数都优于1.5,基本都满足使用要求。

图2 3D电路微波信号传输方式

图2从上到下依次为类直通结构,类共面波导结构,类同轴线结构。

1.3 3D结构基本电路设计

3D电路结构中,利用了锡球墙与基板之间形成的腔来进行隔离,如图3所示。梳谱与混频部分的IF信号通过锁相环控制CRO电调端电压形成相位负反馈,移频锁相环锁定。

图3 移频锁相环内部布局

2 移频锁相源相位噪声设计

2.1 理论基础及相位噪声设计

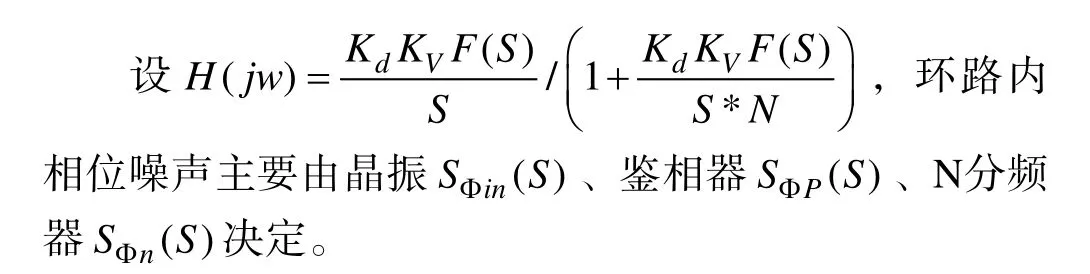

锁相环的原理相位模型如图4所示:

图4 锁相环的相位噪声模型

由输入晶振贡献的相位噪声为:

由鉴相器贡献的相位噪声为:

由N分频器贡献的相位噪声为:

而H(jw)与N分频比成反比,因此输入晶振、鉴相器、N分频器贡献的噪声都与N值成反比,因此在晶振输入相位噪声、鉴相器噪声、VCO指标确定的情况下,降低锁定频率jw和N值能提高环路带内相位噪声[3]。移频锁相源正是利用这种原理,可以先将VCO输出频率与另一个相位噪声较好的信号进行混频,中频反馈到鉴相器,可以降低输出频率jw,降低分频比N,满足相位噪声要求,移频锁相源实现的原理框图如图5所示。

图5 移频锁相环原理框图

锁相环输出频率理论相位噪声按倍频理论计算为20LOG(f/fin)。移频锁相环振荡器选用混合集成同轴介质振荡器CRO,相位噪声一般优于普通LC压控振荡器约20dBc/Hz,梳谱按理论20logN恶化,数字鉴相器选用ADF4002BCPZ,本底相位噪声为–222dBc/Hz,归一化50MHz相位噪声为–134.6dBc/Hz@10KHz,–142dBc/Hz@100KHz。

2.2 实物制作与测试结果

以某产品为例,输入参考频率为100MHz,相位噪声实测为–164.1dBc/Hz@10KHz,–170.3dBc/Hz@10KHz,输出信号为2950MHz,CRO频率输出2935-2965MHz,相位噪声达到–105dBc/Hz@10KHz,–125dBc/Hz@100KHz;梳谱输出2900MHz,相位噪声理论恶化 20LOG(f/fin)=20*LOG(2900/100)=29.3dB,梳谱相位噪声为–134.8dBc/Hz@1KHz,–141.0dBc/Hz@10KHz;锁相环鉴相频率为50MHz,环路带宽约350KHz,锁定后带内输出2950MHz相位噪声主要由鉴相器与梳谱混频得到,理论计算为–131.6dBc/Hz@1KHz,–138.5dBc/Hz@10KHz。

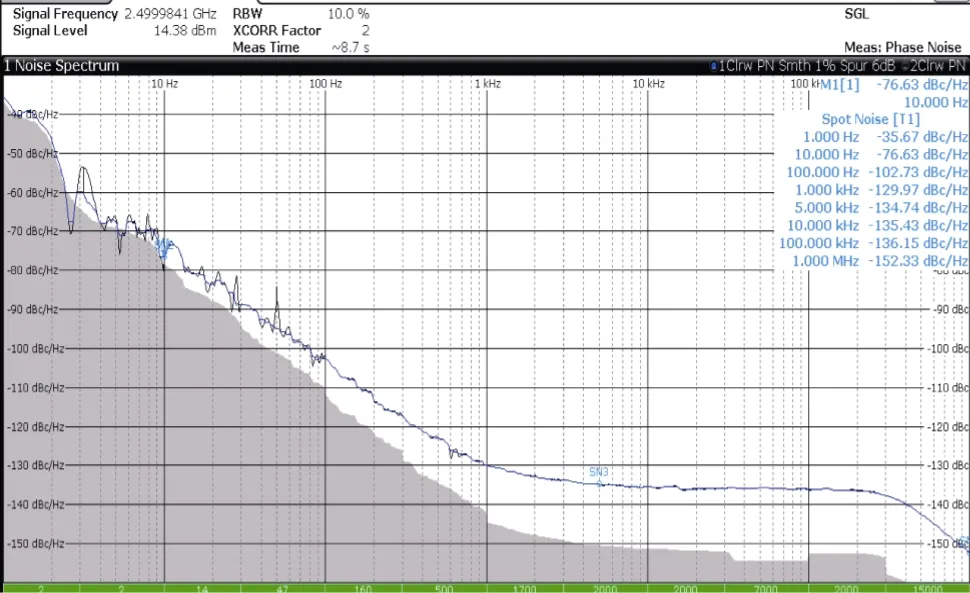

最终产品测试结果如图6所示,相位噪声达到–130.8dBc/ Hz@1KHz,–135.5dBc/Hz@10KHz,比输出频率20LOG(f/fin)理论值恶化约3.8~6.5dB,同频模拟锁相环PDRO相位噪声如图7所示,为–129.9dBc/Hz@1KHz,–135.4dBc/Hz@10KHz,可见本设计相位噪声与模拟锁相环相当,甚至更优。

图6 输出频率相位噪声

图7 同频PDRO相位噪声

与标准盒体PDRO(40×40×12.8mm)相比,集成管壳的体积为20×15×4.8mm,减小到原来盒体的7.5%左右。采用标准集成管壳可用于PCB板表贴,对用户来说使用更方便简易。

3 结语

本文根据工程需要,设计了基于3D电路结构的小型化混频锁相源。采用BGA植球工艺实现类陶瓷基板的互联,实际测试指标也满足用户要求[4]。对该设计结构而言,CRO一般可以覆盖1.0-5.0GHz,输出频率经过倍频滤波(MMIC)后,频率可以覆盖1.0-20GHz,在一定范围内可以替代PDRO。这种结构使频率源的体积大大缩小,可广泛应用于频率源的小型化设计,基于这种设计思路还设计了乒乓锁相环、DDS封装、宽带锁相环、激励锁相环等相关频率源系统[5-6]。

由于鉴相器本底相位噪声与梳谱相位噪声相当,混频后恶化相位噪声约3dB,优化鉴相器本底相位噪声可以改善本设计输出频率相位噪声。自行研制的鉴相器本底噪声可以达到–230dBc/Hz,使用该鉴相器设计可以优化输出频率相位噪声约1.8dBc。