一种高性能信号处理SIP 芯片的设计

李欣LI Xin;张渊ZHANG Yuan;汪鹏志WANG Peng-zhi

(①海军研究院空中所,上海200436;②武汉船舶通信研究所,武汉430079)

0 引言

伴随电子科学技术的快速发展,工业界对半导体芯片的轻重量、低成本、小型化以及性能的要求越来越高。系统级封装(System in Package,SIP)技术是一种可以把多种功能芯片在有限空间外壳中结合成整体系统的封装技术。和传统PCB 不同,采用SIP 技术的芯片具备系统可靠性高、尺寸小、轻重量、研制成本低以及开发时间短的优势。在无线通信设备的信号处理系统中采用SIP 封装技术,能够在有限空间中保持系统存储大小、性能指标不变,同时还能降低系统的尺寸大小、重量以及能耗,这对信号处理系统的小型化、高可靠性、高性能以及轻量化等方面具有重大意义,SIP 封装技术已经成为实现无线通信设备小型化的重要手段。

本文设计基于SIP 技术高性能信号处理芯片,内部集成 FPGA、DDR3、SDRAM、eMMC 和 NOR FLASH 等 4 种主要电路,该系统将拥有不同功能的通用微处理系统集成封装在一块很小的SIP 芯片中,使得系统具备体积小、重量轻、高性能以及低功耗的特性。

1 SIP 芯片总体设计方案

本文设计的信号处理SIP 芯片主体由FPGA,DDR3,EMMC,NOR FLASH 构成,具备数据处理与存储能力。其中FPGA 为ZYNQ-7000 系列的XC7Z045,该电路可分成两部分,分别是处理器系统端Processor System 以及可编程逻辑端Programmable Logic。PS 端拥有一个接口种类完备并且带片上存储器的双核Cortex-A9 ARM 处理器,时钟频率可以达到866MHz,具备定点与浮点运算能力,每个CPU 的处理能力达到2.5DMIPS/MHz,包含DDR3 接口、Ethernet 接口、USB 接口、CAN 总线接口、SD/SDIO 接口、SPI、UART、I2C 等丰富的通用接口。PL 部分包含与Kintex-7 规模相当的LE 资源,与PS 通过AXI 总线进行无缝连接,使二者的功能完美的结合。

SIP 芯片内部功能模块包含 FPGA、DDR3、EMMC 和NOR FLASH,其中FPGA 为主要处理器件,DDR3、EMMC和NOR FLASH 都属于FPGA 的外设器件,DDR3 与NOR FLASH 连接至 FPGA 的 PS 端,EMMC 连接至 FPGA 的 PL端。EMMC 控制器与NAND FLASH 共同组成EMMC 模块。

SIP 芯片主要功能与性能指标:

SoC:Xilinx Zynq-7000 XC7Z045;

图1 SIP 芯片内部功能框图

图2 SIP 芯片内部各模块连接原理图

处理器:双核 ARM Cortex-A9,ARMv7-A 架构;

处理器频率:800MHz;

运算能力:2.5DMIPS/MHz per CPU;

L1 Cache:每个核32KB 指令缓存,32KB 数据缓存;

L2 Cache:512KB;

片上RAM:256KB

逻辑规模:350 万门;

Block RAM:19.2Mb;

DSP Slices(18 x 25 MACCs):900

片上 ADC:2x 12bit,1MSPS,17 路外部差分输入,采集片上电压与温度;

Nor Flash:512Mb,QSPI 接口,配置与存储;

DDR3:1GB 32bit,1066MHz;

eMMC:32Gb,25MHz;

对外接口:SPI、IIC、CAN、UART、SD/SDIO2.0/MMC3.31、USB2.0 OTG、GTX、10/100/1000Ethernet MAC、PCIe Gen2 x8;

输入输出端口:128 个PS IO,212 个 HR IO,150 个 HP IO,16 路GTX;

软件:可运行Vxworks;

体积:31mm*31mm*4mm;

封装:BGA900

2 SIP 芯片各模块详细设计

2.1 DDR3 模块的设计

DDR3 模块由 2 片 DDR3 裸芯电路通过微组件的方式实现,每片DDR3 裸芯电路的容量为512MB,位宽为16bit,两片组成总大小为1GB 的微组件。DDR3 微组件直接连接至FPGA 裸芯PS 端的MIO 502 引脚上,MIO 502 引脚是专用的 DDR3 控制器接口,FPGA 与DDR3 微组件主要连接如图3 所示。

图3 内部DDR3 模块连接图

表1 SIP 集成裸芯选型

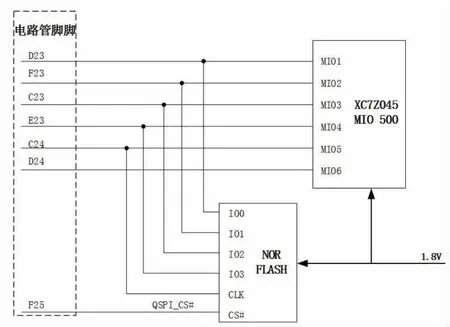

2.2 NOR FLASH 模块的设计

NOR FLASH 模块是通过 RDL 将 WB 形式的 NOR FLASH 裸芯电路转换成FC 形式,直接连接至FPGA 裸芯PS 端的MIO 500 引脚上,MIO 500 的引脚同时还引到SIP芯片封装引脚上。NOR FLASH、FPGA 及SIP 封装引脚的连接如图4 所示。

图4 内部NOR FLASH 模块连接图

2.3 EMMC 模块的设计

EMMC 模块由EMMC 控制器电路与NAND FLASH电路组成,与FPGA 的BANK 9 引脚相连,同时也将信号引至SIP 的封装引脚。EMMC 与FPGA BANK9 的供电电源为3.3V,信号连接如图5 所示。

图5 内部EMMC 模块连接图

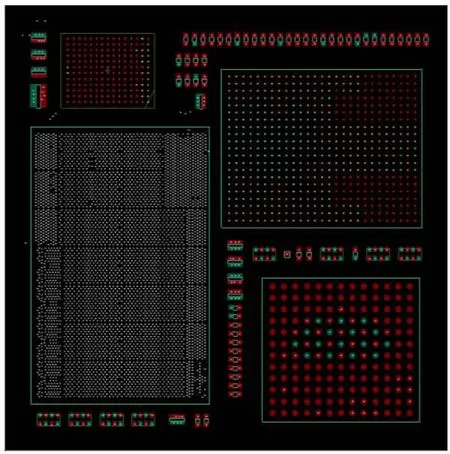

3 SIP 芯片的封装设计

本文设计的SIP 芯片选用BGA 陶封形式实现,对于一个基于BGA 的SIP 芯片,从物理上主要包括裸片与无源器件、基板、裸片与基板的连接3 个主要影响因素。裸片来源于晶圆厂,是SIP 封装的核心部件,根据设计需要,一般会在SIP 中封入两块或者两块以上的裸片。由于SIP 是一个完整的系统,为增加系统性能,需在各管芯周围添加滤波电路、配置电路等外围辅助电路,因此会加入电阻、电容、电感等无源元件,这些无源元件在设计实现时会通过不同工艺埋置在基板中。本文设计的SIP 芯片最终埋入13 颗芯片管芯和若干电阻电容,面积为31mm×31mm,相当于普通封装系统的1/10 ,其内部结构布局如图6 所示。

图6 SIP 芯片内部结构布局图

封装工艺:

基板的选择通常需要考量材料的电阻率(Resistivity)、 热 膨 胀 系 数 (Coefficient of Thermal Expansion, CTE)、介质损耗(Dielectric Loss, DL)、导热率(Coefficient of Thermal Conductivity, CTC)以及介电常数(Permittivity)等特性。本文设计的SIP 芯片采用陶瓷基板,它具有散热性好、气密性强和可靠性高的特点。裸片与基板连接采用Flip-Chip 倒装焊方法,该方法的优势在于焊接点结实、信号传输距离短、电源/地分布广、I/O 密度大、封装体积小以及可靠性高。SIP 芯片集成的DDR3 模块和EMMC+NAND Flash 模块采用两层堆叠陶封,NOR Flash模块采用WB 转FC,FPGA 芯片倒装后粘接散热盖进行散热,产品结构尺寸及封装如图7 所示。

图7 产品结构尺寸及封装图

4 SIP 芯片的测试方案

根据SIP 芯片研制特点,测试主要包括以下三种:

①各种裸芯的CP(Chip Probing)测试:为了提升SIP芯片中管芯的良品率,所有管芯都要在三温环境中进行CP 测试。CP 测试通常是由元器件研制厂家负责执行,当前,它们几乎都拥有完备的CP 测试体系,并且能够结合客户实际的使用需求,进行测试向量的定制补充筛选工作,以此来增大测试的覆盖率,继而提升SIP 芯片良品率。

②成片的自动测试设备(Automatic Test Equipment,ATE)测试:该测试包括使用ATE 进行检测,制作测试底板和测试插座等;进行成片的功能、性能以及可靠性试验,检测SIP 模块功能有无异常,在封装环节中有无缺陷生成,并且检测在经历各种试验后的SIP 芯片能否继续正常运转。

③成品系统级测试:该测试是最终测试(Final Test,FT)的补充,需要制作测试底板以及测试插座,对SIP 芯片的功能、性能以及接口等进行板级或者系统级的检测。如图8 所示。

图8 SIP 芯片成品测试图

5 性能结果及分析

本文设计的高性能信号处理SIP 芯片的最高主频为800MHz,使用WindRiver 公司的Vxworks 操作系统。与传统PCB 信号处理板相比,它们的性能对比结果如表2 所示。

表2 性能结果对比

6 结论

本文分析了信号处理SIP 芯片的技术要求,给出了一种高性能信号处理SIP 芯片的研制设计方案,较详尽地了介绍了该芯片的系统架构、封装以及测试流程。使用这种方案设计的信号处理芯片,在性能和可靠性保持不变的情况下,体积、重量和功耗指标得到了进一步的降低,符合未来无线通信设备小型化的研制需求。