微型近红外光谱仪的光谱信号采集系统设计

黄 磊,顾雯雯,陈 亮,涂 旭,尹欣慧

(西南大学工程技术学院,重庆 400715)

1 引 言

近红外光谱分析技术因其非接触、无损、无需样品前处理、快速、高通量,能定性定量检测固体、液体和气体物质组分与含量[1-2],被广泛应用于工业、农业以及医药等检测领域。传统的近红外光谱仪体积较大不利于便携测量,严重制约了近红外光谱分析技术的进一步发展[3-5]。因此,近红外光谱仪的微型化得到了国内外科研人员的广泛关注和研究[6-7]。光谱信号采集系统作为微型近红外光谱仪的重要组成部分,对仪器的精确性、稳定性以及实时性至关重要[8]。传统的光谱信号采集方案多以外置FIFO、RAM、SRAM作为光谱信号采集系统的数据存储芯片,普遍存在价格昂贵、数据存储空间小、硬件体积大以及外围电路设计复杂等缺点,不利于近红外光谱仪的微型化。因此,开展微型近红外光谱仪光谱信号采集系统的研究对推动微型近红外光谱仪的发展具有十分重要的意义。

相比于DSP、ARM、单片机等主控芯片,FPGA以其独特的并行处理架构被广泛应用于高速信号采集和实时传输控制等应用场景。同时FPGA作为一种高集成度的半定制电路具有很好的灵活性,相对于逻辑接口与接口芯片相匹配的设计方式,FPGA可以直接通过硬件语言编程控制芯片内部的连线来实现逻辑接口的设计,极大降低了外围电路的设计难度。FPGA的可定义与优秀的移植特性使得微型近红外光谱仪嵌入式系统的研发在应用功能的丰富上具有极大的可拓展性。SDRAM相对于外置FIFO、RAM、SRAM等存储芯片,将复杂的外围电路全部集成到SDRAM芯片内部,降低了光谱信号采集系统外围电路的复杂程度。本文以FPGA为主控,SDRAM为光谱数据存储芯片,配合FPGA芯片内部的FIFO对光谱数据进行读写缓存,最后以RS232接口总线的方式将光谱数据传输至上位机。相对于传统的光谱信号采集方案来说,提高了系统的数据存储容量、减小了系统的硬件体积。虽然,该方案增大了光谱信号采集系统时序控制逻辑的设计难度,但是硬件体积的减小更加有利于近红外光谱仪的微型化。

2 光谱信号采集系统的总体设计

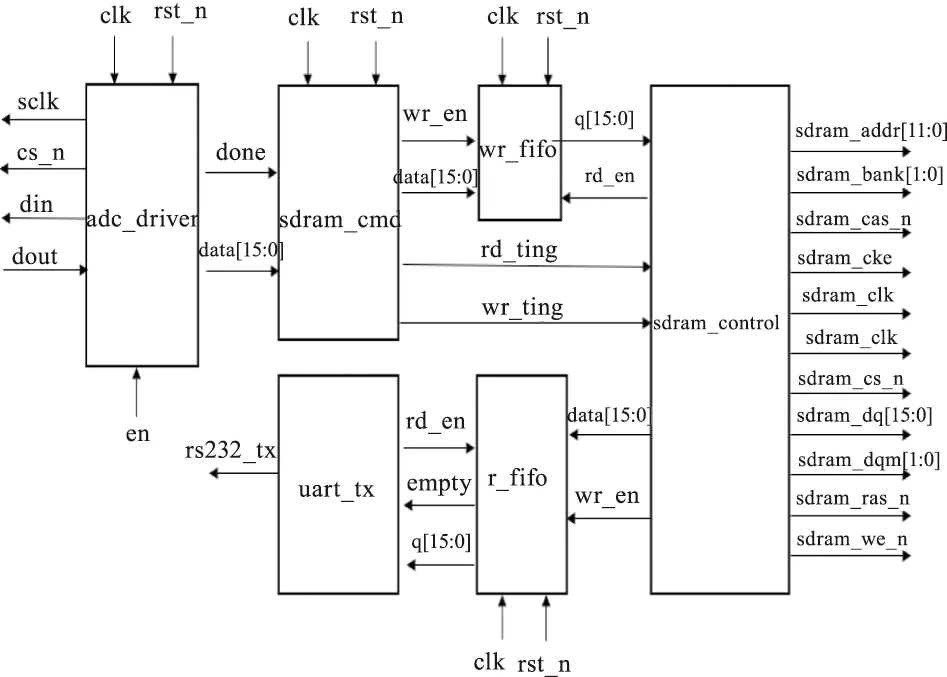

光谱信号经过光电探测器转换以后是一个微安级别的电流信号,需要经过信号调理电路进行一定程度上的降噪和放大处理,以提高整个系统的信噪比同时将信号放大至AD转换电路的电平要求。AD转换电路将模拟信号转换为数字信号,以LVDS电平的形式发送给光谱信号采集系统。以FPGA为核心的光谱信号采集系统在50 MHz的工作频率下,将采集到的数据通过“W_FIFO”写入SDRMA中进行存储,当需要对数据进行读取时,上位机发送相应的指令,通过SDRAM控制器将存储的数据从SDRAM中读取到“R_FIFO”,最后经UART_TX模块以RS232接口总线的方式传输至上位机进行后续的运算处理。整个光谱信号采集系统的设计框图如图1所示。

图1 光谱信号采集系统框图Fig.1 Block diagram of spectrum signal acquisition system

3 光谱信号采集系统的硬件设计

系统采用ATLREA公司的EP4CE10F17C8N作为主控芯片,该芯片具有10320个逻辑单元、414 k嵌入式存储器、23个18×18嵌入式乘法器、两个通用的锁相环(Phase Locked Loop,PLL)以及179个IO口,丰富的逻辑资源足够完成对光谱信号的采集、存储以及传输等功能的控制。以TI公司的12 bit,8通道的ADC128S102作为ADC采样芯片,完成模拟信号到数字信号的转换,最高传输速率可达1 Msps。

3.1 电源设计

电源电路的设计如图2所示。整个系统的供电需求分别为1.2 V、2.5 V、3.3 V、5 V、-5 V。考虑到功耗以及电源纹波对信号质量的影响,选择线性度较好的LDO电源芯片LM1117对1.2 V、2.5 V、3.3 V进行设计,以减少电源对信号的干扰;5 V电源由USB接口提供;-5 V电源由电源芯片TPS6040进行反向得到。在进行PCB板设计时,整个PCB板采用信号层、地层、电源层、信号层的叠层结构进行设计。为了提高整个系统的电磁兼容性,将电源芯片布置在PCB的背板,同时不在电源层和地层走信号线来保证电源层和地平面的完整性,以降低电源对信号带来的影响从而提高信号的质量。

图2 电路原理图Fig.2 Schematic diagram of power supply circuit

3.2 存储方案设计

利用微型近红外光谱仪对物质进行检测时,产生的原始光谱数据需要被尽可能多的采集以保证检测结果的精确性。为了满足光谱采集系统实时大容量采集的需求,需要设计相应的大容量存储方案。传统的光谱信号存储方案主要有外置FIFO、RAM、SRAM等三种。本文以SDRAM作为微型近红外光谱仪光谱信号采集系统的数据缓存芯片与传统的设计方案相比,具有如下的优缺点,如表1所示。

表1 存储方案对比Tab.1 Comparison of storage solutions

相较于外置高速大容量的FIFO与双端口RAM缓存方案,SDRAM采集方案不仅能够实现数据的随机存取,使缓存读写更为灵活,而且价格更为低廉;相较于SRAM的采集方案,SDRAM的集成度高,体积更小,外围电路简单,一定程度上缩小整个采集系统的体积。同时,SDRAM中的数据以电荷的形式进行存取,相比其他存储芯片来说同样大小的存储容量,SDRAM的体积更小,因此更有利于减小光谱采集系统的硬件体积。不足之处在于SDRAM的控制逻辑十分复杂,需要设计专用的SDRAM控制器,设计周期较长。综上所述在各种随机存储器中,SDRAM的价格低、体积小、速度快、容量大是搭建嵌入式光谱采集系统的理想器件[13]。因此,本文选用WINBOND公司的W9812G6KH-75型SADRAM作为缓存芯片,具有128 M的存储容量,能够满足该系统大容量存储的应用要求。

3.3 通信设计

通用异步收发器(Universal Asynchronous Receiver/Trimister,UART)能够实现数据的串/并转换。UART协议作为基础的通信协议,电路结构简单、成本较低,在注重性价比的情况下,UART协议使用极其广泛[18]。为了缩小整个PCB的体积,提高系统的集成度,采用USB接口来取代RS232接口,并通过CH340G芯片来完成USB转串口。根据上位机发送的指令将缓存在SDRAM中的数据通过“R_FIFO”读取出来,并通过串口发送模块将数据传输至上位机。

4 光谱信号采集系统的逻辑设计

根据功能的不同可以将系统的控制逻辑分为六个部分:分别是adc_driver、sdram_cmd、w_fifo、sdram_control、r_fifo以及uart_tx。系统的内部的逻辑框图如图3所示。当外部按下按键就产生一个使能信号en,此时adc_driver模块开始驱动光谱信号采集系统对光谱信号进行采集,每采集到一个光谱数据就产生一个done信号作为sdram_cmd控制逻辑的触发信号,用来调用w_fifo控制逻辑进行数据的写操作。当“W_FIFO”中的数据被写满的时候,sdram_cmd模块就会产生一个wr_ting写触发信号给sdram_control模块,sdram_control通过控制SDRAM将“W_FIFO”中的光谱数据读取到SDRAM中进行存储。当需要对SDRAM中的数据进行读取时,上位机给系统发送一个读取指令,并产生一个rd_ting配合“R_FIFO”将SDRAM中的数据读取出来,最后通过串口发送出去。

图3 系统逻辑框图Fig.3 System logic block diagrams

4.1 sdram_control控制逻辑设计

sdram_control控制逻辑设计的核心部分是对sdram_control状态机的设计,状态机通过对SDRAM的读操作、写操作、自动刷新操作和预充电操作的调度来实现对光谱数据的存储和读取。sdram_control的状态机主要由仲裁状态机、写状态机和读状态机等三部分构成,其中读操作状态转移与写操作状态转移的过程类似。如图4所示,仲裁状态机主要是对SDRAM的操作顺序进行仲裁,通过判断模块间的信号来调度相应的功能模块从而实现想要的功能。1)处于IDLE(空闲)状态下的时候,需要对SDRAM进行初始化操作,否则会产生无法预料的结果,初始化完成后即可跳转到ABRIT(仲裁)状态;2)ABRIT主要功能是对各个信号进行判断,根据信号来调度各个功能模块;3)REF(刷新)状态,当达到了指定的刷新时间,REF状态会产生刷新请求进行刷新操作,来保证SDRAM上的数据不丢失;4)WRITE(写)状态,向ABRIT发送写请求wr_req,ABRIT进行仲裁,在合理的情况下,发送一个wr_en写信号给WRITE状态进行写数据操作;5)读模块的状态转移条件与写模块状态转移类似。默认的优先级从高到低依次是REF状态、READ状态、WRITE状态。

图4 仲裁状态转移图Fig.4 Arbitration state transition diagram

如图5所示,写状态机作为WRITE状态内部的一个状态机,用来完成SDRAM的写数据操作。1)在IDLE状态下,系统会产生一个“空命令”不进行任何操作,等到wr_ting写触发信号到来时跳转到REQ(请求)状态下;2)REQ状态下产生一个写请求信号wr_req给仲裁状态机进行仲裁,当仲裁状态机给写模块发送一个wr_en写使能信号时从REQ状态跳转到ACT(激活)状态;3)ACT状态下对SDRAM进行激活并给定一个行初始地址,等到激活时间结束跳转到WR(写)数据状态;4)WR状态开始对数据进行写入,WR状态跳转到PRE(预充电)状态主要有三种情况ref_end(刷新时间到了)、row_end(一行数据写满了进行换行操作)以及wr_data_end(所有数据写入完毕);5)PRE(预充电)状态下完成对SDRAM的预充电操作,SDRAM是电荷存储机制,需要在相应的时间内进行预充电操作防止数据丢失。最后,在PRE状态下等待信号的产生,完成相应状态的跳转,读状态转移与写状态转移类似。

图5 写状态转移图Fig.5 Write state transition diagram

4.2 sdram_cmd控制逻辑设计

命令解析模块sdram_cmd作为连接w_fifo控制模块和sdram_control控制模块的一个桥梁,会根据接收到的操作信号产生相应的触发信号来驱动SDRAM对“W_FIFO”中的数据进行读取。同时,也控制着“R_FIFO”与串口发送模块的数据读写是整个控制逻辑的关键部分。sdram_cmd模块的接口设计如图6所示。

图6 命令解析模块接口设计Fig.6 Interface design of command parsing module

sdram_cmd的控制逻辑如图7所示,给adc_data发送一个16’h55命令,并配置给cmd_reg命令寄存器提示系统开始进行光谱数据的采集。每采集完一个数据就产生一个adc_done信号,同时产生一个wifio_wr_en信号控制“W_FIFO”写入ADC采样得到的数据。adc_data每接收到一个数据,data_cnt就进行加1操作,当“W_FIFO”存储空间被写满时data_cnt清零并产生一个wr_ting写触发信号提醒SDRAM开始写入“W_FIFO”中的数据。当需要将SDRAM中的数据传输到上位机时,发送一个16’haa命令配置给cmd_reg命令寄存器,并产生一个rd_ting信号用于控制“R_FIFO”对SDRAM存储数据的读取。

图7 时序图Fig.7 Sequence diagram

5 光谱信号采集系统的仿真实验

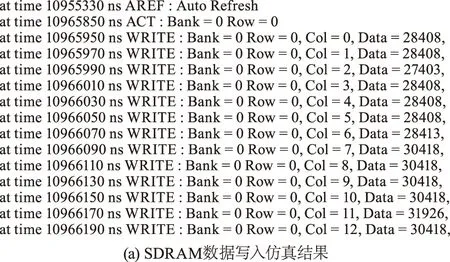

通过编写相应的仿真测试文件对光谱信号采集系统的逻辑功能进行了仿真验证。为了便于对整个系统的逻辑功能进行测试,将adc_driver控制模块修改为了uart_rx串口接收模块,用于接收PC端发送的光谱数据。通过uart_tx接收到光谱数据来模拟adc_driver模块采样得到的光谱数据对系统的逻辑功能进行测试。仿真用到的测试软件是Quartus II 15.0和ModelSim 10.3d,SDRAM模型是在镁光网上下载的W9812G6KH-75 SDRAM官方模型。仿真用到的127个测试数据是基于MOEMS扫描光栅微镜谐振频率为656.38 Hz时采集到的电压数据[19],为了便于uart_tx模块进行仿真测试需要将原始的电压数据进行取整。处理好的电压测试数据如表2所示,仿真结果中SDRAM写入和读取的部分数据如图8所示,串口发送数据波形如图9所示。

表2 谐振频率为656.38 Hz时的部分电压数据Tab.2 Part of the voltage data when the resonance frequency is 656.38 H

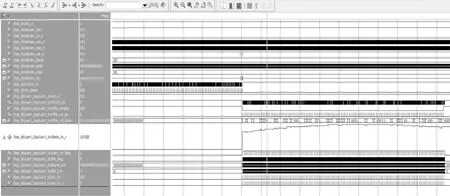

图8(a)和表2对比可以看出由串口发送的电压数据经“W_FIFO”被正确的写入进了SDRAM存储了起来。通过sdram_control控制逻辑对SDRAM进行刷新和预充电操作,确保SDRAM中的数据不会丢失。图8(b)和表2的对比可以看出,在PC端提取数据的过程中SDRAM中的数据被“R_FIFO”正确的读取,经串口发送如图9所示的数据波形。

图8 SDRAM功能仿真结果Fig.8 SDRAM function simulation results

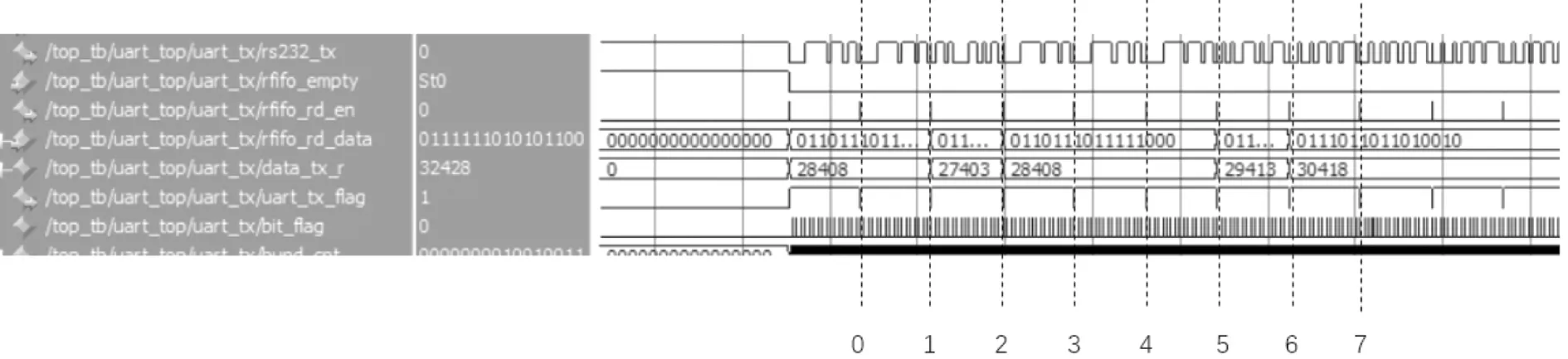

为了验证串口发送数据的正确性,将图9中的data_tx_rx信号的波形以十进制数显示得到如图10所示的结果。对比表2可以看出数据被正确的发送。

图9 发送至上位机的数据波形Fig.9 Data waveform sent to the host computer

图10 串口发送的数据Fig.10 Data sent by the serial port

6 结 论

针对传统的光谱信号嵌入式采集系统数据存储容量小、硬件体积较大、外围电路复杂以及硬件价格昂贵等问题,本文提出了以FPGA,SDRAM、FIFO和串口为核心的光谱信号实时采集和传输系统。主要具备以下几个优点:1)FPGA和SDRAM是高度集成的芯片,大部分电路都被集成到芯片内部,只需要设计专用的控制逻辑完成芯片内部的连线就可以实现想要的功能。因此降低了外围电路的复杂程度,一定程度上减小的PCB的体积,有利于近红外光谱仪的微型化;2)SDRAM是以电荷的形式进行数据存储,相对于以CMOS晶体管形式存储数据的SRAM来说,同样存储容量的SDRAM体积更小、功耗更低。只需要通过设计相应的SDRAM控制逻辑完成正确的预充电和刷新操作,就可以确保数据不会丢失。3)鉴于,CMOS晶体管的数据存储机制,决定了SRAM容量不可能被做到很大。而目前SDRAM最多可做到512M的存储容量,采用该方案能够满足光谱信号大容量的采集要求。4)该方案相对于其他方案来说成本较低,但是需要设计复杂的控制逻辑,设计的周期较长。本文通过编写相应的功能测试文件对系统的控制逻辑进行了验证,结果表明光谱信号采集系统的时序控制逻辑可行,能够正确控制光谱信号采集、大容量存储和实时传输等操作。基于FPGA的可升级特性,后期可以采用USB来完成对数据的传输,进一步提高光谱数据传输的速率。