基于GaAs的5G通信手机功率放大器设计

李海鸥, 谢志远

(桂林电子科技大学 广西精密导航技术与应用重点实验室,广西 桂林 541004)

第四代移动通信系统4G在我国大范围普及,为第五代移动通信系统(5th generation mobile network)5G的建设与发展打下扎实基础,新一代通信的射频前端研究必须尽快开展[1]。相比于4G通信系统,5G通信系统旨在提供更快的通信速度、更低的系统延时性、更大的系统容量、更高的系统可靠性、更安全且绿色节能和更大规模的设备互联。从近期的数据分析可知,5G通信系统的数据传输速率高达20 Gbit/s,其系统延时性降低至小于10 ms[2]。从各行业的应用分析得出,5G通信技术具有满足多种特定场景特殊需求的能力,可拓宽以及融合各个产业发展空间的潜力[3],是支持工业4.0的关键技术。

第五代移动通信系统的数据传输速度比第四代移动通信系统快100倍,并且传输信号的频率更高。频率越高,信号传播距离越短,导致基站覆盖半径较小,受到基站数量和高频信号传播的能量耗散等问题影响,用于第五代移动通信系统的功率放大器需要更高的增益和输出功率。输出功率的大小由功率放大器(power amplifier)末级放大电路的晶体管发射极面积决定,更高的输出功率需更大的发射极面积。末级放大电路的多个晶体管并联,导致末级放大电路的输入阻抗非常接近0。使用LC匹配网络无法将末级放大电路与次末级放大电路级间匹配的回波损耗S11优化至-10 dB以下,因此,整体版图仿真结果将无法满足设计要求。采用变压器匹配网络在优化回拨损耗问题上具有较为明显的优势,并可通过变压器功率合成技术提高整体功率放大器的输出功率。

该PA采用三级放大电路结构,在PA第三级放大电路与第二级放大电路级间使用变压器匹配结构,有效地将级间S11优化至-20 dB,使工作全频段整体PA的S11小于-10 dB。该PA的第一级放大电路为单端输入、单端输出结构;第二级放大电路为单端输入、双端差分输出结构,信号经变压器转为180°的差分信号;第三级放大电路为双端差分输入、单端输出结构,两路差分信号经变压器合成一路信号。变压器为四端口结构,变压器的隔离端给第二级放大电路提供电源,PA的第二级放大电路单端输出信号传输至变压器,信号经变压器主级线圈并联接地,并将变压器的次级线圈上耦合出的2个大小相同、相位相反的差分信号输入至第三级放大电路。PA的第三级放大电路的两路差分信号经过基板上变压器合成为一路信号,此时输出功率与增益进行合成,有效提高了输出功率与增益。该PA通过在晶体管基级串联电阻和增加负反馈结构达到工作全频段绝对稳定,采用自适应有源偏置电路技术和双偏置电路技术,在提供稳定的静态电流的情况下,有效提高了PA输出功率的线性度。

1 变压器的结构设计及其原理

设计的变压器有2个,一个变压器参与PA第二级放大电路与第三级放大电路的级间匹配,为片上变压器;另一个变压器参与PA第三级放大电路的输出匹配,为基板上变压器。

片上变压器作用为:将PA原第三级放大电路拆分为两路,由N个晶体管并联改为两路N/2个晶体管并联,因此,增大了PA第三级放大电路的输入阻抗值。级间匹配难点在于阻抗值之间相差较大,变压器参与匹配后,PA第三级阻抗值增加,由此降低匹配难度。交流信号经过变压器主级线圈后,在次级线圈上耦合出一个信号。PA第三级放大电路的信号为差分信号,2个信号相位相差180°,为确保2个信号的相位准确,本设计使用的变压器为对称互绕变压器[1],该变压器的结构完全对称,可确保2个信号相位相差180°。PA第三级放大电路的两路差分信号与原信号相位相差180°,经基板上变压器再次转换相位180°,该信号此时的相位与原信号相位相差360°,即0°,因此可进行功率合成[2-8]。合成后的增益、功率均为原增益、功率的2倍。

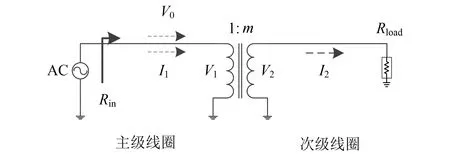

图1为变压器结构原理图,Rin为PA第二级放大电路的输出阻抗,Rload为PA第三级放大电路的输入阻抗,且次级线圈为串联连接,次级线圈的电流相同。基于变压器基础理论可得[9-11]:

图1 变压器结构原理图

(1)

(2)

(3)

V0为交流电压,且当V2=2mV0可得:

(4)

本设计的变压器为两路差分,则m=2,可得:

(5)

若不采用两路差分,则m=1,可得:

(6)

比较m不同时对应的Rin,可得采用两路差分结构,相同的Rload可与更小的Rin进行匹配。设计的难点在于PA的第二级放大电路的输出阻抗与PA的第三级放大电路的输入阻抗相差较大。使变压器匹配两路差分结构,PA的第二级放大电路的输入阻抗值一定时,可与更小的第三级输入阻抗值完成匹配[12],获得到较好的S11。

2 PA原理图与版图设计

2.1 PA原理图设计

图2为偏置电路原理图,该偏置电路为自适应有源偏置电路。当PA输入功率增大,晶体管Q0基极电流增大,导致Q0的基极电位降低,同时部分射频主路上动态信号会泄露至偏置电路,信号经Rbias流至Q4,通过电容CL到地,因此偏置电路不受射频信号影响。在温度变化时,偏置电路的晶体管基级电压表示如下:

Vb,Q2=Vreg-(IC1+Ib,Q2)R6,

(7)

Vb,Q3=Vreg-(IC2+Ib,Q3)R5,

(8)

Vb,Q4=Vreg-(IC3+Ib,Q4)R4。

(9)

图2 偏置电路原理图设计

射频主线路上的晶体管因其自热效应,Q0的基极电位下降,因此,Q0基级静态电流随之增大,Q0基极-发射极之间的电压Vb,Q0减小;晶体管Q1的基极电位Vb,Q1因此减小,晶体管Q1的基电极电流Ic1下降,电阻R6与晶体管Q1串联,电阻R6上的电流减小,即R6两端所加电压减小;晶体管Q2基极电压Vb,Q2随之升高,晶体管Q2基电极电流增大,电阻R5两端所加电压增大;晶体管Q3基极电压Vb,Q3随之降低,晶体管Q3基电极电流降低,电阻R4两端所加电压减小;晶体管Q4基极电压Vb,Q4增大,从射频主线路泄露进Q4的动态信号使得Vb,Q4降低。该自适应有源偏置电路通过反馈结构,使得射频主线路上Q0的偏置电压基本保持不变。通过调节R1、R2、R3、R4、R5、R6的电阻值大小,可以调节各电阻对应串联电路上的晶体管的基极电位大小,达到控制偏置电路电流大小与电压补偿值[13-17]的目的。

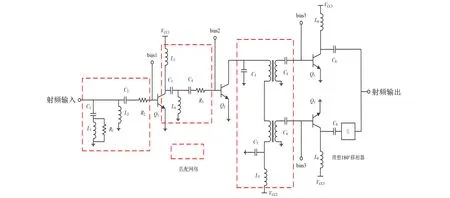

PA原理图设计结构如图3所示,PA第一级匹配网络增加了一个CL串联到地的谐振结构,R1可控制该谐振网络的带宽。N79频段较高,S21平坦度较难优化,且HBT自身增益随频率增大逐渐降低,该CL谐振结构可将PA第一级放大电路低频增益降低,维持增益随频率增加趋势;PA第二级放大电路增益趋势保持为增益随频率变化较小;PA第三级放大电路增益较难控制,其增益趋势为增益随频率增加而降低,此时PA三级放大电路级联后增益较为平坦。PA第二级与第一级放大电路的级间匹配为两阶LC匹配,可达到级间匹配的S11,低于-20 dB。PA第一级放大电路的VCC1通过扼流电感L3直接为晶体管Q1供电,PA第二级放大电路的VCC2通过变压器隔离端给晶体管Q2供电。R2、R3串联在射频主线路的晶体管基极,可降低匹配难度,更好优化S11,并增加稳定性,但导致增益与输出功率降低,所以第三级放大电路不采用该方法优化S11。PA第三级与第二级放大电路的级间匹配为变压器匹配,C6为隔直电容且参与匹配,变压器为具有耦合效应的电感,此时的C5、变压器、C7、L5近似为CLCL匹配网络,C6变压器、C6近似为CLC匹配网络。PA第三级放大电路的VCC3由基板上变压器供电,图3中用理想隔交(DC_Feed)L0代替变压器。PA第三级放大电路一路信号直接理想隔直(DC_Block)输出,PA第三级放大电路另一路信号经理想为隔直(DC_Block),再经理想移相器后输出。该移相器的相位为180°移相,将此处与原信号相差180°的信号再次移相180°,即360°,使得PA第三级放大电路两路信号相位相同,因此可进行功率合成。且功率合成后,该输出阻抗为原PA第三级放大电路一路输出阻抗的一半[18-20]。

图3 PA原理图设计结构

2.2 PA版图设计

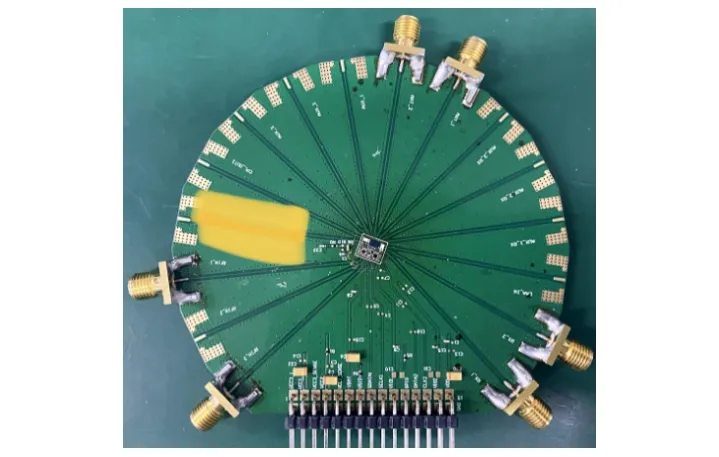

设计的PA版图为3层布线金属,如图4所示,采用AWSC的HBT工艺,尺寸小于1 mm2,长宽均小于1 mm。在ADS上完成版图与原理图设计、仿真,在Cadence上完成DRC、LVS检查和流片。

图4 PA整体版图与基板

在版图设计阶段,必须保证变压器结构严格对称,从而保证主级线圈与次级线圈的匝数比为1∶1;以此确保2个信号的相位差为180°,并且与原信号大小相同。否则另一路与原信号相位相差180°的信号,经过基板上变压器再次将该信号转换180°后,无法确保此时该信号与原信号的相位相差360°,即0°,此时将无法进行正常功率合成。因第一层金属较薄,寄生参数较大,该层金属只能作为导线,应尽量避免使用第一级金属设计变压器与电感,使用第二、三层金属可增大变压器与电感的Q值。

3 仿真与测试结果

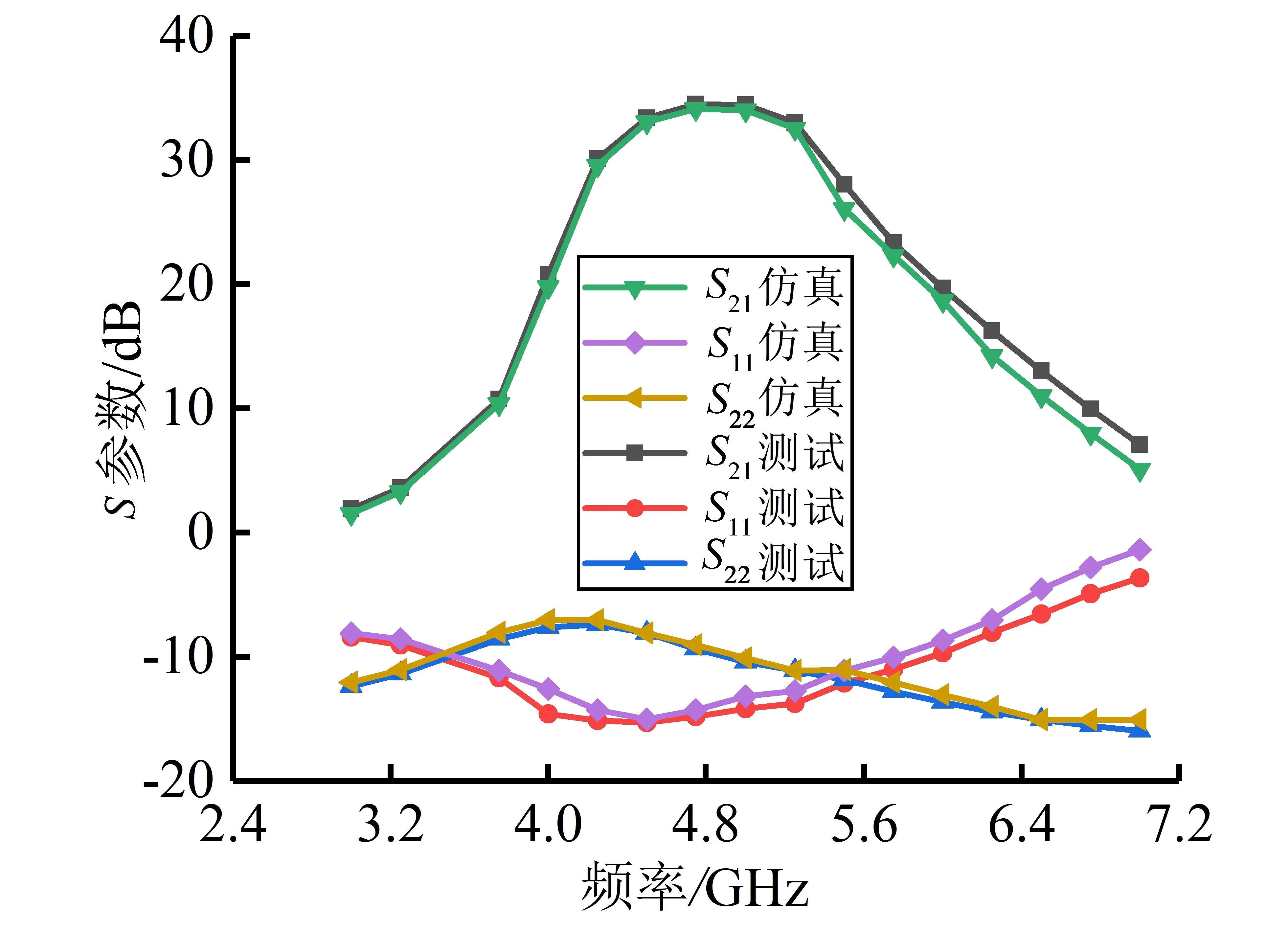

PA各级放大电路的VCC、Vbat分别为5.0、4.2 V,PA第一级放大电路的Vreg为2.8 V,PA第二级与第三级放大电路的Vreg为3 V。设计采用AB类静态偏置点,各晶体管发射极静态电流为10 mA左右,总电流为350 mA。图5为S参数仿真与测试结果。在4.5~5.0 GHz的工作频率下,增益仿真结果为33.5~34.5 dB,增益测试结果为33~34 dB,增益达到设计指标,PA三级放大电路实现较高增益;S11仿真结果为-15.3~-14.2 dB,S11测试结果为-15.0~-13.2 dB,N79工作全频段S11小于-10 dB,电路总体性能的测试结果较好;测试S参数结果和仿真S参数结果均比较接近。PA整体的输出反射系数S22测试结果与仿真结果很接近,相对其他S参数的测试与仿真结果,在仿真阶段为-8.0~-10.3 dB,在测试阶段为-8.0~-10.1 dB。

图5 S参数仿真与测试结果

图6为PA大信号测试结果,在N79频段4.50、4.75、5.00 GHz这3个频点所对应的1 dB功率压缩点均大于37 dBm,且1 dB功率压缩点所对应的效率均大于45%;输出功率从1 dB功率压缩点直至饱和功率,增益几乎在1 dB内迅速下降。该PA采用的静态工作点为AB类偏B类的静态工作点,因此效率较高。

图6 PA大信号测试结果

4 结束语

设计了一种适用于5G频段手机端的功率放大器,并通过分析变压器匹配的优点和有源温度补偿偏置电路原理,对PA整体放大电路进行仿真、优化和测试。在频率为4.5~5.0 GHz时,测试结果与仿真结果较接近;在PA级间使用变压器匹配,优化整个频段S11;采用功率两路合成,在保证较高效率的前提下,有效增大增益、输出功率。该PA可应用于5G手机端芯片,可进一步实现国产替代,具有较大的使用和生产价值。