一种继电保护控制装置掉电保护设计

南京国电南自自动化有限公司 陈继洪

国家的碳中和、碳达峰战略计划颁布后,能源领域针对自身特点,将发展水电、风电及分布式光伏发电等清洁环保发电方式作为重要工作,面对越来越多样化的安装环境,继电保护控制装置的环境适应性、可靠性要求也越来越高。继电保护控制装置发生供电电压跌落现象时,装置内的存储器件可能会出现误擦除、误写入等问题,这将极有可能导致整个继电保护装置工作异常、无法启动等严重故障。按照《GB/T 14598.26量度继电器和保护装置》第26部分电磁兼容的要求,继电保护装置在发生供电电压暂降、瞬断时,允许出现暂时性功能丧失,但要求在故障消失后能自恢复。

针对这一问题,相关学者的研究已经取得了一定的成果,文献[1]阐述对比了备份文件方式和高可靠性系统设计两种方案解决继电保护装置意外掉电破坏参数问题的优缺点;文献[2]对eMMC 进行可靠性特性分析,针对常见的掉电失效模式提出了文件系统感知的磨损均衡、依据数据的属性合理映射分区、减少写入次数以及降低写放大效应等措施;文献[3]公开了一种应用于非易失性存储器件的硬件掉电保护方案,通过主备分区的冗余设计,以备份标志、备份次数为依据进行掉电保护更新。

以上几个文献公开的方案主要是从存储器工作过程中进行软件备份或者规避,无法解决电压波动引起的存储器件误操作问题。针对这一场景本文提出了一种低成本、高可靠性的硬件掉电保护电路设计方案,在发生供电异常时通过控制存储器件外部硬件写保护管脚屏蔽写操作来保护数据,文中经过理论分析和仿真验证,可以有效的解决该场景下误操作问题。

1 硬件架构设计

Nor Flash 一般用于存放继电保护控制装置CPU 处理器正常工作所需的BIOS 程序,是非常重要的一个存储器件,一旦出现存储数据改写或者丢失就会导致整个继电保护装置无法启动,下文就以Nor Flash 为例进行分析和研究。

1.1 存储芯片功能简介

Nor Flash 芯片常用SPI 接口,包括设备选择线、时钟线、串行输出数据线、串行输入数据线4根信号线。芯片厂家在设计时考虑到Nor Flash 容易发生存储数据改写、丢失等问题,在芯片内部集成了写保护功能,可以通过外部写保护管脚WP#和内部寄存器配合实现大部分场景下的存储数据保护功能,以兆易创新GD25Q64C 系列Nor Flash 为例,其芯片内置写保护功能可以归纳成表1所示的真值表。目前业界常用的写保护管脚WP#接法是外部硬件写保护不使能,交由软件通过写使能位WEL 进行写使能控制。但是这种方案在芯片发生供电波动、掉电等异常场景时芯片本身工作状态不正常,软件写控制功能无法生效。

表1 Nor Flash 写保护功能真值表

1.2 掉电保护电路架构

存储器件在供电不稳定时SPI 接口信号线状态是不确定的,有可能会触发错误的读写操作,导致存储数据发生改写、擦除等严重故障。针对这一问题,本文提出了一种低成本、电路简单的硬件掉电保护电路设计方案,在继电保护装置上电、下电以及供电欠压时,通过使能存储器件硬件写保护管脚WP#,屏蔽掉所有的软件写操作,保证不发生误操作。

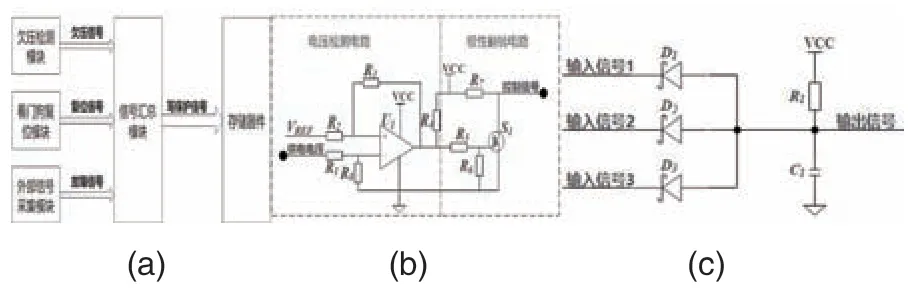

本文提出的硬件掉电保护电路设计方案架构如图1(a),该设计方案架构由欠压检测模块、看门狗复位模块、外部信号采集模块以及信号汇总模块组成。其中,欠压信号、复位信号和故障信号都是低电平有效,经过信号汇总模块“与”操作后产生用于控制存储器件外部硬件写保护管脚WP#的控制信号,只有在欠压信号、复位信号和故障信号都为高电平正常状态时存储器件的外部硬件写保护功能才是不使能状态,此时才能对存储器件发起写入操作。

欠压检测模块如图1(b)所示,迟滞比较器电路构成了电压检测电路,小信号mos 管构成极性翻转电路,用于监控存储器件的供电电压状态。当供电电压高于设定的阈值时输出的控制信号翻转成高电平正常状态。看门狗复位模块在CPU 处理器系统中比较常见,主要用于系统程序跑飞时产生复位信号,使得CPU 处理器复位后恢复正常工作状态,此处将看门狗复位信号引过来是规避CPU 处理器状态异常时发起的未知随机操作,不额外增加电路成本。外部信号采集模块用于采集其他关联装置送过来的故障信号做联动处理,此模块为可扩展模块。

信号汇总模块如图1(c)所示,使用3个二极管组成“线与”电路,只有当3个输入信号都为高电平,即无异常状态时输出信号才会是高电平状态,后级的存储器件才能正常进行写操作。

图1 硬件掉电保护电路

2 参数设计及仿真验证

本文提出的硬件掉电保护电路欠压保护动作点和恢复点可以根据实际场景进行设定。图1(b)中控制信号由低电平翻转到高电平时,供电电源Vih可以用如下公式表示:Vih=R3/(R2+R3)×VREF-R2/(R2+R3)×VL(1),式中,VREF为参考电压值,VL为比较器供电负电压;图1(b)中控制信号由高电平翻转到低电平时,供电电源Vil可以用如下公式表示:Vil=R3/(R2+R3)×VREF-R2/(R2+R3)×VH(2),式中,VREF为参考电压值,VH为比较器供电正电压;综合公式(1)(2),回差电压ΔV 可以表示为:ΔV=R2/(R2+R3)(VH-VL)(3)。

结合应用场景,参考电压VREF取2.5V,比较器供电正电压VH取3.3V,比较器供电负电压VL取0V;设定门限电压Vil和Vih分别为2.97V 和3.25V,回差电压ΔV 为0.28V。将以上参数值代入公式(1)(2)(3),计算得到图1(b)中电阻R1、R2、R3和R8的阻值分别为1kΩ、1kΩ、20kΩ 和3.74kΩ。为了验证本文提出的低成本、高可靠性硬件掉电保护电路设计方案的可行性,按照章节2设计的参数,搭建仿真模型。

仿真波形如图2所示,图2(a)为存储器件写保护管脚WP#仅由供电电源VCC 检测结果控制的波形,可以看到VCC 上电时电压达到约3.25V 后WP#信号翻转为高电平,存储器件可以进行写操作;当VCC 掉电时只要检测到电压低于正常值(2.95V)就会拉低WP#,存储器件无法进行写操作;图2(b)为存储器件写保护管脚WP#由欠压信号、复位信号和故障信号同时控制的波形,可以看到只有3个控制信号都是高电平正常状态时WP#才翻转为高电平,可以进行写操作;当有一个控制信号为低电平异常状态时,WP#立刻翻转为低电平,存储器件无法进行写操作。仿真结果证明了本文所提硬件掉电保护电路的可行性。

图2 仿真结果

3 结论

所提的低成本、高可靠性的硬件掉电保护电路可以设定欠压点和保护回差值,并在检测到欠压故障或者其他需要动作的异常时,控制WP#管脚禁止写操作,保证存储芯片内数据不被改写或误擦除,可以有效解决继电保护设备掉电后无法启动问题;所提的低成本、高可靠性的硬件掉电保护电路可以应用于各类存储芯片掉电保护,在电力装置、通信设备和工业控制设备等领域有一定借鉴意义。