基于嵌入式Linux 操作系统的电缆故障测距系统研究

蒋志炀, 白晓斌

(国网陕西省电力公司宝鸡供电公司,宝鸡721004)

0 引 言

由于外力损伤、绝缘受潮老化或化学腐蚀等原因导致的各种故障,随着电缆的运行会不断出现[1]。 随着电力电缆敷设数量和种类的增加,运行负荷和时间的增长,电力电缆故障发生频率越来越高[2]。 由于电缆芯线由多层保护材料包裹,而且在电缆敷设时,一般直接埋入地下或放置于电缆沟中,电力电缆一旦发生故障,寻找故障点位置变得十分困难[3]。 因此,在电力电缆故障发生后,如何快速准确地进行电缆故障位置测距,并进行电缆故障修复,对保证电力系统的可靠性和稳定性,减小由电缆故障带来的损失具有重要意义。

电力电缆故障发生后会导致电缆的阻抗特性发生改变,引起电缆阻抗的不连续。 由传输线时域反射原理可知,电磁波信号传输时,遇到阻抗突变或不连续处会发生反射[4]。 电力电缆作为传输线的一种,可以通过信号发生装置向已经发生故障的被测电缆注入脉冲电波信号,使用信号检测装置采集入射和反射脉冲信号,而后根据仪器检测所得到的两者之间的时间差,结合电缆中电磁波传播速率,即可计算出阻抗不匹配位置距离脉冲注入点的长度,由此实现电缆特性突变点的测距。 这种方法可以实现迅速无损的电缆故障测距,同时也可以利用电磁波信号波形的时频域信息实现简单有效的故障类型分析,为故障电缆的快速维修提供帮助。

1 电缆脉冲时域反射

电磁波在传输线上发生反射的现象是最基本的物理现象。 在传输线路径中进行传输的信号,若其感受到阻抗发生变化或不连续,便会发生反射。 被反射的部分信号将向反方向传播,而透射的部分将继续向前传播[3]。

传输线中阻抗突变点产生反射如图1 所示,Z1为线路1 的阻抗,Z2为线路2 的阻抗,两条线路的相接处为J,入射信号在传输到J 处时,感受到阻抗的变化,将在此处发生反射,反射信号的信号量由阻抗突变点的变化量决定,可以使用反射系数ρ和传输系数τ进行表示。

图1 传输线中阻抗突变点产生反射

反射系数ρ是反射信号电压幅值(U反射)和入射信号电压幅值(U入射)的比值:

类似地,传输系数τ定义为传输信号的电压幅值(U传输)与入射信号电压幅值(U入射)之比,其与反射系数ρ之间的关系如式(2)所示:

由式(1)可知:传输线存在以下3 种特殊情况。以图1 为例,若线路1 末端为开路,不连接线路2,即线路2 阻抗Z2=∞,计算出反射系数为1,意味着信号在界面J 处产生与入射信号具有相同极性和大小的反射信号返回到入射端。 第二种情况为线路1末端短路,及线路2 阻抗Z2=-1,计算出反射系数为零,意味着信号在界面J 处产生与入射信号极性相反但大小相同的反射信号。 第三种特殊情况为线路1 与线路2 阻抗匹配,即Z1=Z2,此时反射系数为零,信号将不会在J 界面处产生反射。

结合传输线反射理论,向电缆中注入脉冲,并使用仪器检测电缆入射和反射脉冲信号,检测到入射和反射脉冲信号时间差为Δt,并根据脉冲信号在电缆中的传播速率(ν), 便可计算出阻抗突变点距信号入射端长度:

2 脉冲信号发生与系统检测整体设计

2.1 硬件总体设计

依据电缆中脉冲信号的传输和反射原理,向电缆中发送的脉冲信号宽度及幅值应与电缆的长度相关,同时为减小脉冲宽度带来的盲区,所需的脉冲的宽度应该尽量窄,常用的脉冲宽度为纳秒级,因此检测系统应能够产生超窄的纳秒级脉冲,并使用高速信号采集系统对电缆中的脉冲信号进行检测[5-6]。

考虑到FPGA 具备可编程性好,运行速率快,适合高速并行电路等特点,为满足高速信号发生、数据采集和缓冲的需求,本系统选择使用FPGA 实现纳秒级脉冲发生和高速数据采集。 同时,为更好地进行系统控制和交互,本系统中选用了恩智浦i.MX6D处理器作为控制核心,其包含两个运行频率达1.2 GHz的ARM Cortex-A9 核心,且具备出色的图形显示能力和丰富的接口资源。 考虑到直接使用i.MX6D处理器设计电路需要使用8 层PCB 设计,且包括众多高频高速电路,其工艺要求高,成本也较高,因此,本系统中采用“i.MX6D 核心板+底板”模式进行设计。 核心板集成了处理器和存储器等核心资源,只需要根据所需功能设计相应的外设电路即可,增加了系统的稳定性和可维护性。 整个系统由控制部分、脉冲发生及采集部分、电源模块三部分组成,系统硬件结构框示意图见图2。

图2 系统硬件结构框示意图

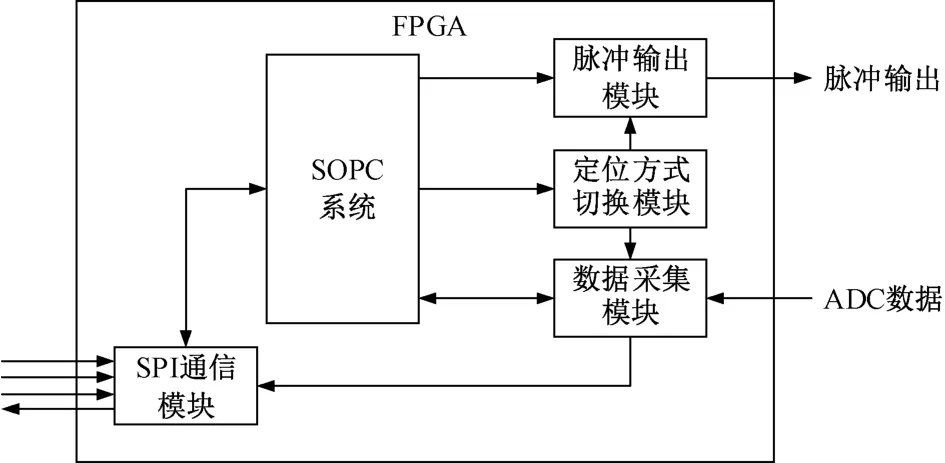

FPGA 内部逻辑框示意图见图3。 图3 中控制部分采用SPI 接口与脉冲发生及采集模块进行数据通信与交互,其中控制部分由freescale i.MXD 处理器及其外围电阻组成,完成对整个系统的控制、交互、显示和数据存储等功能;脉冲发生及采集部分以Cyclone III FPGA 为核心,采用片上可编程系统,结合SOPC 系统与自定义逻辑实现FPGA 设计。 首先利用窄脉冲发生电路产生纳秒级脉冲信号并输入被测电缆,使用信号调理模块和数据采集模块分别对电缆中的入射和反射脉冲信号进行处理和采集,采集到信号转化为数字量由FPGA 数据采集模块经SPI 接口送入ARM 中进行处理与显示。 SOPC 系统完成FPGA 各个模块初始化,同时能够解析SPI通信模块接收的来自ARM 的命令,控制其他模块执行相应的动作。

图3 FPGA 内部逻辑框示意图

2.2 软件总体设计

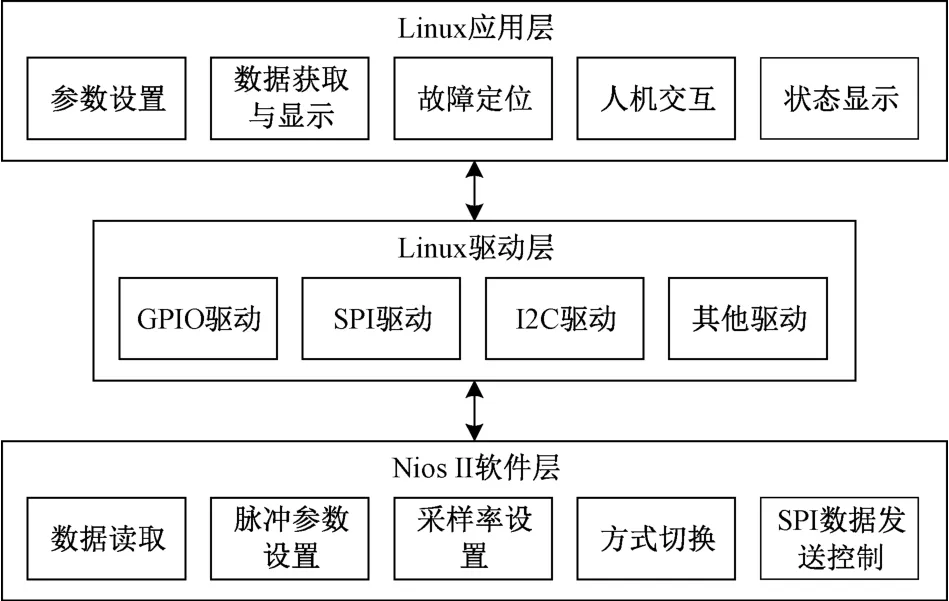

整个检测系统的软件主要由应用层、驱动层和FPGA 层程序等组成,软件总体框示意图见图4。

图4 软件总体框示意图

检测系统控制部分ARM 核心板采用嵌入式Linux 系统,数据采集部分采用基于SOPC 的NiosⅡ程序设计。 上电启动后将自动初始化系统硬件,并显示人机界面程序。 应用层完成系统的交互和测试相关参数的设置,用户设置参数经过驱动层传输到FPGA 内部,经过程序解析命令后依据用户所设置参数设置脉冲宽度和ADC 采样率等。 FPGA 采集到的脉冲信号将数据采集 FIFO 写满后,通过GPIO 通知控制部分驱动层,驱动层接收信号后通过SPI 接口读取FPGA 脉冲数据,并将数据发送到应用层进行脉冲波形显示、数据存储和处理及故障测距等。

3 主要硬件电路设计

3.1 窄脉冲发生电路

本工作中所设计的脉冲发生电路将数字逻辑与MOSFET 放大电路相结合,利用电容储能式脉冲发生器原理产生宽度可调的纳秒级窄脉冲信号[7-8]。

由于电缆存在损耗,输出脉冲幅值太低时,反射脉冲幅值可能衰减到背景噪声中导致无法分辨反射点位置,因此输出脉冲幅值不能太低。 工程应用中常使用负脉冲进行电缆故障定位,因此,电路幅值为-5~-35 V 可调,用于满足不同的测试场合。

脉冲发生模块示意图见图5。 FPGA 发出宽度可调的脉冲信号,经由栅极驱动器放大后将脉冲信号的电压幅值提高至系统电压12 V,以此驱动MOS FET 的通断。 FPGA 同时产生高频脉冲信号控制升压整流模块,用来产生所需的电压幅值。 在MOS FET 的源极输出低压脉冲信号并经过阻抗匹配电路传输到待测电缆。

图5 脉冲产生模块示意图

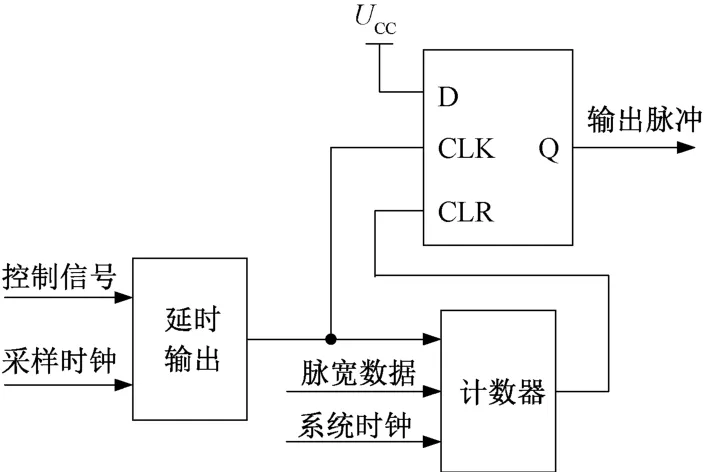

脉冲宽度的调节利用FPGA 逻辑实现,逻辑框图见图6。 控制信号经过30 个采样时钟延时后输出,开始产生脉冲。 使用计数器和D 触发器实现脉冲宽度调整,计数器依据脉宽数据引脚控制D 触发器以产生不同宽度的脉冲信号。

图6 脉冲输出模块示意图

3.2 脉冲信号调理电路

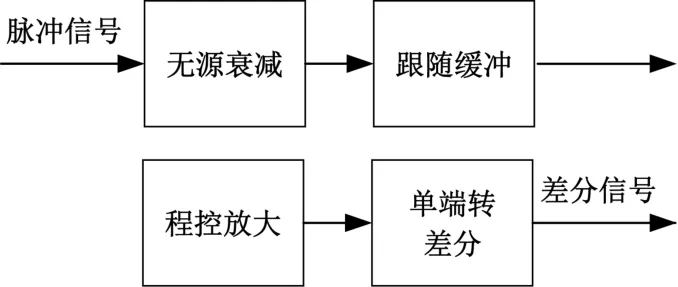

脉冲入射和反射信号的调理是整个系统的关键部分,由于脉冲发生电路输出的脉冲宽度窄频率高,必须保证信号在调理采集过程中尽可能地减小失真变形。 脉冲信号调理部分电路主要由无源衰减、跟随缓冲、程控放大和单端转差分等4 个部分电路组成,脉冲信号调理电路结构框图见图7。

图7 脉冲信号调理电路示意图

系统进行电缆检测时入射和反射脉冲信号的幅值比较高,可能达到35 V,如果将此信号直接输入后续电路可能击穿元器件,因此必须对信号进行衰减。 由于检测系统所使用脉冲信号频带较宽具有较多的高频信号,在无源衰减电路中结合一般示波器探头的衰减网络设计原理[9],利用电容进行补偿。

衰减电路使用的电阻阻值常为兆欧级,脉冲信号经过无源电阻衰减电路后,电流很小,驱动负载能力很低,因此,常在后续电路中加入跟随缓冲电路,提高信号的驱动能力。

不同脉冲幅值经过衰减电路和跟随缓冲电路后的幅值不同,为了使后续的A/D 转换器(ADC)工作在合适范围内,需要对不同幅值的信号进行不同倍数放大处理。

多数高性能ADC 都利用差分输入来提高动态范围,抑制共模噪声和干扰,同时利用平衡信号来提高总体性能。 因此,设计单端转差分电路将输入的单端信号转换为差分信号以提高ADC 性能。

4 系统软件设计

4.1 检测系统NiosⅡ的应用程序设计

SOPC 系统是整个系统FPGA 部分的核心,而NiosⅡ软核处理器则为整个SOPC 系统的控制核心,用于处理并解析由检测系统控制部分发出的命令,并控制相应模块做出动作。

NiosⅡ软件主程序设计流程图见图8。 系统上电后,首先对FGPA 中自定义逻辑模块和各个IO 引脚进行初始化。 初始化结束后启动定时器,定时器用于控制FPGA 外围“心跳”指示灯。 其后进入主程序循环,首先进入SPI 接收数据读取函数,用于读取ARM 主机所发送的控制命令。 读取到的命令经过解析满足自定义要求后,依据命令进行相应的参数设置,产生脉冲信号并进行脉冲信号数据的采集,将所采集数据存入ADC 数据缓冲FIFO,FIFO 写满后将控制模块的准备发送标志位置位,等待主机进行SPI 数据读取,数据读取完成后,返回主循环进行下次的采集。

图8 NiosⅡ主程序流程图

4.2 Linux 驱动程序设计

Linux 系统中,用户空间程序若要访问或操作设备必须通过驱动进行,而无法直接与设备进行交互。 应用软件若需要操控硬件,必须通过调用系统所提供的应用编程接口(API)进行。 一般情况下,处理器出厂时厂商会配备相应的驱动程序,但由于该电路为自行设计,为了使系统更好地配合硬件电路,需要对板子上相应的外设设计驱动程序。 本工作以用于ARM 与FPGA 进行数据传输的SPI 驱动为例进行介绍。

在Linux 内核中,对SPI 驱动的软件架构进行了合理的分层和抽象,将SPI 子系统分为三部分:SPI 控制器驱动、SPI 核心、SPI 设备驱动,SPI 子系统架构示意图如图9 所示。

图9 SPI 子系统架构示意图

SPI 控制器驱动负责直接与具体的控制器硬件进行交互,按时序要求将SPI 设备驱动准备好的数据发送给SPI 设备,同时向上层的SPI 设备驱动传送设备所接收到的数据,控制器驱动常由处理器厂商提供;SPI 核心描述传输的数据结构,实现传输接口,降低SPI 设备驱动和控制器驱动的耦合程度;SPI 设备驱动程序依据硬件设备功能和协议格式,完成SPI 设备的具体功能。 SPI 子系统中SPI 设备驱动通常结合所使用的SPI 器件由设计者自行实现,考虑到SPI 通信必须要主机主动读取从机数据,因此,在本检测系统的SPI 设备驱动中加入GPIO中断处理函数,用于FPGA 准备好数据后通知ARM主机进行读取,SPI 设备驱动实现流程示意图见图10。

图10 SPI 设备驱动实现流程示意图

5 结束语

本工作分析了脉冲时域反射原理,结合嵌入式技术,设计了一套用于电缆故障测距的检测系统。系统基于ARM 和FGPA 搭建,设计了脉冲发生、信号调理采集和SPI 通信等硬件电路和逻辑,完成了NiosⅡ程序以及外围器件的Linux 设备驱动编写。实现了纳秒级别的可调脉冲输出、最高250 MHz 的信号数据采集以及电缆故障自动测距等功能,并通过实际电缆试验验证了系统的可靠性。