智能视力检查表电路设计

蒋 成,周春梅

(四川工商学院电子信息工程学院,四川 成都 611745)

1 智能视力检测系统的软件模块设计

1.1 软件设计方案

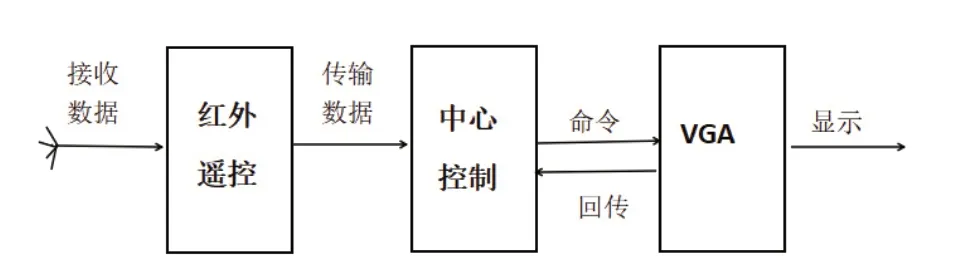

如图1 所示,软件设计同硬件设计一样,主分为三个模块,是属于整体设计的数字端,由红外遥控接收遥控器传输过来的数据,做转换,发给中心控制端,中心控制端做解析后,发给VGA 端,由VGA 接口将数据传到显示器,并显示E。

图1 软件设计方案流程图

1.2 算法设计

(1)算法模块

视力检测算法要求视力检测时,使用者根据自己观测到的视标开口方向提供反馈信息,FPGA 将对这些反馈信息进行记录和处理后,选择下一个E 视标进行显示。最后将这些结果进行整理得到最后的视力检测结果。反馈信息的处理和整理过程就是下面要介绍的视力检测算法。

(2)判断时间

在视力检测时需要使用者对判断方向提供反馈信号后再显示下一个信息,正常情况下,在进行视力检测时,从看到视标的那一刻起,人的大脑需要一段反应时间进行方向的判断,然后根据判断结果按下对应的方向按键。本设计就这段时间的长短进行了限制,使整个算法更为标准化和人性化,减少了人为误差。

如图2 中的延时计数器软件设计图所示的程序代码表示,延时为2 秒,意思是需要在使用者按下按键后进行下一个视标的显示,这段时间是由使用者的反应判断时间加上按键时间共同决定的。本设计将视标的显示时间设为2s,如果超出反应时间段后使用者仍然没有输入按键信息则认为使用者无法看清该视标[1]。

图2 延时计数器软件设计代码

1.3 红外遥控模块

(1)红外遥控模块整体设计

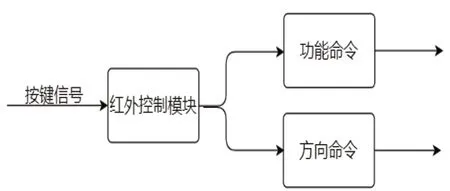

红外遥控模块的软件设计比较简单,只做数据接收和发送,如图3。

图3 红外遥控设计流程图

按键信号(key_flag)包括功能命令和方向命令数据,由NEC 协议传输到红外控制端,做数据解析,然后传给中心控制芯片。

(2)NEC 协议算法

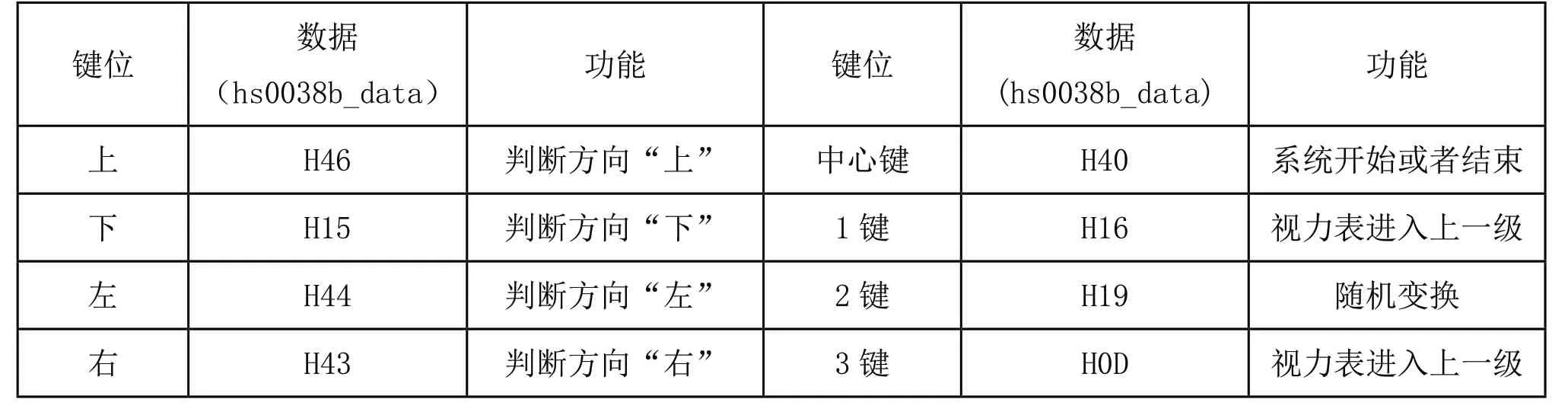

NEC 协议是红外远程控制控制最常用的传输协议之一。当遥控器按下按键时,会发出一帧的数据,这一帧的数据分别为引导码、地址码、地址码反码、数据码、数据码反码;然后由HS0038B 红外芯片接收。本次设计的遥控器所需的各个按键发送数据如表1 所示。

表1 遥控按键指示表

1.4 中心控制模块

(1)中心控制模块整体设计

如图4 中心控制模块是为FPGA 内部运算来控制,主要是分为判断模块、计数模块和随机数模块。

图4 中心模块控制流程图

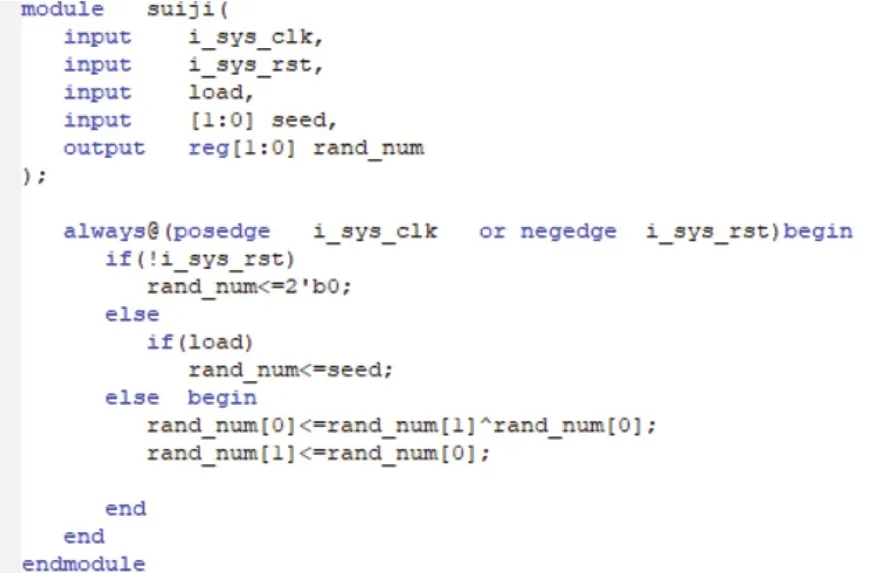

(2)随机数模块

在FPGA 的电路设计中,$androm 只能在仿真是运用,对于在系统综合是无法编译成功,而若是要是实现随机,只能运用伪随机法,伪随机法是属于长时间来看有周期性的随机算法。

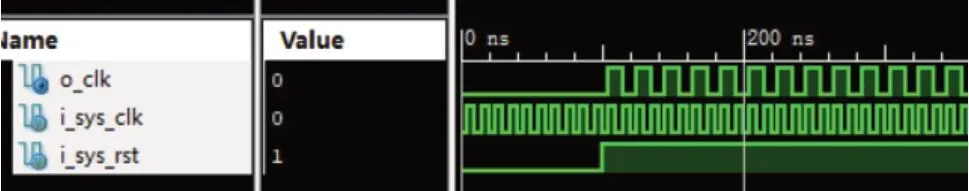

如图5,当给出load 信号后,由seed 左右种子数,然后rand_rom 循环移位,最后随机产生一个2 字节的数据,分别为00、01、10、11,每个字节生成的概率相等,本次设计给出,判断rand_num 的数据,定义rand_num=00 时视标“E”方向为上,rand_num=01时“E”方向为下,rand_num=10 时“E”方向为左,rand_num=11 时“E”方向为右,如表2。(3)用户判断模块

图5 随机数生成软件示意图

表2 随机数功能示意表

用户判断模块是一个比较复杂的模块,主要是需要根据用户按键判断的方向和视标“E”的方向是否匹配。由于红外遥控模块的NEC 协议传输的按键方向数据不是00、01、10、11,故此,在进行方向判断之前,需要将NEC 传数过来的数据做转换,转换方式为:将红外遥控模块的数据(hs0038b_data)进行判断,做一个按键判断寄存器(key_judge_buff),并由状态机来实现;

如图6 所示,当检测到发送数据完成(hs0038b_en=1)状态机进入1 状态,并且判断hs0038b_data的 值,为h46 时,key_judge_buff 赋值为00;表示方向判断为上,当为hs0038b_data=h15 时,key_judge_buff 赋值为01,表示方向判断为下;当为hs0038b_data=h44 时,key_judge_buff 赋值为10,表示方向判断为左;当为hs0038b_data=h43 时,key_judge_buff 赋值为11,表示方向判断为右;当给key_judge_buff 赋值后,状态机进入3 状态,为方向判断,判断语句为o_judge=key_judge_buff&&e_fx;表示当key_judge_buff和e_fx 相同时,o_judge=1,否则为0。

图6 用户判断软件示意图

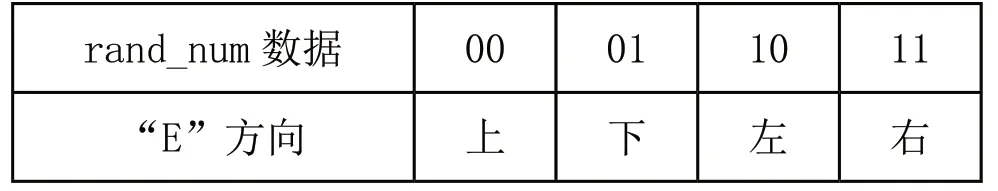

1.5 VGA 接口调用模块设计

需要显示的内容包括:E 视标、和最后的检测结果。设计程序按照功能分为时钟部分设计、VGA 驱动部分和VGA 显示控制部分3 个模块, 其模块划分结构如图7 所示。Div_2 是时钟分频模块,将50Mhz 的时钟作2 分频,分为25Mhz,以提供输入时钟和复位时钟。VGA_show 是显示模块。按时序描述VGA 显示内容,VGA_driver 是VGA 驱动电路,对时序及状态进行约束。

图7 vga 显示模块设计图

(1)分频模块设计

分频模块的设计是为了满足VGA 显示640×480分辨率所需时钟的25Mhz,而本次设计所采取的系统时钟为50Mhz,故此只需要将系统时钟进行二分频;

二分频极为简单,如图8 所示,当系统来一个时钟上升沿,clk_25Mhz 取反,并且,将clk_25Mhz 作为输出即可实现二分频。

图8 二分频软件示意图

(2)VGA 驱动模块设计

在前面第三章介绍部分讲了,VGA 若要实现显示,则需要将有效数据送到显示屏上,例如640×480 分辨率的VGA,其有效数据位是640×480,然而其实际数据长度为800×525,因此,需要将行计数器(h_cnt)和场计数器(v_cnt)的数据减去显示前沿和显示后沿;

如图9 所示,表示对行、场同步计数器计数,行同步计数器(h_cnt)计数到行同步周期800(H_TOTAL),场计数器计数到525(V_TOTAL)。

图9 VGA 驱动模块软件示意图

(3)VGA 显示模块设计

VGA 显示模块主要是接收来字随机数模块的数据和VGA 驱动模块的数据,并且调用内部rom IP 核,将rom 内部的数据传输给显示屏并显示出来。

如图10 所示,VGA 显示模块接收到来随机数,做相应的方向随机变化,接受到驱动模块的数据,显示再显示屏上。

图10 VGA 显示模块流程图

2 智能实力检测表测试

2.1 功能仿真测试

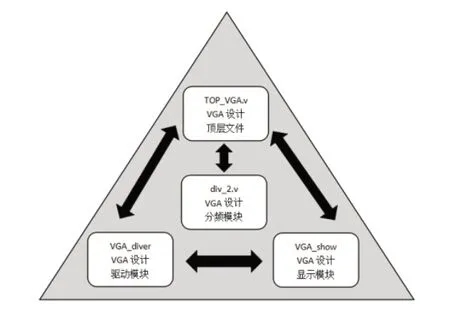

(1)时钟分频模块仿真测试

时钟分频模块是用来生成VGA 时序的,本次设计采用的VGA 分辨率是680*600,所需要的时钟是25Mhz 的时钟,即对50Mhz 的系统时钟进行二分频,将输出时钟o_clk 作为VGA 的时序时钟,其仿真图如下;

如图11 的仿真所示:当使能信号拉高后,每来一次系统时钟i_sys_clk 上升沿,o_clk 便拉高一次,而输出的o_clk 便是25Mhz 的时钟。

图11 时钟分频仿真图

(2)随机模块测试

随机数模块用来产生随机数的。每次产生的随机数都代表下一次视标的显示方向,为了保证显示视标符合随机显示的需求,需要一个随机数来确定方向。设计中定义了一个四位的循环移位寄存器,其中对这四位数据进行赋值,初始值为11,每次时钟信号上升沿到来后进行一次循环移位处理。其中对视标的四个显示方向分别定义为上:00,下:01,左:11,右:10。每次需要提取随机数进行下次视标显示时就对寄存器的后两位数值进行提取。提取的时间由手持端按键按下的时间决定,每个操作的人间隔时间都不相同,因此具有随机性。首先要证明上下左右的概率相同,都为1/4,这样才能满足各朝向数目均等的要求。其概率仿真图如图12 所示。

图12 随机模块仿真图

如图12 的随机模块仿真图所示,由seed 做为种子,通过循环移位后,再某个时钟就会得到随机数,而随机数作为VGA 显示模块随即便换的驱动。

2.2 功能测试

图13 初始界面显示

图13 显示视标“E”

初始界面显示为START,当JTAG 驱动之后,系统开始运作,显示器显示,如图12 所示的START。

如图14 显示的第一级时标“E”,是当测试者按下遥控器中心键后的显示。

图14 遥控按键判断图

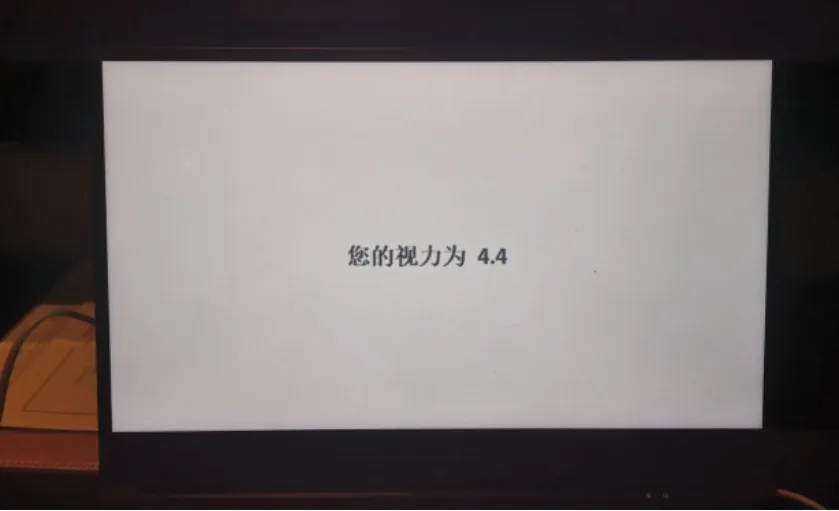

如图14 所示,为测试中按下遥控键的图,其中等亮表示此次判断正确。如图15 所示,为测试者再次按下遥控的中心键后的显示,当测试这第二次按中心键表示系统运作结束,并且显示测试者此次测试的视力数据。

图15 结束界面视图

3 结语

此次设计是一个基于FPGA 实现的智能视力检测系统,改善了传统的使用视力表检测时需要人工辅助的弊端,实现了更加智能人性化的视力检测过程。设计通过介绍标准对数视力表的优势和原理,说明了选择其作为智能视力测量参考的原因。然后按照设计流程,分几个模块对整个系统进行了从方案选择到软硬件设计实现的详细描述。显示端使用FPGA 作为控制核心,与液晶显示屏进行连接实现VGA 的显示,与无线接收模块相连接收发送的按键信息。模型系统在借助了开发板的情况下,实现了整个视力检测的模拟过程,并进行了仿真测试和整机实测。模型系统能够满足设计需求,取得比较满意的设计效果。

- 四川工商学院学术新视野的其它文章

- 基于教学数据实时跟踪的嵌入式课程教学探究

- 差旅费用报销系统构建成效

- The Application of PDCA Theory in Middle School English Teaching

——Taking Xijie Junior Middle School as an Example - 基于“新工科”理念下教学质量的提升手段

——以四川工商学院建筑工程学院为例 - Research on Translation Skills of News from Cross-cultural Perspective

——Taking the News Report of the Third Session of the 13th - CLIL教学法在初中英语阅读教学中的应用研究

——以邻水中学为例