新工科背景下数字电路案例教学

徐 辉

(安徽理工大学计算机科学与工程学院,安徽 淮南 232001)

2017年,我国提出“新工科”建设,着力培养面向未来、面向世界、引领未来的精英人才。通过实施“卓越工程师教育培养计划”,我国建成了规模庞大、门类齐全的工程教育体系,极大地支撑了国家社会经济发展[1-2]。通过开展“工程教育本科专业认证”,保证了工程教育本科教学质量。通过学习并实践“华盛顿协议”,既引导了高校按照国际标准培养高水平人才,又实现了工程师国际互认[3]。“数字电路”是计算机信息类专业的重要基础课。目前“数字电路”课程教学主要存在以下问题:过于重视传统知识的讲授,忽略了科技前沿对教学内容和教学手段的影响;课程独立性太强,讲授过程中与其他学科的交叉欠缺,课程学习片段化明显;课程实践过程采用传统教学模式,实践目标仍然以验证理论知识为主;学生被动接受知识的环节较多,探索性环节欠缺。针对以上问题,我们提出在“数字电路”课程教学中采用案例教学法,注意紧扣学科发展前沿,下面具体以数字电路老化教学为例进行讨论。

1 紧紧跟随科技发展,发掘前沿科学问题

传统数字电路中“二极管”、“三极管”知识点被删除,代之以CMOS集成电路。目前CMOS电路可靠性已经成为限制集成电路发展不可忽视的重要因素。对于65 nm及以下的集成电路,负偏置温度不稳定性(NBTI)已经成为影响电路可靠性的关键因素,严重影响了芯片的生命周期[4-5]。引导学生查阅文献资料,理解NBTI是一种主要作用于PMOS晶体管的老化效应,当PMOS的栅极处于负偏置时,PMOS的阈值电压就会随着电路工作时间的增加而不断升高,进而导致逻辑门的传输时延增大,降低了电路性能,最终可能会导致电路发生时序违规。因此,探讨NBTI的老化效应并进行精准的预测和防护具有重要意义。通过文献调研,同学们了解到当前的NBTI电路老化研究工作大致可以分为两个阶段:硅前阶段,对NBTI效应进行物理建模和老化预测分析[6-8];硅后阶段,对芯片的老化情况进行在线监测[9-10]及NBTI相关的电路优化技术[11-14]。对于该问题的解决手段,同学们总结了两种优良的解决方案:文献[15]提出了利用MDS(Maximum Dynamic Stress)老化分析方法来预测NBTI效应导致的时延增加,该方法将所有逻辑门的输入节点占空比都统一设定为0.95,忽略了电路逻辑门之间的拓扑关系,对于老化时延的预测过于悲观;文献[16]提出了一种基于静态时序分析的识别NBTI老化效应下关键门和关键路径的方法,该方法仅仅通过路径上的单个逻辑门的老化时延和时序约束进行比较来识别关键门,缺乏对于同一时序路径下其他逻辑门影响的考虑,在识别的精度上有待提高。针对这两种方案的缺点,提出学习任务。

2 牢牢掌握基础理论,结合数学知识解决模型问题

对于NBTI引起的时延,敦促学生从工程角度考虑问题,从数学角度解决问题,掌握精确的NBTI数学模型对于时延预测的作用。NBTI预测常用的是R-D(Reaction-Diffusion)模型,它将NBTI的老化过程分成反应阶段和扩散阶段两部分。在反应阶段,界面陷阱的产生速率与工作时间呈线性关系。随后的扩散阶段,氢原子结合成氢分子并以tn的时间依赖关系从界面向氧化层扩散,对于氢分子而言,n一般取0.16。界面陷阱的产生模型为

其中,kF是正向反应速率,kR是逆向反应速率,N0是初始时刻界面陷阱的密度,DH是氢的扩散系数[6]。在NBTI的长期老化预测模型中阈值电压增量与工作时间、占空比等因素的关系[17]为

其中,K是与电场、温度和载流子浓度等相关的参数;n为时间系数,当扩散模型为氢分子的时候取0.16[6];α为输入信号概率,表征PMOS管在一段工作时间内负偏置的时间比例;Tclk为时钟周期;β为与时钟周期、工作温度以及工艺参数相关的系数。在特定工艺参数下阈值电压增量简化公式为[18]

其中,A为环境和工艺参数,t为电路的工作时间。研究表明,NBTI老化效应下逻辑门的传播时延增量与阈值电压增量ΔVth可以表示为一阶线性关系[19]:

其中,B是与环境因素和逻辑门工艺相关的常数,可以通过对逻辑门的老化数据进行拟合得到。

3 有效利用算法知识,设计解决框架

学生在教师指导下,结合数据结构与算法知识,提出了一种准确识别NBTI效应下老化敏感的关键门算法流程:首先,对标准逻辑门单元进行NBTI老化时延模型抽象分析;然后,通过建立动态占空比模型分析所有内部节点的占空比信息,得到具体的老化时延信息;最后,将关键门的识别分类,第1部分通过时序约束和逻辑门的老化识别出初始关键门,第2部分充分考虑同一条时序路径其他逻辑门发生严重时序违规造成的影响,识别出需要进行老化防护的实际关键门。

这样,同学们提出的算法流程就充分考虑了电路中逻辑拓扑结构引起的逻辑门之间的逻辑功能和占空比约束,并考虑在识别关键门过程中可能出现的特殊情况,在进一步提高对关键门识别精度的同时,减少了最后识别出的关键门数量。毫无疑问,结合数学知识、数字电路知识、算法知识等解决了实际工程问题,极大地提高了同学们的学习兴趣。

3.1 考虑NBTI老化效应的静态时序分析算法框架

结合文献[20-21],学生设计出考虑NBTI的静态时序分析流程,如图1所示,有关定义如下。

图1 算法流程

定义1初始关键门:电路中经过了一段工作时间之后因受到NBTI的影响而导致经过该逻辑门的时延超过了原先设计阶段预留的时间余量,则称该逻辑门为一个初始关键门。

定义2实际关键门:在初始关键门的集合中,如果当前的初始关键门发生了严重的时序违规,并导致同一条时序路径上的其他逻辑门发生时序违规,则称该初始关键门为一个实际关键门。

具体算法流程:(1)利用电路综合出的电路网表,结合工艺参数以及初始的模型参数信息,建立整个电路的逻辑拓扑结构;(2)根据整个电路的逻辑拓扑结构,结合输入输出信息,计算出受到NBTI老化之前的时延信息;(3)根据占空比模型,在给定输入信号占空比的情况下,对所有逻辑门工作时的动态占空比进行计算,并将结果作为预测NBTI老化的重要参数;(4)通过NBTI的老化模型对电路中所有逻辑门的老化时延进行预测,并确定在给定的时序余量之下出现时序违规的逻辑门,将它们作为初始关键门;(5)通过算法计算所有初始关键门是否会对同一条时序路径下其他初始关键门的时序违规产生重要影响,得出实际关键门。

3.2 电路逻辑拓扑结构

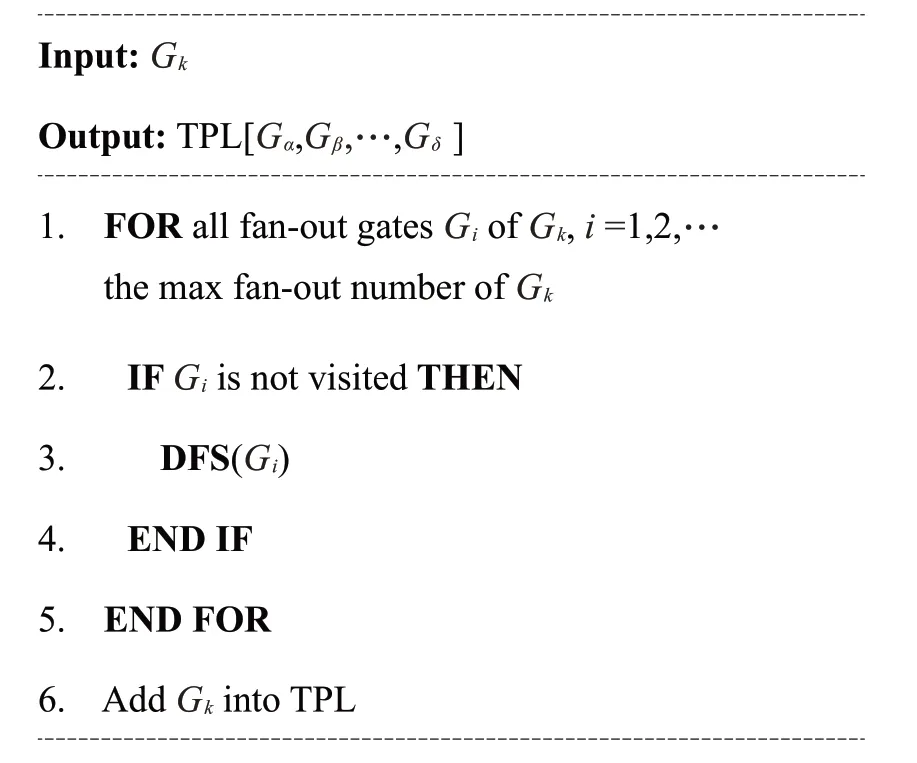

对于一个给定的电路网表文件,其中可能包含大量触发器和逻辑门,在对电路进行分析之前,需要先建立起电路整体的逻辑拓扑结构。拓扑排序是算法课程的重要知识点,同学们结合文献[22-23]采用了深度优先搜索算法来对电路进行拓扑排序,如算法1和算法2所示。

算法1:Topo_Sort

算法2:DFS

3.3 根据逻辑占空比识别关键门

老化逻辑占空比在NBTI导致的老化问题研究中,占空比指PMOS晶体管处于负偏置的时间占电路所有工作时间的比例[24]。从统计学角度来看,占空比可以看成整个工作时间内电路节点输入信号为零的概率。由式(4)可知,NBTI导致的老化延迟与逻辑门输入信号占空比存在函数关系。根据初始输入信号的占空比动态计算出所有节点的占空比,用于准确预测NBTI老化效应导致的延迟。同学们利用概率论知识,结合算法1、2的占空比传播公式[25]计算出了电路中所有节点的占空比,如表1所示。

表1 几种基本逻辑门的占空比传播公式

将电路NBTI老化效应下的关键门识别分为初始关键门识别和实际关键门识别。

初始关键门识别由逻辑占空比模型可得出电路中逻辑门Gk的输入信号占空比d(Gk),结合式(4)可以得到实际NBTI老化:

其中,ΔD(GK)表示逻辑门GK的NBTI老化,B是工艺环境相关的系数,t为工作时间,n对于氢分子取0.16,Δp为预测误差的常数项。

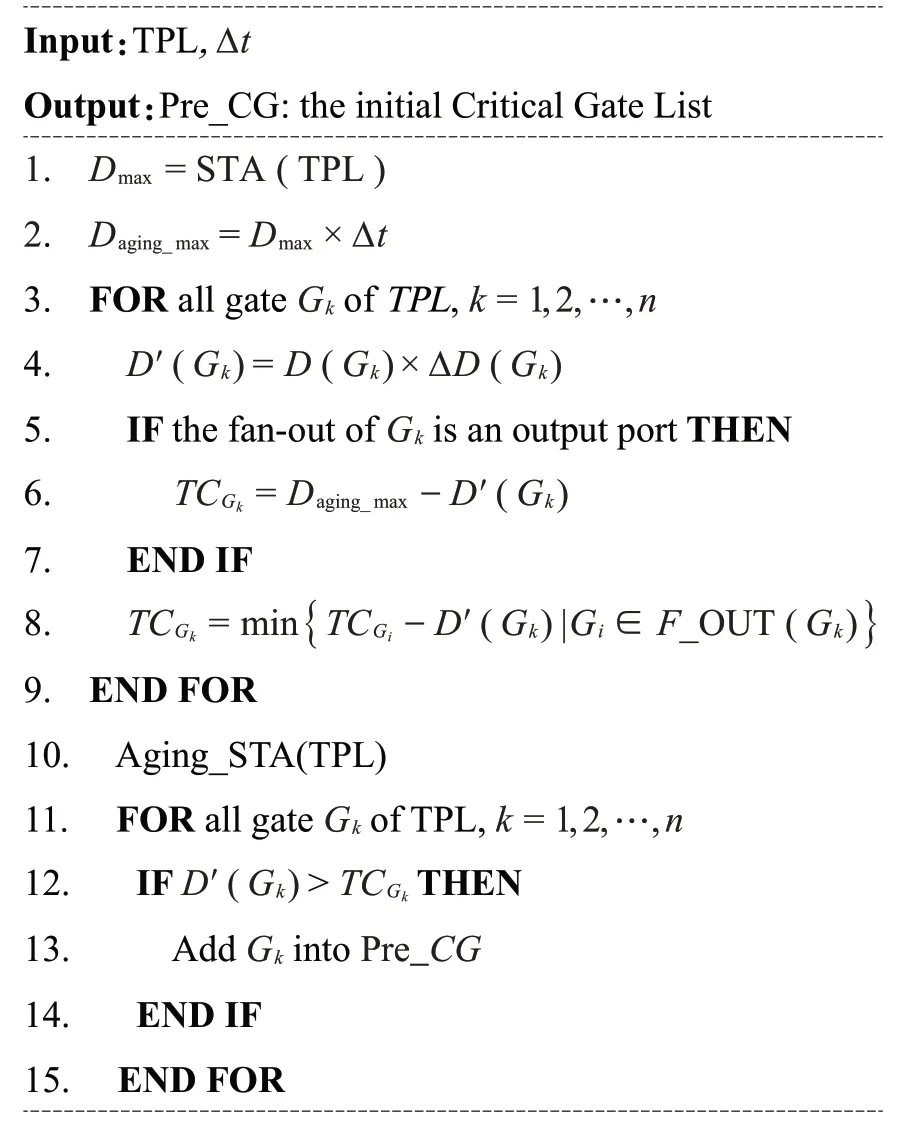

确定初始关键门步骤:(1)通过3.2中所有逻辑拓扑列表TPL对整个电路进行老化前的STA,得到各个逻辑门的延迟D(GK),并计算出整个电路中所有输出的最大延迟Dmax(其中D触发器的输入端作为伪输出端参与计算);(2)由未老化的最大延迟Dmax和设定的时间余量系数Δt推导出老化后电路的最大时序延迟Daging_max;(3)根据所有逻辑门的延迟D(GK)、NBTI效应下的老化系数ΔD(GK)和输出端最大时序延迟Daging_max从输出端逆向计算每个逻辑门在经过NBTI老化之后的时序约束TC(GK)(Timing Constraint);(4)由逻辑拓扑列表对整个电路进行NBTI老化效应的静态时序仿真,挑选出所有超过时序约束的逻辑门作为初始关键门。具体见算法3。

算法3:CG_Selection

算法3中的符号说明:TPL,电路逻辑门拓扑列表;Δt,设计阶段预留的时间余量系数;Dmax,老化前电路输出端的最大时延;STA,静态时序分析算法;Daging_max,老化后电路输出端的最大时延;D(GK),逻辑门GK老化前的时延;ΔD(GK),逻辑门GK受NBTI老化效应影响的老化系数;D′(GK),逻辑门GK老化后的时延;TCGk,逻辑门GK在老化后的时序约束;F_OUT(GK),逻辑门GK的所有扇出逻辑门集合;Aging_STA,老化后的静态时序分析算法;Pre_CG,初始关键门集合。

实际关键门的识别在完成初始关键门的识别后,仍需要对Pre_CG中的初始关键门做进一步的筛选,从而得到实际关键门。算法3关键门的识别方法过于粗糙。电路经过算法3识别之后可以发现某条路径上的逻辑门发生了时序违规。但是若作为伪输入端的D触发器时序路径在开始处就发生了时序违规,就可能会出现特殊情况:如果前面逻辑门的时序违规过大,而后面的几个逻辑门对NBTI老化效应并不敏感,但是因为电路时延传递的原因,导致后面的所有逻辑门都发生了时序违规。这种特殊情况对NBTI老化防护可能会带来影响。如果仅仅是因为前一级的延迟过大,那么在进行防护时仅仅需要对一个逻辑门进行防护,而不需要对原先时序路径上的所有逻辑门进行老化防护,这样可以大大减少老化防护的开销。真正需要进行防护的逻辑门就是该论文中的实际关键门。

针对上述特殊情况,同学们通过修改算法思想,从初始关键门集合Pre_CG中识别出实际关键门,并采取以下两个策略:a)如果一个初始关键门的扇入中存在另一个初始关键门,并且其时序违规超过当前初始关键门的时序违规,则当前关键门为一个实际关键门;b)如果一个初始关键门的扇入中存在另一个初始关键门,并且其时序违规超过所有初始关键门的时序违规平均值,则当前关键门为一个实际关键门。对于Pre_CG中的任一初始关键门,如果能够同时满足上述两个条件,则可以把该关键门视为一个实际关键门。

4 实验结果和分析

数字逻辑作为重要的专业课,需要不断改革和优化传统实验,以适应新工科发展的需要。同学们根据文献要求,选用了数字电路EDA工具进行了仿真实验。首先采用Design Compiler对电路进行综合分析,再将HSPICE中得到的各个逻辑门老化数据进行拟合,得到工艺环境相关参数B和常数项误差Δp,拟合部分是通过MATLAB R2016b中的Curve Fitting工具箱来实现。这部分工作量大、工作平台多,要求同学们通力配合,才能准确获取各种数据。

算法部分的实现,充分考虑高级语言程序设计专业课。基于VS2017实验平台,将上述各种仿真工具得到的各项参数通过C++读取,实现对电路网表的读取和转换及时序电路组合化。同学们用C++实现了对老化前的静态时序分析(STA)、动态占空比分析(DC_Analysis)、老化后的静态时序分析(Aging_STA)、初始关键门选取(CG_Selection)以及实际关键门识别(CG_Recheck)。

经过实验分析,研讨小组得到所提方案,并与国际主流方案进行对比,得到时序余量系数为10%,经过10年NBTI老化的情况方案在不同电路中识别的关键门数量,对比结果如表2所示。表2中第1列和第2列分别表示电路的名字和对应的逻辑门总数(包括D触发器),第3列到第5列分别表示了本文方法和文献[15]、文献[16]识别出的关键门数量,第6列和第7列分别表示本文结果同文献报道的结果相比的相对减少百分比。

表2 不同方法识别的关键门数量比较

与文献[15]相比较,同学们采用了更加精确的预测模型,将初始输入信号的占空比全部设定为0.95,而其内部节点的占空比遵循电路的逻辑功能,动态地通过计算节点的占空比预测。从表2结果来看,研究小组能够在更加精确合理地识别出关键门的同时,也大大减少了关键门数量,比文献[15]的结果平均减少了35.67%。与文献[16]相比较,同学们在逻辑门与时序约束的大小关系基础上,将关键门的识别步骤细化,进一步加入了对于同一时序路径中部分关键门可能出现严重时序违规情况的考虑,从而识别出在初始关键门集合中真正需要进行防护的实际关键门。相比于文献[16]中的识别方法,同学们的方法同比减少了25.28%的关键门数量。

5 结束语

综上所述,本文以“数字电路老化研究案例”为例,讨论了数字电路案例教学的实施策略。该案例考虑了学科前沿、多学科交叉和学生意愿,充分调动了学生的积极性。在“新工科”背景下,基于培养合格工程师要求,可以在数字电路教学中使用案例教学方法。对于数字电路学科中的电路老化这一前沿课题,我们将数字电路、数学、高级语言程序设计以及算法知识相结合,有效地解决了这一难题,极大地提高了学生的学习兴趣,激发了学生对于未知世界的探索欲望。