基于FPGA的移相时钟数字内插TDC电路设计与实现

刘景岩,路美娜,王羿,蔡伟杰,宋茂新∗,洪津

(1中国科学院合肥物质科学研究院安徽光学精密机械研究所,中国科学院通用光学定标与表征技术重点实验室,安徽 合肥 230031;2中国科学技术大学,安徽 合肥 230031)

0 引 言

为了进一步提高PM2.5等气溶胶污染物的遥感监测精度,中国科学院安徽光学精密机械研究所与数字地球研究所联合提出了基于“偏振交火”测量方案的大气颗粒物监测仪(Particulate matter polarimetry suis,PMPS)[1]。PMPS由高精度偏振扫描仪(Particulate observing scanning polarimeter,POSP)与多角度偏振成像仪(Directional polarimetric camera,DPC)组成,通过“偏振交火”将POSP的高精度数据传递给DPC进行交叉定标,以提升DPC数据精度[1]。航天器在发射之前需要经过一系列复杂的地面检测[2,3],针对“偏振交火”要求的POSP和DPC两台载荷之间时序信号的严格同步性,需要采用地面检测系统的时间数字转换电路(Time-to-digital converters,TDC)对时序信号同步关系进行验证。

高精度的TDC电路常用于定位定时、激光测距、原子物理等领域[4,5]。现有的测量方法包括直接计数、时间-电压转换、延迟线内插等方法[6]。直接计数法是使用待测信号作为计数器的起止标志,对待测间隔直接测量,这种方法一方面会有固定的±1周期的量化误差,另一方面高频率的时钟对时钟质量、功耗、器件速度等级提出了更高的要求[7];时间-电压转换方法采用电容充放电的原理对直接计数的量化误差部分进行细分,既保证了量程又提高了测量精度[8],但模拟电路对环境非常敏感,且容易产生非线性误差;延迟线内插技术在FPGA与专用集成电路(Application specific integrated circuit,ASIC)时间间隔测量设计中应用广泛,利用门电路等作为延迟单元,线性好,精度高,高等级器件最高测量精度可以达到数十皮秒[9],但不同器件制作工艺以及软件编译的差别较大,每次设计需要重新进行标定[10],使得延迟线技术设计灵活性和移植性都较差。

鉴于以上问题,本文结合地面检测系统的设计要求,设计了一种基于移相钟数字内插的TDC电路。该电路具有精度高、灵活性与移植性好、设计便捷等优点。

1 系统设计与实现

1.1 地面检测系统

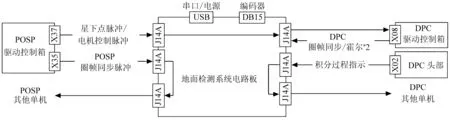

在PMPS工作原理中,POSP星下点采样间隔恰好为DPC两帧图像采集周期,所以在电子学设计中,为确保“偏振交火”定标效果,DPC图像采集须同步于POSP驱动控制箱星下点脉冲。为验证POSP和DPC两载荷之间数据采集的同步性,设计了一套地面检测系统,对相关的同步时序信号进行实时检测与评估,待测信号和整体设计如图1所示。

图1 地面检测系统Fig.1 Ground test system

系统位于载荷信号传递线路中间,作为转接板连接各路信号。电机控制脉冲等同步信号由POSP与DPC各工作单机产生,经过地面检测系统传递到其它单机,在此期间,各路信号被捕获与测量。测量结果与脉冲对应编码器信息通过串口传输到上位机。PMPS的数据采样周期以纳秒为单位,细微的误差即可能影响到定标数据的视场匹配结果,同时,系统信号通道和待测数据较多,因此测量电路在高精度的条件下必须灵活性好且资源占用率低。所以,设计了基于移相时钟数字内插技术的TDC电路。

1.2 数字内插技术原理

传统的直接计数法在对时序信号进行测量时,在时钟上升沿附近会产生最大1个时钟周期的量化误差,如图2所示。

图2 直接计数法Fig.2 Direct counting

实际值与测量值的误差ΔT为

式中ΔT1为测量起始位置量化误差,ΔT2为测量停止位置量化误差。

数字内插技术采用兼顾大量程的“粗”测量与高精度的“细”测量结合的方式,使用直接计数的方式获得“粗”时间,然后通过一组移相时钟将一周期细分成2N份(N为移相时钟个数),等效于获得了计数时钟的2N倍频,如图3所示。

图3 数字内插法Fig.3 Digital interpolation technology

在图3中,Clock 0为计数时钟,Clock 1、Cock 2分别相对于Clock 0移相π/3、2π/3,在待测信号跳变沿到来时刻,一个时钟周期内可以产生6种不同的电平状态组合,再通过查找表获得组合相对应的“细”测时间t1、t2。此时,测量值 T0为

式中T1为“粗”测量值,t1为测量起始位置“细”测量值,t2为测量停止位置“细”测量值。

实际值与测量值的误差ΔT为

式中Δt1为测量起始位置“细”测量值与实际值误差,Δt2为测量停止位置“细”测量值与实际值误差。

1.3 测量电路实现

测量电路采用Intel公司Cyclone IV E系列FPGA器件进行验证,该系列FPGA采用60 nm低功耗工艺,内核电压最低至1 V,同时有充足的逻辑和时钟管理资源,适合应用在有低功耗和低成本要求的场合。

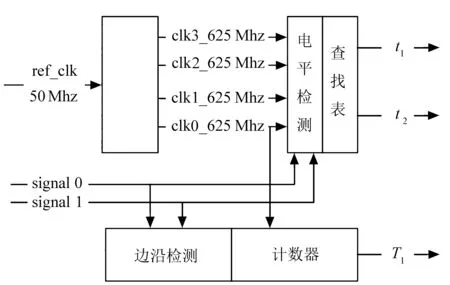

数字内插测量电路分为“粗”测与“细”测两部分。“粗”测部分包括边沿检测、锁相环(Phase locked loop,PLL)倍频、计数器等组件,首先通过PLL对FPGA输入50 MHz参考时钟进行倍频,得到625 MHz计数时钟,然后对待测时序信号Signal 0、Signal 1进行边沿检测,作为计数器的起止标志。“细”测部分使用4路移相时钟,每路相差π/4相位,相当于把计数时钟测量精度提高了8倍。测量电路结构如图4所示。

图4 测量电路Fig.4 Measurement circuit

在Signal 0、Signal 1边沿将4路移相时钟电平状态组合锁存起来,然后通过查找表获得“细”测时间,状态组合对应的“细”测时间如表1所示。

表1 “细”测时间查找表Table 1 “Fine”measurement lookup table

计数时钟经过分相后,4路时钟信号由全局时钟网络进行传输,保障时钟之间的延迟误差最小,“细”测时间分辨率理论上可以达到0.2 ns。“粗”测计数器位数决定着测量电路的量程,可根据设计需要灵活调整。

2 测试与分析

2.1 测量不确定度定义与测试

测量不确定度是评定测量结果的一个重要指标[11]。测量不确定度表征着测量结果的分散性,不确定度越小,测量结果分散性越小,反映其测量水平越高。在只考虑由重复性引起的测量不确定度的前提下采用A类评定方法,即通过对一系列的观测数据进行统计分析来评定,并利用贝塞尔公式计算不确定度,即

式中σ为测量不确定度,xi为单次测量数据,为n次测量数据的算术平均值。

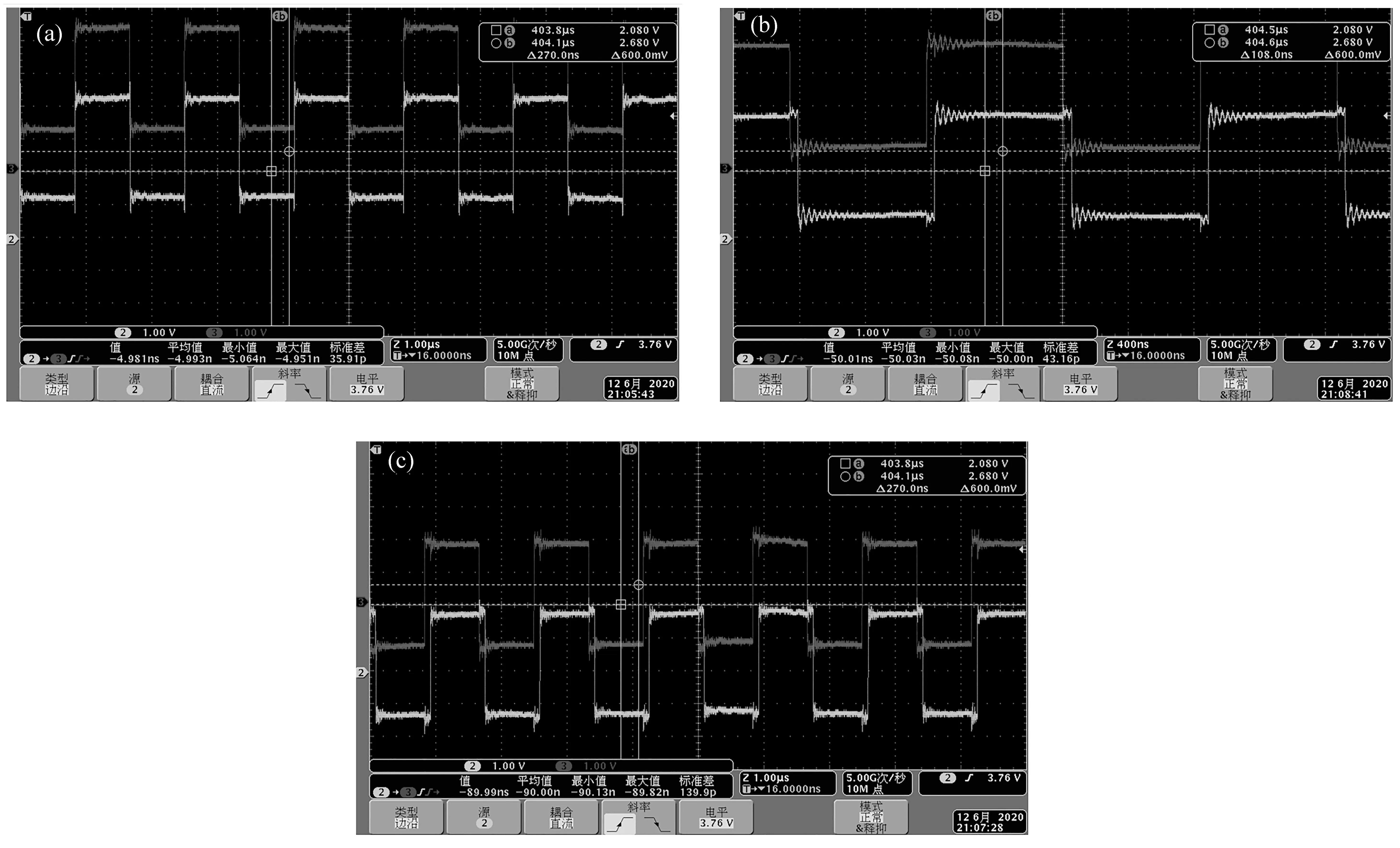

待测时序信号由剩余的PLL资源生成,通过FPGA内部延时单元产生待测时间间隔,然后由全局时钟网络输出,PCB严格等长走线,这样保证了待测信号时序的准确性。采用示波器(采样率5 GHz,带宽1 GHz)对待测信号时间间隔进行验证。在PMPS的时序设计中,5、50、90 ns是常见的时间间隔,因此选其作为实验样本值,每个值进行1000次的重复测量。示波器对信号的时间间隔验证、数字内插法与直接计数法测试结果对比如图5–8所示。

图5 示波器对不同时间间隔信号的验证。(a)5 ns;(b)50 ns;(c)90 nsFig.5 Oscilloscope validation of signals at different time intervals.(a)5 ns,(b)50 ns,(c)90 ns

可见,通过FPGA内部延时单元产生的待测信号时序准确,但随着时间间隔变长,稳定性有所下降。直接计数法结果总是含有±1周期的量化误差,而数字内插技术大体满足分辨率预期,但仍存在少量异常值。

图6 数字内插法(a)与直接计数法(b)对5 ns时间间隔信号测试结果Fig.6 Test results of 5 ns time interval signal by digital interpolation(a)and direct counting(b)

图7 数字内插法(a)与直接计数法(b)对50 ns时间间隔信号测试结果Fig.7 Test results of 50 ns time interval signal by digital interpolation(a)and direct counting(b)

图8 数字内插法(a)与直接计数法(b)对90 ns时间间隔信号测试结果Fig.8 Test results of 90 ns time interval signal by digital interpolation(a)and direct counting(b)

2.2 误差分析与处理方法

TDC电路主要误差来源包括量化误差、时钟抖动等,以及在上述测试中出现的异常值情况。经过分析,其原因在于待测时序信号上升沿锁存分相时钟电平状态时,恰好碰到计数时钟边沿,造成了一个时钟周期的计算误差。此类误差可以通过多次测量取平均数或中位数来降低,两种方法处理后三次测试数据对比如图9–11所示。处理前后的测试数据经测量不确定度分析结果如表2所示。

图9 平均数处理(a)与中位数处理(b)后5 ns时间间隔信号测试结果Fig.9 Test results of 5 ns time interval signal after average processing(a)and median processing(b)

表2 测量不确定度分析Table 2 Test uncertainty analysis

图10 平均数处理(a)与中位数处理(b)后50 ns时间间隔信号测试结果Fig.10 Test results of 50 ns time interval signal after average processing(a)and median processing(b)

图11 平均数处理(a)与中位数处理(b)后90 ns时间间隔信号测试结果Fig.11 Test results of 90 ns time interval signal after average processing(a)and median processing(b)

分析可知,直接使用数字内插技术获取的测试结果测量不确定度小于0.2 ns,平均数与中位数处理均可以避免随机误差导致的异常值出现,测量不确定度减小到0.1 ns以下。同时还发现,随着样本值的增大,测量不确定度也逐渐上升,经分析是因为待测信号稳定性降低,所以内部延迟单元产生信号源不适合较大样本值的测试。

3 结 论

采用FPGA中PLL资源对地面检测系统中时序信号测量电路的时钟进行倍频与移相,实现了基于移相时钟数字内插技术的TDC电路,并获得了0.2 ns的分辨率,检测精度高、灵活性好、占用资源少,满足了航天载荷之间同步信号测试的性能要求。此外,最小分辨率主要受到FPGA器件等级的限制,在更高要求的使用场合中,使用更高等级的器件将获得更高的精度。