一种超低输入共模电压的动态比较器电路设计

杨德旺,张春华,郭春炳

(广东工业大学 信息工程学院,广东 广州 510006)

0 引言

随着物联网低功耗应用的逐渐兴起,系统供电电压逐渐降低,要求便携式设备和无线传感器网络能够在电源电压和输入共模电压都更低的条件下正常工作。比较器电路是SAR ADC 等电路系统中的关键电路模块,其性能的好坏对系统有重要的影响[1-6]。

常用的比较器包括开环比较器和动态锁存比较器。动态锁存比较器相较于开环比较器具有无静态功耗、速度较快和精度较高等优点,因此取得了更广泛应用[7-8]。

StrongARM 比较器具有低功耗的优势,但分辨率较低,且输入共模范围较小。DoubleTail 比较器的分辨率和输入共模范围相比于StrongARM 比较器有了一定的提高,但代价是更高的功耗,尤其当输入电压较低时会发生漏电,造成功耗急剧增加。因此设计一种同时满足低功耗、高分辨率和宽共模输入范围的动态比较器具有较强的实用意义[9-11]。

本文首先分析了StrongARM 比较器[12-14]和DoubleTail比较器[15]的结构特性和限制因素,接着阐述本文提出的一种适用于超低输入共模电压的动态比较器的工作原理和设计要点,最后对电路仿真结果进行讨论。

1 电路设计

1.1 StrongARM 比较器

StrongARM 比较器的优点包括:(1)它消耗零静态功率,(2)它直接产生轨到轨输出,(3)它的输入参考偏移主要来自一个差分对。

其增益主要来自输入对管,近似于:

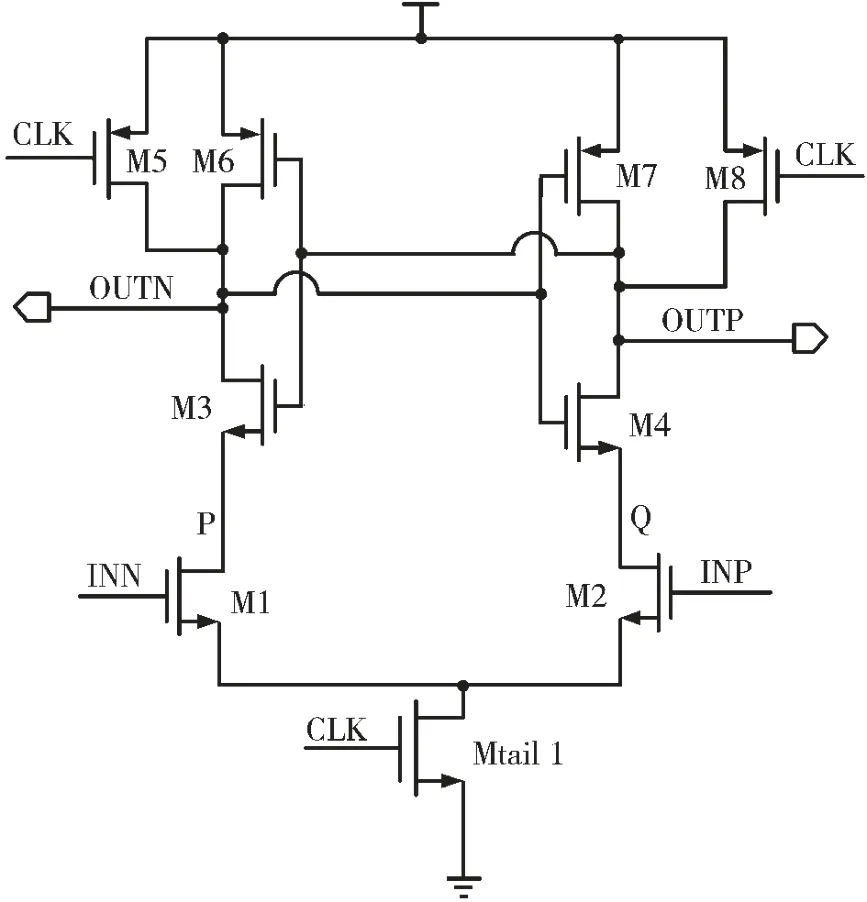

如图1 所示,当CLK 为低时,M5、M8 导通,Matil 1关断,对OUTN 与OUTP 进行复位操作,当CLK 变为高时,StrongARM 比较器进入比较阶段,通过输入对管M1、M2进行放电,直到VP 与VQ 小于VDD-VTHN,M3、M4 打开,并通过M3、M4、M6、M7 形成正反馈,最终形成高低电平输出。

图1 StrongARM 比较器

由于从4 级MOS 管堆叠,需要很大的电压余量,这在低电压深微米CMOS 技术中存在问题,提升了对最低电源电压的要求,从而导致功耗增大。当输入共模电压低于MOS 管的阈值电压时,输入对管会关断电流泄放路径,其比较器延时明显增大,不能正常工作。

1.2 DoubleTail 比较器

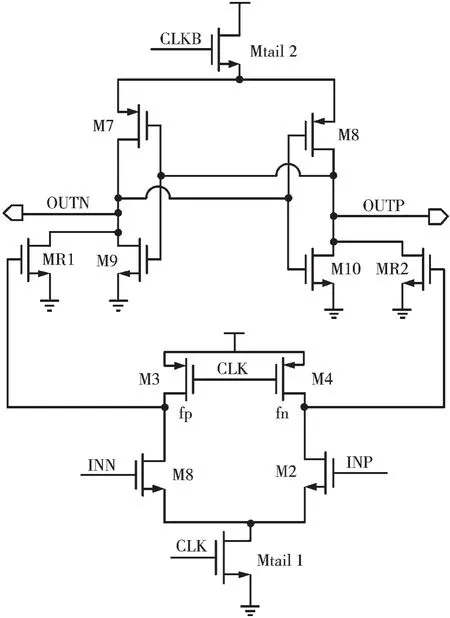

传统的DoubleTail 比较器如图2 所示,其工作原理如下。

图2 传统双尾比较器

复位阶段:当CLK 为0 时,Mtail1、Mtail2 断开,M3、M4 闭合,从而fn=fp=VDD,进而OUTP=OUTN=0。

再生阶段:当CLK 为1 时,Mtail1、Mtail2 闭合,M3、M4 断开,如果INP>INN,fn=0 且fp=1,从而MR2 断开,MR1 闭合,继而M10 断开,M8 闭合,进而OUTP=VDD。如果INN>INP,fn=1 且fp=0,从而MR2 闭合,MR1 断开,继而M9 断开,M7 闭合,进而OUTP=VDD。

它使用一个尾管作为输入级预放大,另一个尾管作为锁存级。从VDD 到地需要三级MOS 管堆叠,较StrongARM 减少一级。然而当输入共模电平低于阈值电压时,输入对管M2、M8 会进入亚阈值导通甚至不导通状态。这导致在再生阶段(CLK 为1),fp 与fn 不能下拉到地,从而使得MR1 与MR2 一直处于导通状态,形成电源到地的电流通路,发生漏电现象,继而使OUTP 与OUTN 一直处于低,影响比较器正常工作,造成功耗急剧增加。

1.3 提出的双环路动态比较器电路

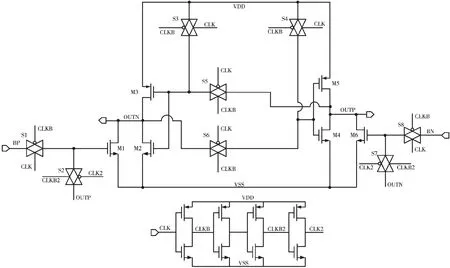

本文提出的动态比较器如图3 所示,包括输入差分对M1、M6,采用S1-S8 传输门作为开关,用于控制电路的时序,每个时序开关中均具有两个反向时钟,分别通过接收不同的时钟信号CLK、CLKB 来控制时序开关的通 断。M2、M3、M4、M5 构成一个正反馈回路,M1、M5、M6、M3 形成另一路正反馈回路。有效增大其增益,进而提升其分辨率,其等效增益约为:

图3 本文提出的动态比较器

在时钟信号CLK、CLK2 为高时,时钟信号CLKB、CLKB2 为低,比较器 进入复位阶段。S1、S8 闭合,S2、S7断开,将输入保存在M1、M6 的栅极寄生电容处。同时,S3、S4闭合,S5、S6断开,将M2 至M5 的栅极拉到电源VDD,则M3、M5断开,M2、M4闭合,将OUTP、OUTN 拉到地端。

接着进入再生阶段,时钟CLK 变为低,CLKB 变为高,则S1、S8 断开,断开M1、M6;同时,S3、S4 断开,S5、S6 闭合,其中M2、M3、M4、M5 构成一个正反馈回路。随后CLK2 变为高,CLKB2 变为低,将输出OUTP、OUTN 接入M1、M6 栅极,其中M1、M5、M6、M3 形成另一路正反馈回路,OUTP、OUTN 在复位阶段为低,时钟从低变到高的过程中,由于输入BN、BP 的不同,会让M1、M6 开关程度不一致,继而细微影响OUTP 与OUTN 的变化,进而经过正反馈,影响最终OUTP 与OUTN 输出值,并形成一高一低两个电平输出。

值得注意的是,因为比较器输入差模信号一般都较小,为防止上一次比较的结果的大信号OUTP 与OUTN 对下一次输入的影响,因此先让S1、S8 导通接入信号,以形成有效的初始值,而后再通过CLK2、CLKB2 让S2、S7导通,让OUTP、OUTN 接入反馈回路。

因为该电路在比较阶段,引入两级反馈,且从电源到地只有两级MOS 管,最低电源电压只需要2VDS,使该电路具有更大的电压裕度。在输入共模电压低于阈值电压时,因为输入信号仅通过一级输入对管M1、M6 接入反馈回路,依然可以影响输出信号,因此比较器可正常工作。

2 电路仿真与分析

基于TSMC 0.18 μm 1P6M 混合信号工艺,采用Cadence Spectre 软件对三个比较器进行设计和仿真。为了便于性能对比,图1~图3 的MOS 管均采用最小尺寸,NMOS、PMOS 均宽为2 μm,长为180 nm。

对三个比较器进行瞬态仿真,电源电压为1.8 V,INN为100 mV~300 mV 斜坡信号,INP 为300 mV~100 mV 斜坡信号,时钟信号为1 MHz,仿真结果如图4 所示,本设计比较器依然能够实现比较功能。而StrongARM 已完全不能建立正确的输出,DoubleTail 在ΔVin为86 mV 以下也已不能建立正确输出。进一步通过参数仿真,在电源电压为900 mV,差模电压为1 mV 情况下,本文提出的比较器最低共模电压为51 mV,与传统StrongARM 动态比较器和DoubleTail 动态比较器相比,分别降低了374 mV和264 mV,仿真结果显示本设计具有更大的输入范围。

图4 瞬态特性仿真结果

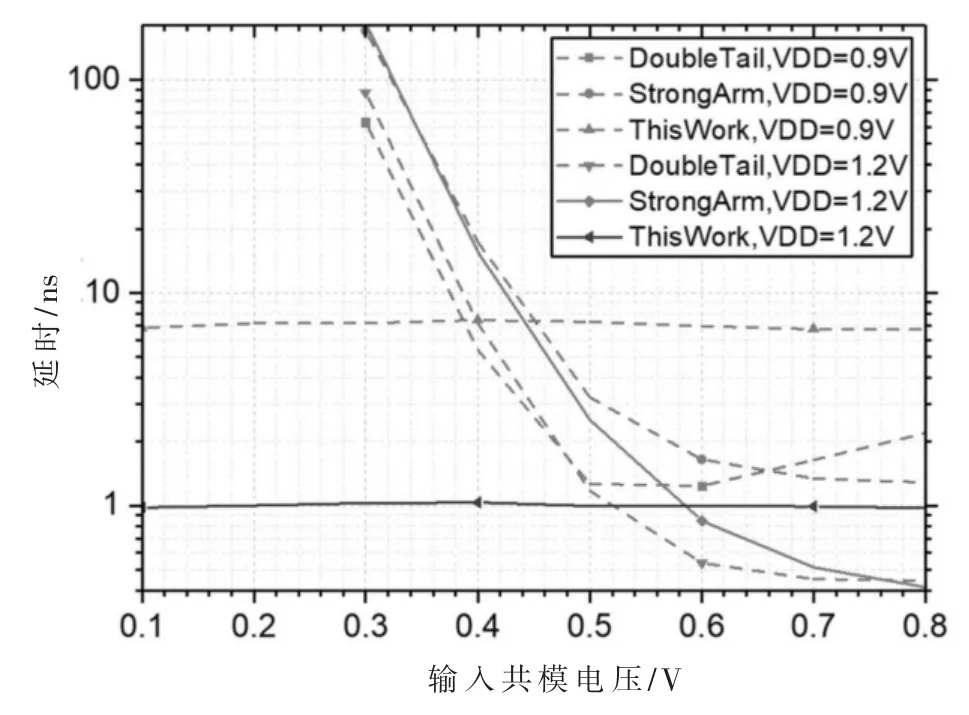

对三个比较器进行延时测试,分别在VDD 为1.2 V、0.9 V,时钟频率为1 MHz 情况下,ΔVin为1 mV,分别验证三种不同比较器在不同输入共模电压下的延时。其中,DoubleTail 与StrongArm 两个比较器在共模输入电压低于0.2 V 情况下不能工作,因此没有数据。仿真结果如图5 所示,双循环比较器具有较好的延时稳定性,例如:在VDD 为0.9 V、输入共模电压为0.3 V 时,本文提出的比较器、DoubleTail 与StrongArm 延时为分7.18 ns、62.94 ns、169.4 ns,在输入共模电压较低时,本文提出的比较器延时性能明显优于其他两种比较器。

图5 三个比较器随输入共模电压的延时变化结果

对三个比较器进行功耗测量,分别在VCM=0.3 V、0.5 V,时钟频率为1 MHz,仿真时间为100 μs,选择其VDD 上的平均电流乘以工作电压,如图6 所示,其功耗基本介于StrongARM 比较器与DoubleTail 比较器之间。

图6 三个比较器随电源电压的功耗变化结果

在VDD=1.2 V,时钟频率为50 MHz,输入电压INP为振幅为20 mV 的三角波(最小值590 mV,最大值610 mV),INN 为600 mV 恒定值。首先截取到OUTP 跳跃到VDD/2的时间点,再选取对应的INP 值减去VDD/2,所得结果为翻转电压,使用蒙特卡洛仿真,仿真测试200 个点,测得其平均值为112.748 u,标准差为2.575 u。结果如图7、图8 所示。

图7 offset 测试

图8 蒙特卡洛仿真结果

在VDD 为0.9 V,VCM 为0.3 V,输入ΔVin为1 mV,时钟频率为1 MHz 时,测试三个比较器延时与功耗,其中DoubleTail 比较器MR1 与MR2 器件会泄漏电流,因此导致功耗骤增,仿真结果如表1 所示。

表1 比较器性能参数仿真结果

3 结论

本文提出了一种适用于超低输入共模电压的CMOS动态电压比较器,通过采用时序开关控制输入输出,增大了输入动态范围;减小堆叠的MOS 管级数,降低了最小电源电压;引入两个正反馈回路,提高了分辨率,从而解决了传统动态比较器无法同时满足低功耗、高分辨率和宽共模输入范围的缺点。基于TSMC 180 nm 工艺进行设计和验证。实验结果表明,提出的比较器具有更大的输入共模范围,并且在速度、功耗和分辨率之间取得了良好的折中,因此适用于物联网的低压低功耗应用场景。