面向SoC 的SRAM 读出电路加固设计

沈 婧,薛海卫,陈玉蓉,张猛华,王 蕾

(中国电子科技集团公司第58 研究所,江苏 无锡 214035)

0 引言

高能带电粒子在器件的灵敏区内产生大量带电粒子的现象,它属于电离效应。当能量足够大的粒子射入集成电路时,由于电离效应(包括次级粒子的),产生数量级多的电离电子-空穴对,引起半导体器件的软件错误,使逻辑器件和存储器产生单粒子翻转,CMOS 器件产生单粒子闭锁,甚至出现单粒子永久损伤的现象,辐射主要包括质子、中子、重离子和α 粒子[1-3]。集成度的提高、特征尺寸的降低、临界电荷和有效LET 阈值下降等会使抗单粒子扰动能力降低。器件的抗单粒子翻转能力明显与电路设计、版图设计、工艺条件等因素有关[4]。

锁存器经常被用于现在的超大规模集成电路中,特别是SoC 和CPU 的流水线结构中[5-6]。数据读出电路的数据锁存也是必不可少的,因此提高锁存器的抗单粒子能力意义重大。本文基于双互锁(DICE)结构[7-8]和Muller_C单元[9-10],对SoC 片上SRAM 的数据读出电路进行了抗辐射加固设计,并先后提出了两种不同结构的读出电路。

1 基于双互锁结构(DICE)读出电路加固设计

在读出电路设计的过程中,需要考虑以下几个问题:

(1)保留数据锁存能力;

(2)尽量提高抗单粒子和抗闩锁能力;

(3)不能影响数据读出的速度;

(4)翻转后恢复时间要尽量短。

本文提出了SoC 片上RAM 的两种读出电路结构,第一种电路结构是基于DICE 单元和Muller_C 延时结构的单模读出通路设计,灵敏放大器的输出通过基于Muller_C单元的延时结构[11]分别为DICE 单元提供两组输入信号,该设计不仅可以保证信号的抗SEU 能力,也能有效地降低单粒子的瞬态扰动,缺点是延时单元会增加数据读出的时间;第二种电路结构是基于DICE 结构的双模读出电路,在DICE 单元的基础上,对灵敏放大器采用双模设计,该设计抗单粒子能力略高于第一种读出电路设计,同时灵敏放大器的输出在作为DICE 单元输入的同时又与最后一级Muller_C 单元直接相连,从而减少了数据读出时间。

1.1 常见读出电路

图1 是常见的数据读出电路,位线的0/1 通过SA 运放之后经过一级Muller_C 单元读出,Muller_C 结构前是一个钟控的锁存器。灵敏放大器使能信号控制灵敏放大器工作,将这一电压差放大为满摆幅的DPU 和DPN 信号,将存储的数据读出。当读出结束后灵敏放大器停止工作,并且将其差分输入端口充电至“1”,这时DPN 为“1”,DPU 为“0”,使数据无法写入锁存器中从而保证读出数据的正确性。灵敏放大器结构如图1 所示。在读出存储节点信号时,SP 为“1”,这时锁存器的反馈链被打断,从而提高了数据读出的速度,当读出结束后,SP 跳变为“0”,从而所存读出的数据。它们在SP 信号的控制下被锁存,并在Q 端输出。

图1 一般读出电路

1.2 基于DICE 结构读出电路设计

1.2.1 单模双互锁结构读出电路

该读出电路结构主要由灵敏放大器、Muller_C 单元和延时电路组成,基于DICE 单元,数据经过灵敏放大器为DICE 输入信号QI1,通过延时结构为DICE 单元提供另一路信号QI2,电路结构图如图2 所示。

图2 基于DICE 结构单模读出电路

该结构中延时电路由多级反相器组成,使得DICE单元的两组输入信号形成一定的延时错位,该延时必须要大于单粒子瞬态扰动的脉宽[12-13]。结合工艺与器件仿真,该部分电路的延时时间在200 ps~300 ps。

加固后读出电路的抗SEU 工作原理为:在读出过程中,如果QI1、QI2 中的一个节点被打翻,这时Q 输出高阻,数据不能写入DICE 锁存单元,当轰击脉冲过去后,QI1、QI2 节点恢复到正确值,这时Q 输出读出的数据,同时数据被保存到DICE 单元中。在读出数据后,节点QI1、QI2 与灵敏放大器的通路断开,这时输出Q 只与DICE 锁存器中存储的数据有关,由DICE 锁存器的抗SEU 特性可知,这时的输出具有抗SEU 的能力。

但该结构有一个缺点,就是QI2 通路的延时1 会增加数据输入到Q 的时间,而对于SoC 芯片来说,该部分的延迟是希望被省下的,为了改进SoC 时序的问题,对SRAM 读出电路部分进行了优化改进,这就形成了第二种双模双互锁结构电路。

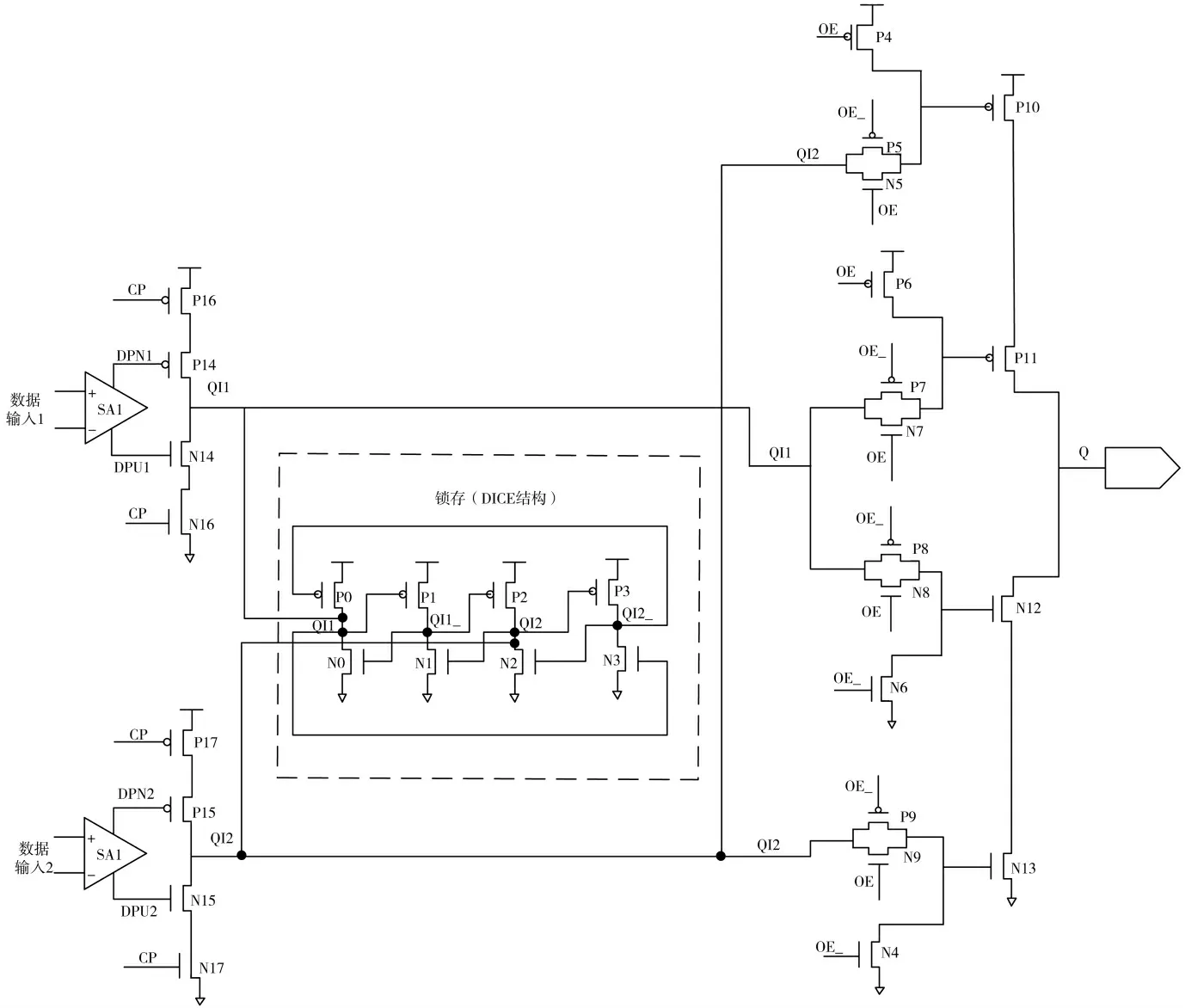

1.2.2 双模双互锁结构读出电路

本结构在单模读出电路基础上做了改进优化,将延时电路产生的QI2 信号用双模灵敏放大器来替代,并将QI1、QI2 直接与后两级读出单元相连,保证DICE 锁存特性的同时进一步缩短数据的读出时间,电路结构如图3所示。

图3 双模双互锁结构读出电路

双模双互锁的结构基础上增加了一个两级OE 控制的读出单元,锁存单元的输出QI1、QI2 经过第一级OE控制的传输门作为第二级读出单元的输入,OE 使能关断的情况下,第一级传输门关闭,锁存单元的数据不会传输到第二级读出单元;第二级读出单元因OE 的关断而被上拉到固定高电平,第二级读出单元也将关断,没有新的数据传输到Q。只有OE 使能,Q 的数据才会更新。

两级带OE 开关的读出结构对数据读出做了更好的隔离,只要OE 使能不打开,端口的数据就不会发生变化,数据的扰动也将会在经过两级OE 开关的读出电路后降低,再加上Muller_C 单元的本身特性,该SRAM 读出电路读出单元有很好的抗单粒子扰动的性能,传输门的延时很小,也不会增加数据读出的时间。

本结构的抗SEU 工作原理与第一种电路结构一样,双模电路结构对数据输入的加固起到了更好的效果,两级的Muller_C 单元起到了更好的抗扰动作用。而数据读书时间方面,通过仿真实验对比,双模双互锁结构的读出电路数据读出时间比第一种结构缩短了约350 ps。

1.3 读出时间Ta 对比

基于sign off 工艺角和电压,采用SPICE 仿真工具,分别对两种结构的SRAM 进行了详尽的仿真验证,4 kB容量的SRAM 读出时间对比如表1 所示。

表1 两种SRAM 结构读出时间对比(ns)

由表1 的仿真数据可以得出,在相同容量的条件下,采用双模双互锁读出结构的SRAM 读出时间缩短10%左右。

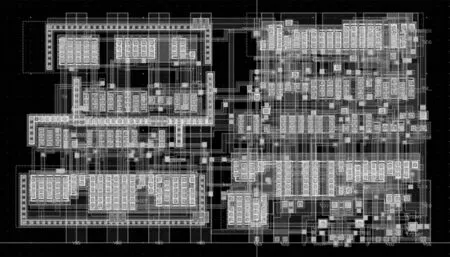

2 版图设计

为了防止数据输入通路的两个节点同时翻转,在版图设计过程中充分考虑两组信号输入通路之间的间距。

图4 为单模双互锁结构的SRAM 读出电路,敏感节点设计为间距5.4 μm;图5 为双模双互锁结构的SRAM读出电路,敏感节点设计为间距4 μm。

图4 单模输入双互锁读出电路版图

图5 双模输入双互锁读出电路版图

3 单粒子翻转实验数据对比

本设计的两种不同结构的SRAM 分别应用于同一款SoC 芯片的两个版本,片内SRAM 容量为32 kB,流片工艺为0.18 μm CMOS 工艺,单粒子仿真采用结合TCAD及SPICE 软件相结合的方法[14-15]。

单粒子翻转试验采用中国原子能科学研究院的HI-13重离子加速器,分别在F、CL、Ti、Ge 和I 五种离子下对电路进行了辐射实验,两种结构的实验测得结果如表2所示。

表2 SoC 片内SRAM 5 种离子辐射实验结果对比

在F 离子和CL 离子下,片内SRAM 均未发生单粒子翻转现象,在Ti 离子、Ge 离子、I 离子下片内SRAM均发生了不同位数的翻转,实验结果表明在受到较高能量辐射时,芯片的单粒子翻转效应更容易产生。

通过SEU 数目和单粒子翻转截面的数据对比,相同试验条件下双模DICE 结构的SRAM 的单粒子翻转数略少于单模DICE 结构的SRAM,计算得出的单粒子翻转截面结果数量级一致,实验结果表明两种结构的SRAM具有相当的抗单粒子翻转能力。

4 结论

本文提出的两种基于DICE 结构和Muller_C 单元的读出电路结构均能有效地提高SoC 片内SRAM 的抗单粒子能力和抗扰动能力。采用两种结构SRAM 的SoC 电路于0.18 μm CMOS 工艺线流片验证。双模DICE 读出结构的SRAM 电路读出时间比单模DICE 读出结构的SRAM 电路读出时间缩短10%,在实际设计SoC 片上RAM时,可综合考虑面积、速度、抗SEU 能力来选择读出电路的设计结构。