高k 介质对屏蔽栅沟槽型MOSFET 电场调制的研究

麻泽众,冯全源,赵宏美

(西南交通大学 微电子研究所,四川 成都 611756)

在中低压功率器件领域,沟槽型MOSFET 因具有通态电阻低、开关速度快等优点,得到了普遍应用[1-2]。在传统沟槽型MOSFET 的基础上,Baliga[3]最早提出了一种基于电荷耦合效应的沟槽型MOSFET(Charge Coupling MOSFET,CC -MOSFET)。由 于CC-MOSFET沟槽内部存在一个与源极相连的多晶硅,也可以称为屏蔽栅沟槽型MOSFET[4](Shielded Gate Trench MOSFET,简称SGT 结构)。源极多晶硅能够通过产生横向电场改善漂移区的纵向电场,提高了器件的击穿电压,另外还可以将部分栅漏电容转化为栅源电容[5]。由于SGT 结构漂移区的纵向电场呈悬链式分布,可以进一步优化漂移区中间区域的电场。为此有相关研究提出多层漂移区结构[6],利用不同的外延层掺杂浓度,在掺杂浓度的交界面引入新的电场峰值,使漂移区电场更加均衡;多阶梯侧氧结构[7]利用不同厚度的氧化层在漂移区内引入新的电场峰值,进而优化电场分布;漂移区内加入P 柱[8]可以通过引入负电荷来增强漂移区横向电场,改善了漂移区的纵向电场,但是形成P 柱需要额外的掩模。

为了优化漂移区的电场分布,本文把高k介质应用于传统SGT 结构的沟槽侧壁绝缘层中,并将提出的新结构称为高k屏蔽栅沟槽型MOSFET (高kSGT 结构)。另外,通过Sentaurus TCAD 软件对传统SGT 结构和高kSGT 结构的性能进行了仿真对比。

1 器件结构和原理

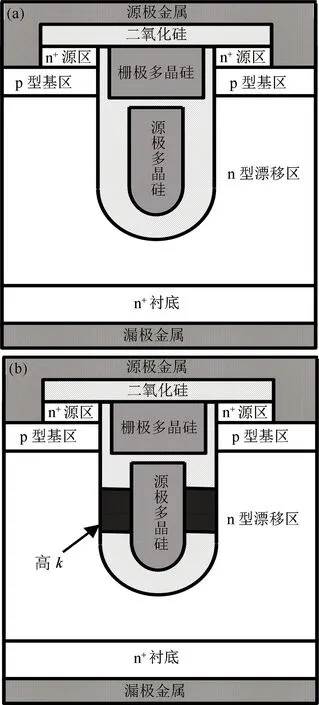

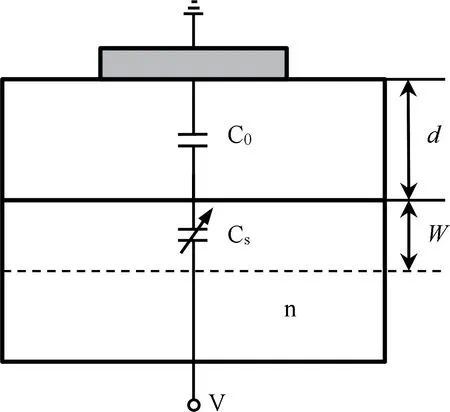

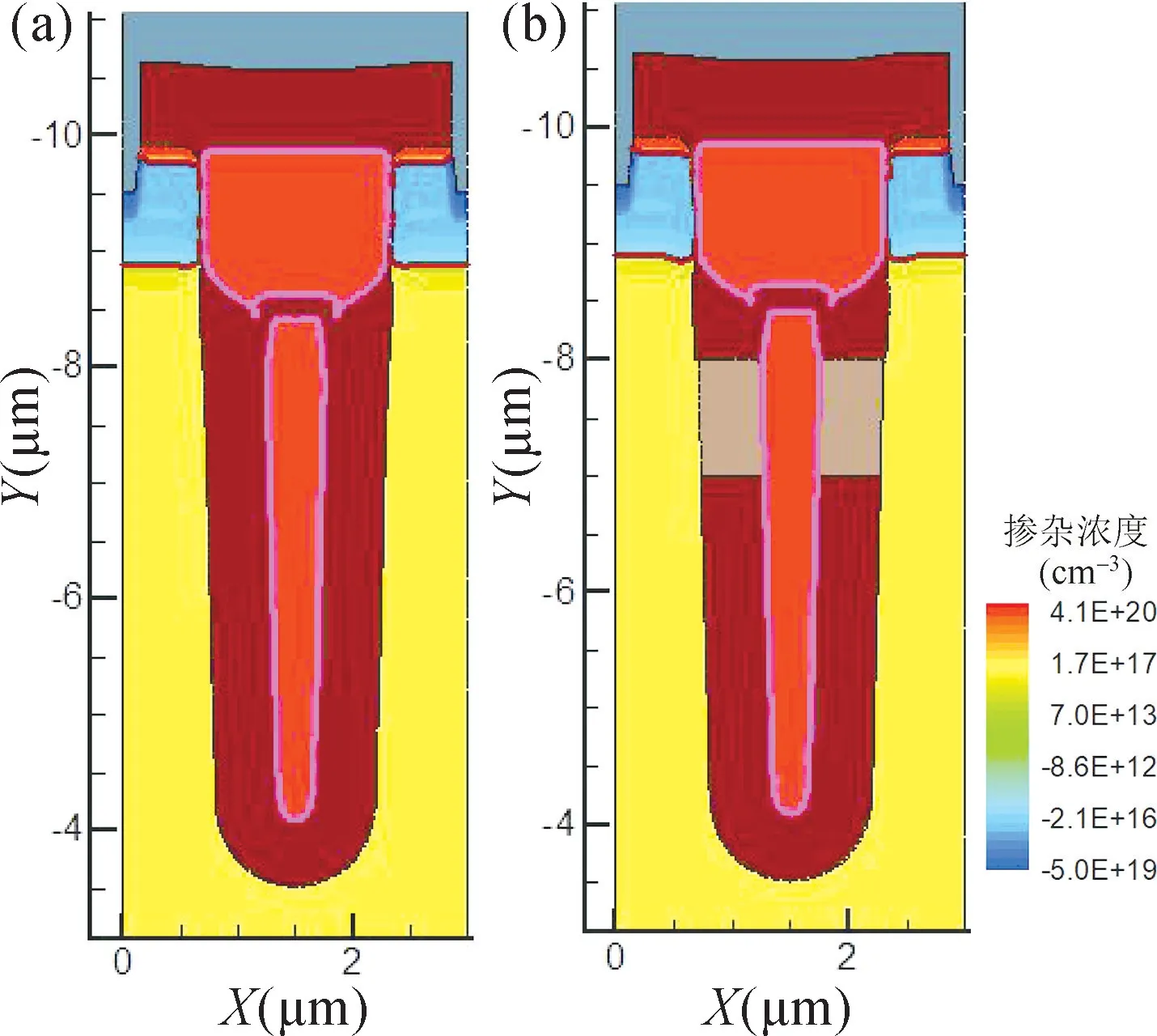

传统SGT 结构的截面示意图如图1(a)所示,该结构包括n+衬底、n 型外延层、U 型沟槽、沟槽顶部的栅极多晶硅、沟槽底部的源极多晶硅、p 型基区、n+源区、源极金属和漏极金属。传统SGT 结构在导通状态下,电子从n+源区分别流过p 型基区的导电沟道、n 型漂移区和衬底,形成漏极到源极的通态电流。当栅压小于器件的阈值电压时,器件处于截止状态,p 型基区和n 型漂移区组成的PN 结通过纵向延伸耗尽层来承受较大的反向漏源电压[9]。图1(b)是本文提出的高kSGT 结构示意图,与传统SGT 结构不同的是,将沟槽侧壁的二氧化硅部分替换成拥有更高介电常数的绝缘介质,同时保留沟槽顶部和底部的二氧化硅。

图1 传统SGT 结构和高k SGT 结构的截面示意图Fig.1 Cross section of traditional SGT structure and high k SGT structure

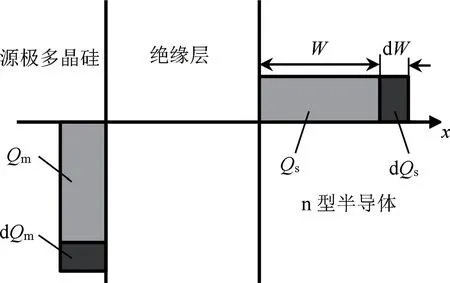

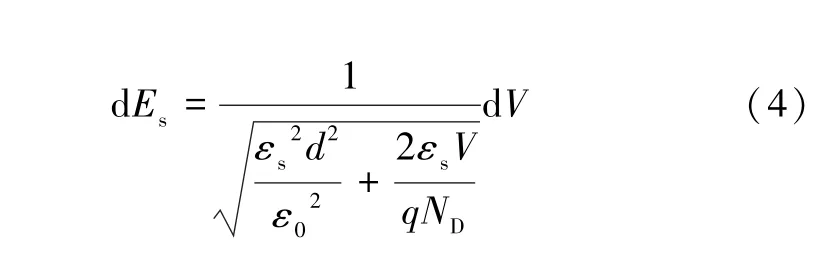

源极多晶硅与n 型漂移区隔着较厚的绝缘层,构成一个MIS(Metal-Insulator-Semiconductor)结构。高k介质的作用可以通过MIS 结构来分析,当源极多晶硅施加负偏压V时,n 型漂移区会进入耗尽状态,此时由于耗尽层中存在带有正电荷的施主离子,将会在源极多晶硅表面也感应出等量的负电荷,如图2 所示。MIS 结构的电容定义为:

图2 多子耗尽时随外加电压变化的微分电荷分布Fig.2 Differential charge distribution with applied voltage for majority carrier depletion

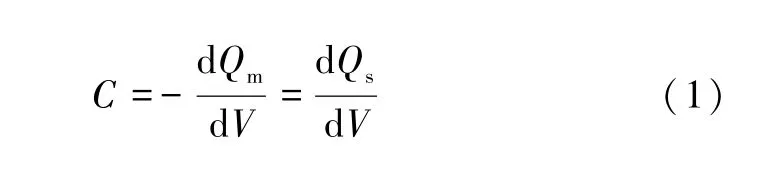

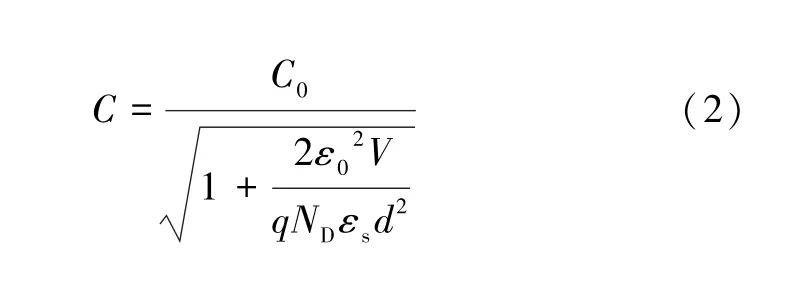

式中:Qm为源极多晶硅中单位面积的负电荷;Qs为耗尽层单位面积的正电荷。MIS 结构电容由绝缘层电容C0和耗尽层电容Cs串联组成,其等效电路如图3 所示。当半导体表面耗尽时,MIS 结构电容为[10]:

图3 MIS 结构的等效电路Fig.3 Equivalent circuit of MIS structure

式中:C0=ε0/d,为单位面积的绝缘层电容;ε0为绝缘层介电常数;d为绝缘层厚度;εs为硅的介电常数;ND为施主杂质浓度。根据高斯定理,表面的电荷面密度与电场强度有以下关系[11]:

式中:Es为耗尽层表面的电场强度。将式(2)和式(3)代入式(1)中,可得:

从式(4)可以看出,当外加偏压V一定时,耗尽层的表面电场会随着绝缘层介电常数增大而增大。当器件承受漏源电压时,沟槽两侧的漂移区会处于完全耗尽的状态,存在大量的正电荷施主离子。在传统SGT 结构中,漂移区耗尽层中的施主离子一部分终止于p 型基区耗尽层中带负电荷的受主离子,另一部分施主离子终止于源极多晶硅的感应负电荷。而在高kSGT 结构中,由于高k介质的存在,使更多施主离子终止于源极多晶硅的负电荷,而终止于p 型基区的施主离子数量将会减少。因为电场强度代表了电力线的密集程度,最终降低了PN 结处的电场强度,提高了漂移区中间区域的电场强度。

2 仿真结果与讨论

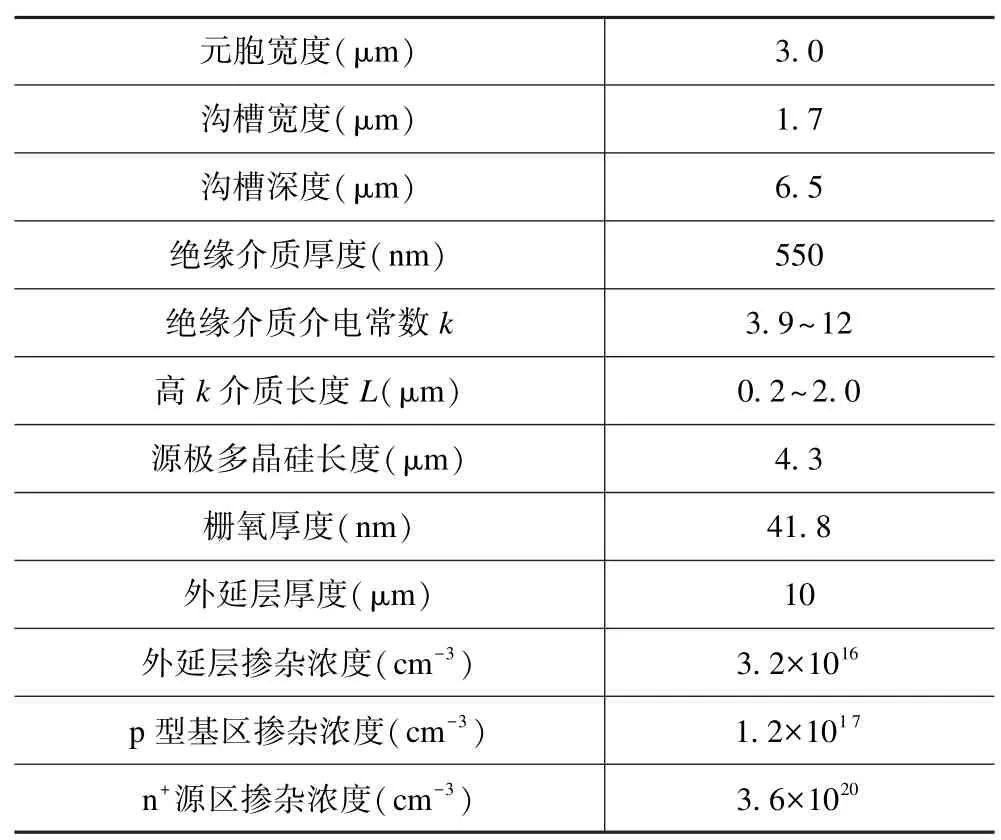

传统SGT 结构和高kSGT 结构均使用Sentaurus TCAD 软件进行仿真,为了比较高k介质对电场的影响,本文在击穿电压为103.4 V 的传统SGT 结构基础上设计高kSGT 结构,除了沟槽侧壁绝缘介质不同之外,其他参数保持不变,具体的结构参数如表1 所示。与传统SGT 结构相比,高kSGT 的工艺流程增加了高k介质的淀积和回刻,但此步骤不需要增加额外的掩模版,其他的工艺流程[12]均与传统SGT 结构相同。

表1 器件的仿真参数Tab.1 Simulation parameters of the devices

根据上述参数得到传统SGT 结构和高kSGT 结构最终的仿真模型,如图4 所示。其中,高k介质位于Y=-8~-7 μm 的位置。

图4 传统SGT 结构和高k SGT 结构的仿真模型图Fig.4 Simulation model diagram of traditional SGT structure and high k SGT structure

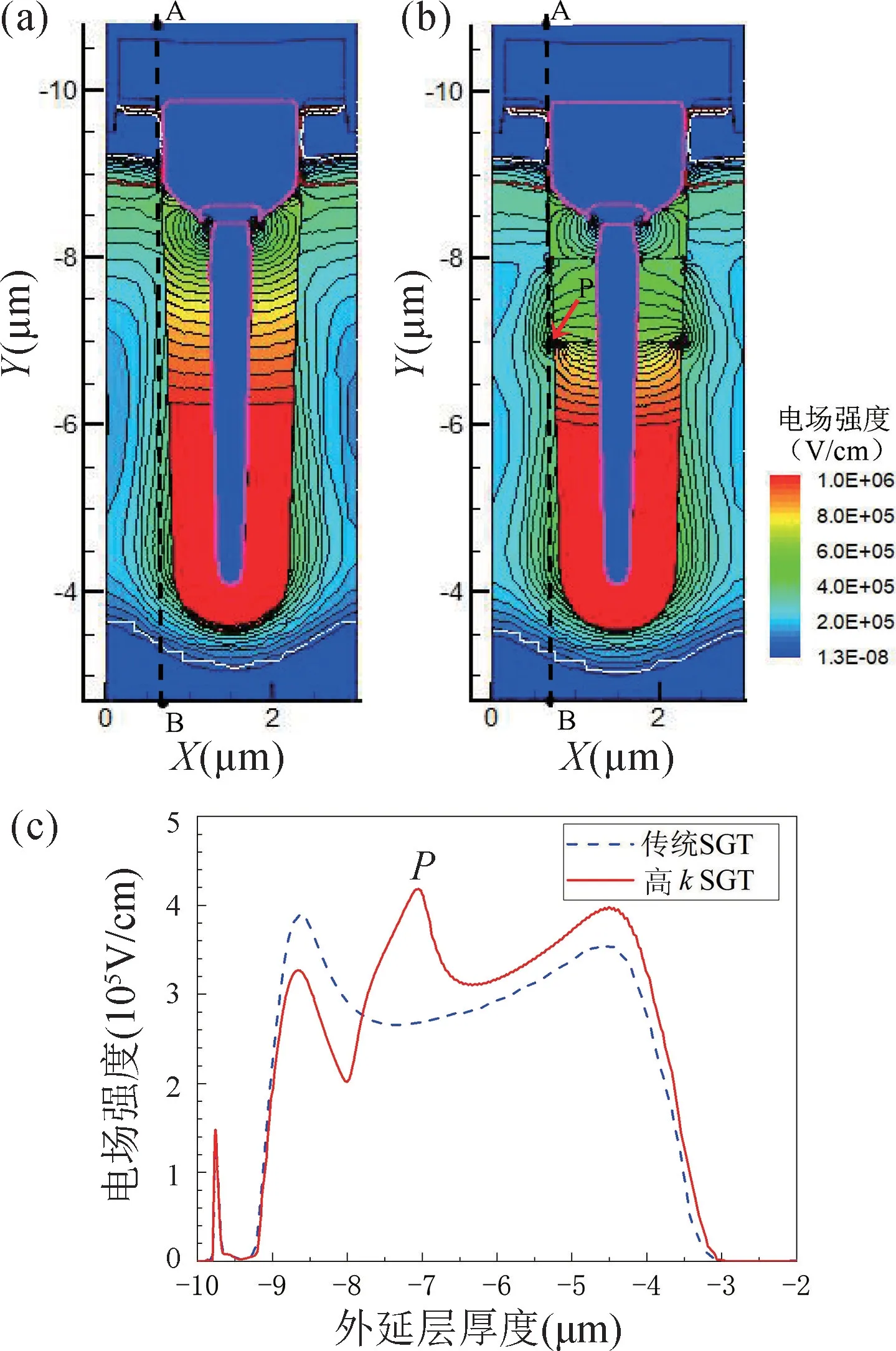

当器件的栅极和源极接地,漏极加正电压时,传统SGT 结构的电场分布如图5(a)所示,图5(b)为高kSGT 结构的电场分布。从图5 中可以看出传统SGT结构的漂移区电场峰值分别位于p 型基区与外延层交叠的PN 结和沟槽底部,而高kSGT 结构在漂移区中间区域引入一个新的电场峰值P。取两种结构切线AB处的电场进行对比,如图5(c)所示,可以看出高k介质将电场峰值中间较低的电场进行拉高,同时PN 结处的电场峰值略有降低,仿真结果符合前文的理论分析。高kSGT 结构的击穿电压仿真结果为112.8 V,结果表明可以通过高k介质优化电场分布来提高击穿电压。

图5 传统SGT 结构和高k SGT 结构的电场分布对比Fig.5 Comparison of electric field distribution between traditional SGT structure and high k SGT structure

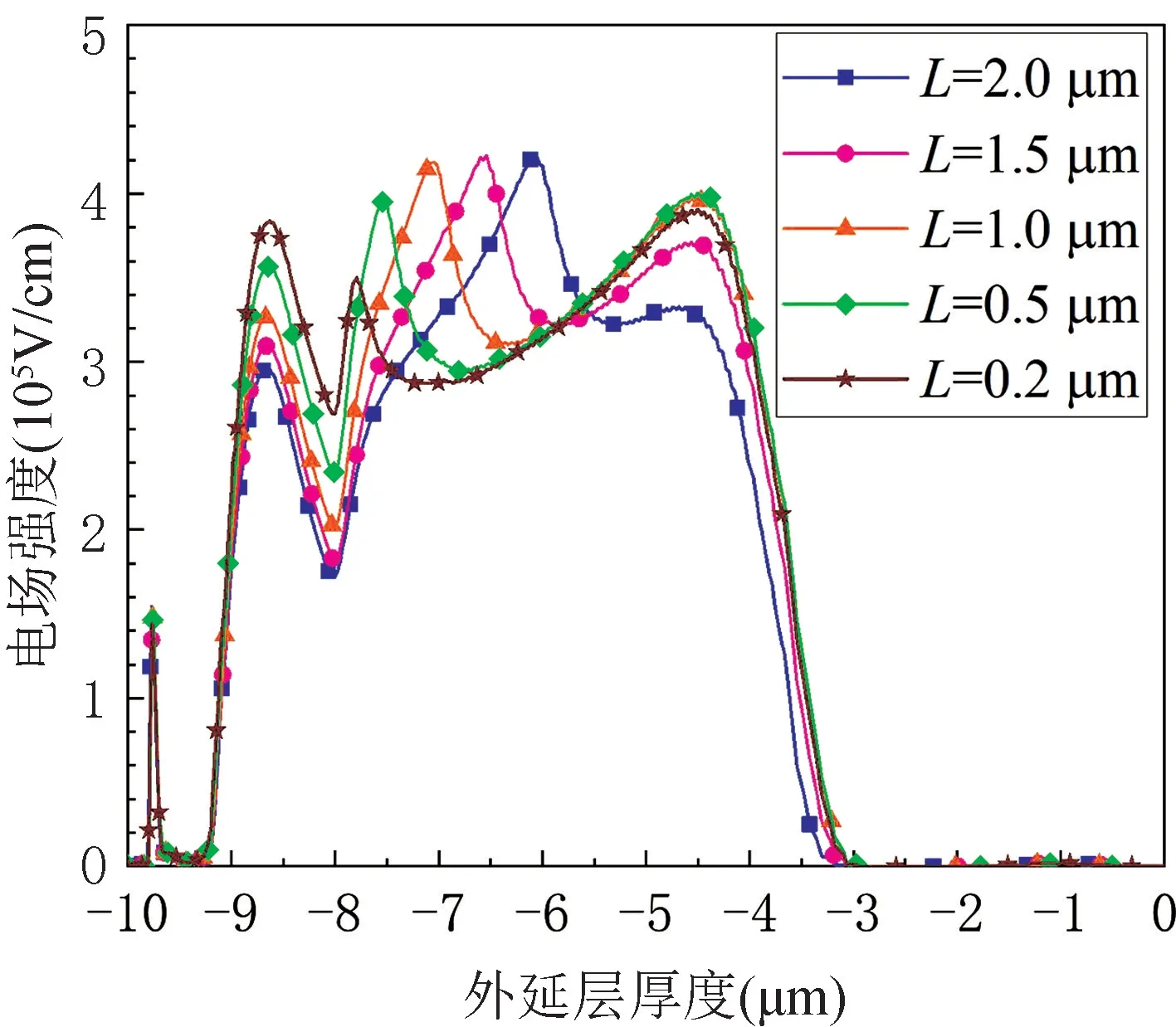

高k介质在沟槽中的位置会对电场分布产生较大的影响,从图5(a)可知,传统SGT 的漂移区电场较低的区域位于Y=-8~-6 μm 处,为了提高该处的电场,将高k介质的起点固定在Y=-8 μm 的位置,沿y轴向下将长度L分别设置为0.2,0.5,1.0,1.5 和2 μm,其电场分布如图6 所示。新的电场峰值P会随着长度增加而逐渐向沟槽底部方向移动,另外电场峰值也会随着长度增加而增大。当L大于0.5 μm 时,新的电场峰值就会超过沟槽底部的电场峰值,导致击穿位置发生在高k介质底部,所以需要通过调整高k介质的位置来使电场分布相对均衡。

图6 k=10 时不同高k 介质长度下的电场强度Fig.6 Electric field distribution of different high k dielectric lengths at k=10

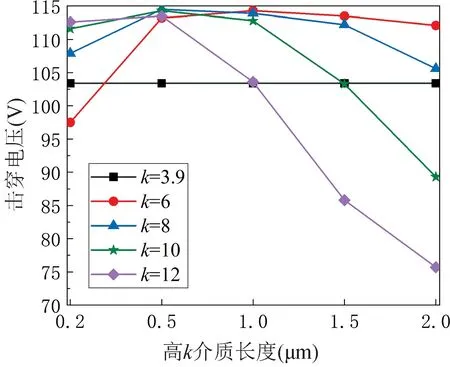

高k介质的介电常数也是影响电场分布的一个重要因素。取介电常数k=6,8,10,12,分析在不同长度下的击穿电压,仿真结果如图7 所示。其中k=3.9是二氧化硅的介电常数,表示传统SGT 结构的击穿电压。从图7 可知,介电常数保持不变时,击穿电压随着高k介质长度的增加呈现出先增加后减小的趋势。当新的电场峰值与沟槽底部的电场峰值相等时,高kSGT 结构达到最大的击穿电压。在相同高k介质长度条件下,当介质长度较小时,击穿电压随着介电常数增大而增大,但当介质长度较大时,低介电常数有更大的击穿电压,因为电场强度与介电常数有正相关关系[13]。当高k介质长度L=0.5 μm、介电常数k=8时,击穿电压达到最大值114.5 V。与传统SGT 结构相比,高kSGT 结构的击穿电压提升了10.7%。

图7 不同高k 介质条件下的击穿电压Fig.7 Breakdown voltage under different high k dielectric conditions

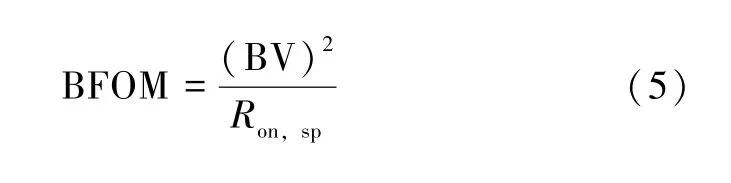

当器件正向导通时,沟槽侧壁的漂移区会形成一层较薄的耗尽层,由于高k介质会产生更多的电荷使耗尽层进一步地横向扩展,相应的电流导通路径将会变窄,使漂移区导通电阻略微增大。为了对击穿电压和特征导通电阻进行折中考虑,引入Baliga 优值(BFOM)[14],计算公式如下:

由于特征导通电阻在不同高k介质条件下变化很小,BFOM 整体的变化趋势与击穿电压相似。与传统SGT 结构相比,高kSGT 结构的BFOM 最大提升了15.2%,降低了器件的导通损耗。

高kSGT 结构与文献[6]提出的多阶梯侧氧分离栅沟槽MOSFET(简称MSO 结构)均通过改变绝缘介质层,在漂移区内引入新的电场峰值,从而提高器件的击穿电压。但是MSO 结构需要多次的氧化层和多晶硅刻蚀步骤,而高kSGT 结构只增加了高k介质的淀积和回刻,相对来说需要的工艺步骤较少,但是需要注意高k介质与硅的界面热稳定性问题[15]。

3 结论

本文分析了高kSGT 的器件原理及高k介质的作用机理,并利用TCAD 仿真软件对高k介质长度和介电常数进行了优化分析。结果表明,1 μm 以内的高k介质长度可以有效提高中低压SGT 结构的击穿电压,超过1 μm 时则适用于深沟槽的高压SGT 结构。另外高k介质的介电常数在6~10 范围内可以提高器件的击穿电压,但过高的介电常数会导致击穿电压下降。