流水灯实验设计与仿真

◇宝鸡文理学院电子电气工程学院 韩芝侠 王晓利 张文娟

为帮助学生理解掌握中规模数字集成器件的应用,本文在Multisim环境下完成了8路流水灯实验设计与仿真,并拓展到如何设计10路或16路流水灯,以此训练电类工科学生电路分析和设计能力,提高学习兴趣,培养创新思维能力和实践动手能力。

计数器、译码器是数字电路中使用最多的中规模集成器件,本文以此为核心设计了流水灯控制电路,并在Multisim环境下进行了虚拟仿真,结果直观清晰,电路调试方便[1]。此实验设计方案只是一个用于学习和实践的简化案例,旨在让学生感受学以致用的价值,提高学习兴趣及电路分析和设计能力。随着后续课程的学习,将会有其他更好更简洁的技术方案[2]。

1 任务要求及设计方案

任务要求:8路彩灯能够自动循环点亮,产生一种流动变化的效果,俗称流水灯控制。

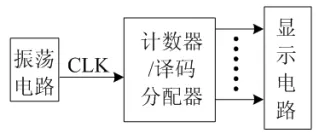

设计方案:先设计8进制计数器,以控制8路信号;计数器的输出接3-8译码器的输入,以产生8个输出信号中唯一有效的输出脉冲,后级再接入发光二极管以显示流水灯效果。设计框图如图1所示。

图1 设计框图

器件介绍如下所示。

74160是异步清零、同步预置数的集成十进制计数器[3],CLK时钟输入端,上升沿有效;~CLR 异步清零端,低电平有效;~LOAD同步预置数控制端,低电平有效;ENP/ENT工作状态控制端,高电平有效;DCBA数据输入端,用于预置计数器初始状态;QDQCQBQA计数器输出端。

74LS138是集成3-8译码器[3],CBA是地址输入端,Y0-Y7是八个输出译码线,低电平有效;还有三个使能端,只有G1=1,G2A+G2B=0时,译码器才处于工作状态,例如CBA=001,Y1号输出线上有信号,为低电平0,其余输出线都为高电平1;当使能端不满足上述状态时,译码器禁止工作,输出全部为1。

2 流水灯实验设计与仿真

在Multisim环境下给出如图2所示的实验设计电路。其中:

时钟信号:CLK来自于信号源提供的方波信号,频率1 Hz,幅值5 V。

计数器:利用一片74160,采用同步预置数法设计八进制计数器。若DCBA预置0000,则置数控制端~LOAD=0的信号就从QDQCQBQA= 0111的状态译出,即将QCQBQA通过与非门送到~LOAD端(因为它是同步预置数,低电平有效),同时将~CLR端、ENP/ENT接高电平。工作时每来一个CLK上升沿,计数器累计加1,当计到0111时,尽管~LOAD=0,但必须等到下一个CLK上升沿到来,才会将0000置入计数器,所以稳定的计数状态中包含0111,从而实现0到7共8个计数状态的循环。

译码器:因为要依次控制8个灯中的其中1个点亮,所以采用一片74LS138即可,按功能表要求将三个使能端G1G2AG2B如 图2依次接高、低电平,三个地址端CBA接计数器的低三位输出端QCQBQA。

显示电路:因为译码器正常译码时,只有1个输出译码线为低电平,其余7个都是高电平,所以将译码器的输出接到发光二极管的阴极,阳极则通过限流电阻接到高电平上。

仿真分析:在Multisim下启动仿真运行按钮,则八个发光二极管从上到下轮流被点亮,一次只亮一个,产生一种流水灯效果。

3 拓展知识

归纳总结该电路工作过程,思考以下问题:

(1)如果将图2中所有发光二极管的位置反向,则实现的就是八个发光二极管从上到下轮流被熄灭,一次只灭一个,产生一种流水灯效果。

图2 8路流水灯控制电路

(2)如何实现10路流水灯控制?可直接用一片74160实现十进制计数器设计,不需要门电路;再用2片3-8译码器扩展成为4-16译码器。重难点是计数器的输出与译码器地址端、使能端的连接。即两片译码器的CBA分别相连后对应接到计数器的QCQBQA上,第一片的使能端G1接 高电平,G2AG2B与第二片的G1相接作为变量D对应接到计数器的QD上,第二片的G2AG2B接 低电平。10个发光二极管分别接到第一片的八个输出译码线上及第二片的低两位输出译码线上。当D=0时,第一片译码器工作,第二片禁止,输出由第一片决定;当D=1时,第一片禁止,第二片工作,输出由第二片决定。

(3)如何实现16路流水灯控制?只需将步骤2中的十进制计数器换成十六进制计数器,如74161,这样就可以设计10以上16以内的任意进制计数器,16个灯来自于2片译码器的所有输出即可。

(4)如果要求流水灯变化时频率快慢可调,则利用555定时器设计一个多谐振荡器,自动产生时钟脉冲信号,其中一个固定电阻串接电位器,方便调节频率。

4 结语

基于Multisim的电路设计和仿真,方便学生及时消化理解课堂知识,验证设计思路,激发学习兴趣[4]。本文通过数字电路中一个具体实例的设计、仿真及分析,进而引申到设计任务要求不同时如何进行变通,引发学生积极思考并拓展训练所学知识,使学生熟悉并掌握《数字电子技术》课程中典型电路的分析、设计、仿真等完整步骤和方法,以培养工科学生分析问题、解决问题、实践动手及创新思维能力。