基于FPGA的多通道多电平高压信号发生器

周家辉,刘一清

(华东师范大学通信与电子工程学院,上海 200241)

随着电子信息产业的不断发展,各领域对于实验仪器也产生了新的需求。机器人灵活协调的动作需要多路二电平PWM 波形来驱动电机协同运作[1-3];新能源发电系统需要产生多电平波形实现逆变电源[4-6];DLP 投影仪中使用的数字微镜器件也需要复杂的多电平高压波形来进行驱动[7]。在各个新兴领域中,多通道、高电压、多电平信号驱动的需求日益增加,但是目前市面上缺少相关仪器,迫切需要科研人员进一步开展研究。文中针对MEMS 数字微镜的驱动,设计了一款多通道多电平高压信号发生器,具有使用便捷、灵活性强、可靠性高等特点,同时也可应用于电机驱动、电源驱动和新型器件驱动等多种领域。

1 系统设计

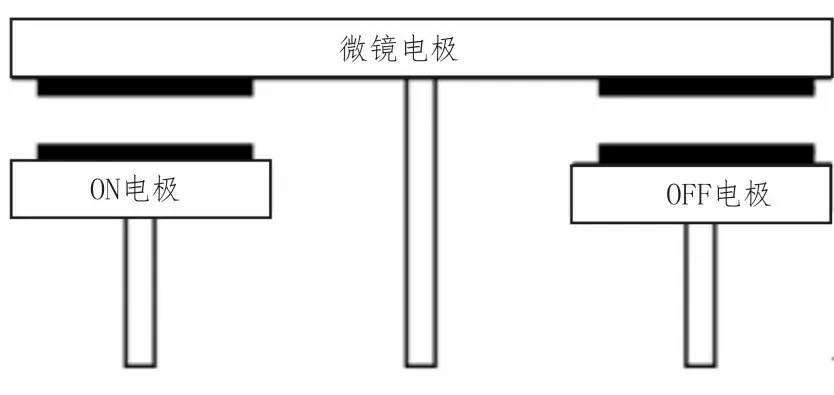

数字微镜器件是一种反射式光开关[8],是DLP 投影技术的核心器件,可以分为MEMS 数字微镜和CMOS 驱动电路两个部分,文中设计的多通道多电平高压信号发生器用于直接驱动MEMS 数字微镜,方便MEMS 数字微镜开发人员测试其微镜的质量。MEMS 数字微镜结构如图1 所示,分为微镜电极、ON电极和OFF 电极3 个电极,微镜电极是公共电极,它与ON 电极、OFF 电极之间可分别等效为两个电容,所以驱动一个MEMS 数字微镜可以等效为驱动两个容性负载。

图1 MEMS数字微镜结构示意图

MEMS 数字微镜大多采用静电驱动,工作时有两种状态,ON 状态和OFF 状态[9-10]。当ON 电极与微镜电极之间的压差大于OFF 电极与微镜电极之间的压差时,MEMS 数字微镜将处于ON 状态,MEMS 微镜将入射光反射到投影窗口区域中,呈现全“亮”的投影效果;反之,当OFF 电极与微镜电极之间的压差大于ON 电极与微镜电极之间的压差时,MEMS 数字微镜将处于OFF 状态,MEMS 微镜将入射光反射到投影窗口区域外,呈现全“暗”的投影效果[11-13]。

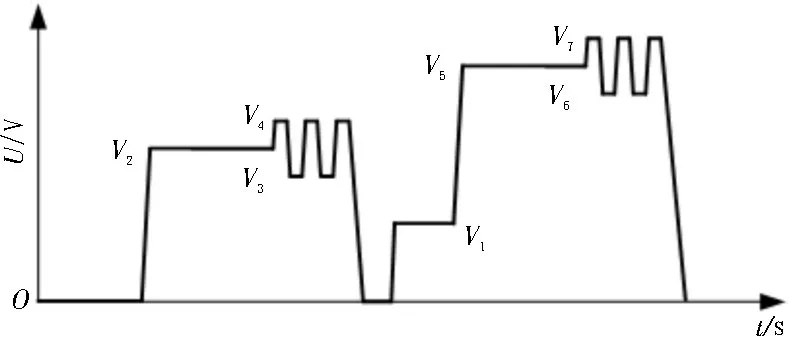

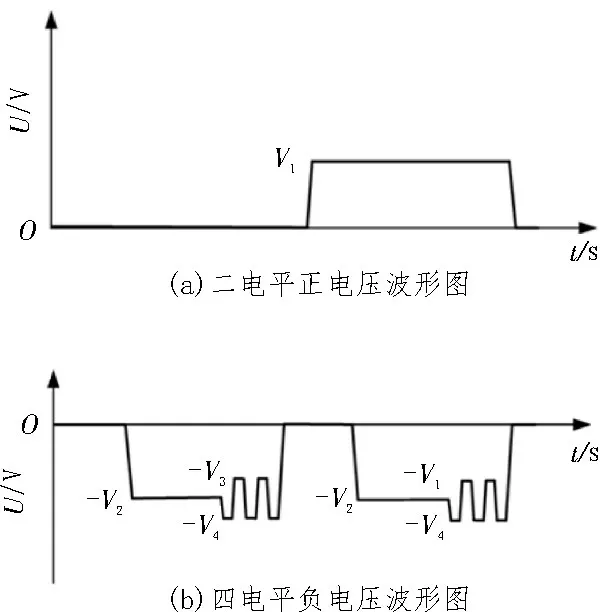

对于MEMS 数字微镜而言,如果将公共的微镜电极接地,那么ON 电极(或OFF 电极)的驱动波形如图2 所示。如果驱动电路直接产生这一波形,那么驱动电路的设计难度较大,一方面该波形电平数达到8 个(包括地电平在内),驱动电路较复杂,另一方面该波形对驱动电路器件的耐压值要求也较高,最高电压达到60 V。

图2 MEMS数字微镜驱动波形图

由于8 个电平存在如下数值关系:

所以文中采用了“悬浮式”电路结构对八电平驱动波形进行分解,以简化电路结构。如图3 所示,ON 电极与OFF 电极采用二电平正压波形驱动,公共的微镜电极采用四电平负压波形驱动,这样不仅降低了电路结构的复杂度,也降低了对器件耐压值的要求。

图3 MEMS数字微镜驱动分解波形图

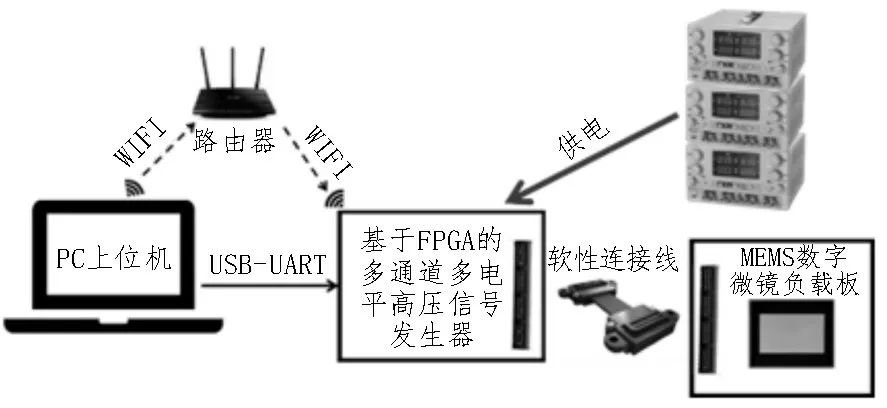

文中所设计的多通道高压多电平信号发生器的系统框图如图4 所示,信号发生器64 通道输出信号的时序参数由PC 上位机程序通过有线USB 或无线WIFI 两种方式进行配置,信号发生器输出信号的电压参数由外部稳压电源进行设置,信号发生器输出信号通过软性连接线连接到定制的MEMS 数字微镜负载板,以驱动MEMS 数字微镜。

图4 系统框图

2 硬件设计

2.1 核心控制电路

文中所设计的多通道多电平高压信号发生器硬件上分为核心控制电路和功率驱动电路两部分。核心控制电路以Xilinx 公司Artix-7 系列FPGA(XC7A35T-1FGG484C) 和ST 公 司ARM Cortex-M7微处理器(STM32F767BIT6)为核心器件,外设包括时钟电路、复位按键、WIFI 模 块、MicroUSB 接 口、FLASH 存储器等,此外,核心控制电路留有板对板连接器,用于连接功率驱动电路。

2.2 功率驱动电路

2.2.1 二电平正电压驱动电路

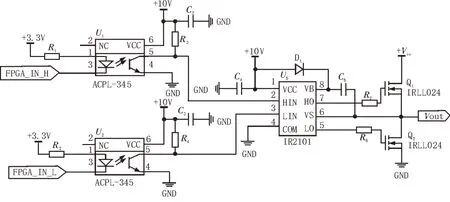

二电平正电压驱动电路采用NMOS 半桥驱动拓扑,电路原理图如图5 所示。NMOS 管采用IRLL024N,源漏电压VDS最大为55 V,漏极电流ID最大为3.1 A,导通电阻为65 mΩ;半桥驱动器采用IR2101,死区时间的控制通过FPGA 实现,FPGA的控制信号通过光电耦合器连接到半桥驱动器的输入。

图5 正电压NMOS半桥驱动电路原理图

FPGA 产生NMOS 半桥电路的控制时序时,需要注意NMOS 半桥死区时间必须折中选择,既不能太大,也不能太小。死区时间太小会导致NMOS 半桥两个NMOS管同时处于饱和区的时间过长,从而造成NMOS 半桥的交叉损耗变大,甚至导致器件损坏[14];死区时间太大又会导致输出信号波形出现过长的异常电平[15]。折中选取后,将NMOS 半桥的死区时间设置为50 ns。

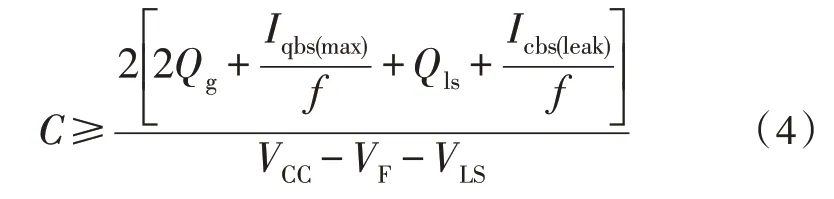

对于图5的NMOS 半桥驱动拓扑,自举电容C5在下管Q2导通时通过二极管D1充电,在上管Q1导通时给上管栅极驱动器供电,所以自举电容C5的取值与输出频率相关,输出频率越低、输出连续的高电平时间越长,自举电容需要的容值越大[16],自举电容取值为:

其中,Qg是NMOS 管的栅极电荷,Iqbs(max)是上管驱动电路的最大静态电流,Qls是驱动器内电平转换器需要的电荷,Icbs(leak)是自举电容的漏电流,VCC是自举电容通过二极管充电的供电电压,VF是二极管的正向导通压降,VLS是下管的压降,f是输出信号频率。

2.2.2 四电平负电压驱动电路

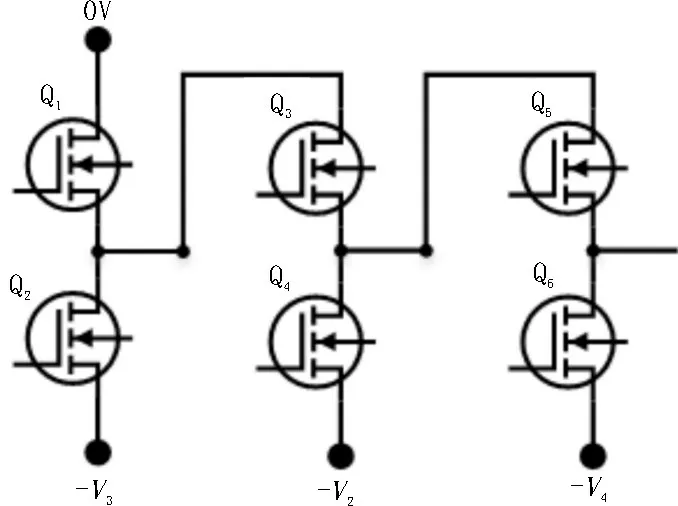

四电平负电压驱动电路采用NMOS 半桥级联型拓扑结构,如图6 所示,设计了三级级联半桥拓扑结构,通过控制6 个NMOS 管的开关产生四电平驱动波形。

图6 三级级联NMOS半桥拓扑结构示意图

NMOS 半桥拓扑需要满足上管电压大于下管电压,所以对于图6 所示的三级级联NMOS 半桥拓扑,4 个电平必须满足如下条件:

该条件与图3(b)中各电平之间的关系一致。

级联NMOS 半桥驱动拓扑工作时,每个半桥最多只有一个NMOS 管导通。当输出0 V 时,NMOS 管Q1、Q3和Q5导通,其余截止;当输出-V3时,NMOS 管Q2、Q3和Q5导通,其余截止;当输出-V2时,NMOS 管Q4和Q5导通,其余截止;当输出-V4时,NMOS 管Q6导通,其余截止。

以第一级NMOS 半桥为例,由于第一级NMOS半桥下管电压是负电平-V3,所以相比于图5 正电压NMOS 半桥驱动电路,负电压NMOS 半桥驱动电路的电压参考点从0 V(GND)变为输出的负电平-V3,此外电路的辅助供电电平也从+10 V 变为-V3+10 V。

3 软件设计

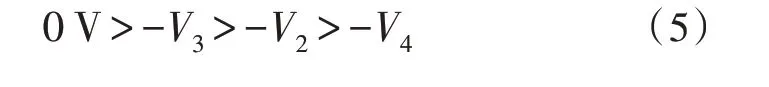

系统软件框图如图7 所示,输出波形的参数通过PC 上位机设置,上位机的控制命令根据自定协议打包后通过有线USB 或者无线WIFI 发送到ARM 微处理器。ARM 微处理器将PC 上位机的打包数据进行接口协议转换,并通过SPI 接口将控制命令发送给FPGA,FPGA 根据控制命令输出控制时序到功率驱动电路,从而产生二电平正电压和四电平负电压驱动波形,产生高压多电平信号。

图7 软件系统框图

完成硬件连接与供电后,需要在PC 上位机控制界面按如下步骤进行操作:

1)选择连接方式,USB 有线或WIFI 无线;

2)选择配置方法,不仅可以通过界面中的配置表进行配置,还可以通过载入规定格式的excel 表进行配置;

3)填写配置信息,如果选择界面中的配置表,在表中选择配置通道,填写对应的时序参数,如频率、相位、占空比等;

4)点击确认配置按钮,完成配置。

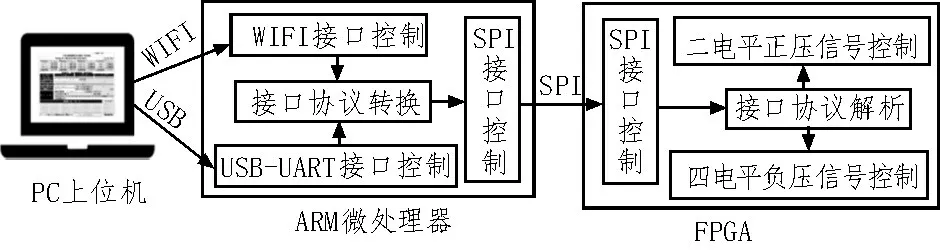

4 测试与验证

多电平高压信号发生器硬件实物图如图8 所示,包括核心控制电路板、功率驱动电路板和负载测试板,核心控制电路板通过板对板连接器连接到功率驱动电路板,负载测试板用于模拟MEMS 数字微镜子板,MEMS 数字微镜可等效为容性负载。

图8 多电平高压信号发生器硬件实物图

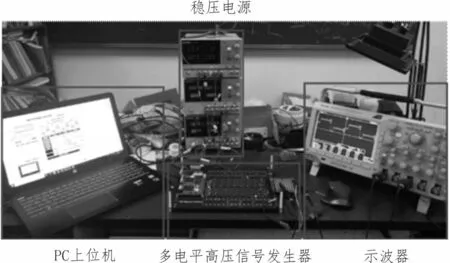

系统测试实物图如图9 所示,包括PC 上位机、稳压电源、示波器和多电平高压信号发生器。PC 上位机通过有线USB 或无线WIFI 连接到多电平高压信号发生器,稳压电源对多电平高压信号发生器供电,示波器探测负载测试板上的输出信号。

图9 系统测试实物图

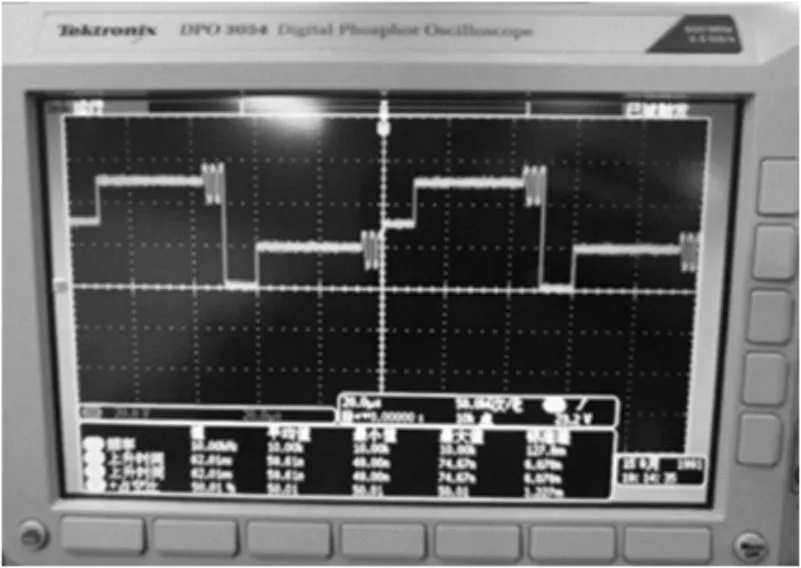

测试时,将示波器的一个通道接入二电平正电压波形,另一个通道接入四电平负电压波形,再利用示波器的减运算功能,即可得到如图10 所示的八电平输出波形测试图。

图10 八电平输出波形测试图

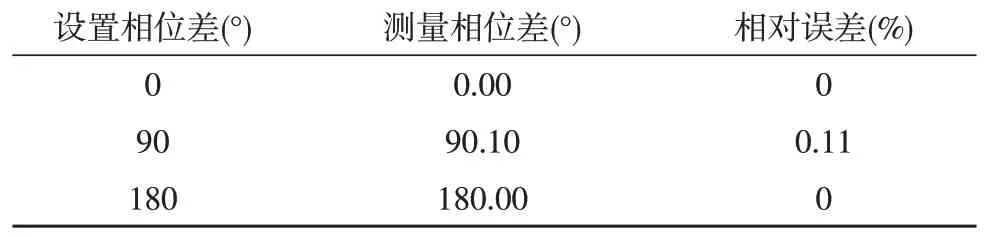

输出信号的频率、占空比和通道间的相位差测量结果如表1~3 所示,由于采用FPGA 进行时序控制,输出信号的频率、占空比和通道间相位差等时序参数的相对误差均精确到0.11%以内。

表1 频率测量结果表

表2 占空比测量结果表

表3 相位差测量结果表

5 结论

文中设计了一种基于FPGA的多通道多电平高压信号发生器,输出信号的频率、占空比、相位等时序参数通过FPGA 控制功率驱动电路输入的PWM 波来调整,输出信号的幅度参数通过外部稳压电源调整,最终实现了针对新型数字微镜器件驱动的64路8 电平60 V 高电压复杂波形信号发生器。