高层次综合技术在遥测地面站数据处理中的应用

迟东明,刘兆辉,王燕玲

(上海航天电子有限公司,上海 201800)

0 引言

遥测地面站所接收的火箭、卫星等飞行器的原始遥测数据中包含有大量的重要遥测信息,如姿态信息、油量信息、位置信息等。地面站需要将这些关键遥测参数从原始数据中提取出来并进行综合、计算,最后将处理的结果显示在终端设备上,以便操作人员进行分析、决策。随着火箭、卫星等飞行器的结构日益复杂,地面站所接收的遥测数据不仅数据量更大,且数据结构更也为复杂,这就对地面站的数据处理能力提出的更高的要求。

地面站对于遥测信息的处理一般采用“FPGA+DSP+通用CPU”或“FPGA+通用CPU”的方式。

“FPGA+DSP+通用CPU”的实现方式中,FPGA负责数据帧检索、重组帧等密集型计算,DSP负责遥测数据计算、数据判断等复杂度较高的计算,而通用CPU负责数据决策、人机交互等。这种实现方式适应面广,但集成度低且功耗较大,不利于地面站的小型化设计。

“FPGA+通用CPU”的实现方式中,如果FPGA负责数据帧检索、重组帧等密集型计算,通用CPU负责其他计算,则FPGA与通用CPU之间需要传输大量数据,对于总线的数据吞吐量及通用CPU的性能提出了极高的要求,不利于地面站低成本设计。虽然目前FPGA内部可以集成通用CPU的IP,但由于通用CPU IP性能较弱,无法满足高速率的遥测数据处理任务。

而如果FPGA负责数据帧检索、重组帧、遥测数据计算、数据判断等,通用CPU负责其他计算,虽然降低了总线及通用CPU的负担,但由于遥测数据处理往往涉及到复杂的数据检索、浮点计算以及数据分析,如果使用传统的基于寄存器传送级(register transfer level,RTL)的设计流程实现遥测数据处理,其代码的设计、调试难度会大大增加,且代码的维护成本也会加大。

本文将FPGA的高层次综合技术(high-level synthesis,HLS)引入到地面站的遥测数据处理中,利用该技术可以将遥测数据处理功能用抽象层级较高的C代码实现,这样就有效降低了FPGA进行遥测数据处理的设计难度,提高了开发效率,从而缩短了产品的研制周期。

1 地面站遥测数据处理流程介绍

地面站的遥测数据处理流程一般是以如图1所示的方式进行[1-2],主要分为5个步骤:

图1 地面站遥测数据处理流程

1)遥测解调。地面站对接收到的无线遥测信号进行解调,并将解调出的遥测数据以数据流形式发送给后端的遥测数据处理模块做进一步处理。

2)遥测帧数据重组。遥测数据处理模块对解调后的遥测数据流进行检索,并根据遥测帧同步头检索出完整的遥测帧,最后根据遥测帧的数据结构进行遥测帧数据重组,从而得到连续的遥测帧。

3)遥测参数提取。遥测数据处理模块根据一定的提取规则,对遥测帧内的遥测参数进行提取,从而得到需要的遥测参数。

4)遥测参数计算。遥测数据处理模块对提取出的遥测参数进行计算及分析,最终得出计算结果。

5)计算结果组帧。遥测数据处理模块将计算结果打包并根据一定的成帧规则形成新的数据帧发送给后端的数据处理模块或终端设备进行后续数据处理或数据显示。

一般情况下遥测数据是以一系列遥测帧的形式进行存储和传输的,如果遥测数据的数据结构较复杂,则每一个遥测帧又可分为一系列不同的遥测子帧,子帧内部的不同区域存放有各类遥测参数或其他数据。换言之,遥测帧一般以二维数据表的形式存放各类参数及数据,而遥测参数则以某一点、某一行(列)或多行(列)的形式分布于该二维表中,其数据结构示意图如图2所示。

图2 遥测数据的数据结构示意图

由于火箭、卫星等飞行器内部包含数量众的多传感器和各类设备,因此其遥测数据的数据结构可能会变得非常复杂。以图2为例,遥测参数集1是遥测帧中子行(列)抽取出来的二维数组,数组中数据可以代表飞行器总线中的某些总线指令,而总线指令在遥测参数集1中的出现的时间以及相对位置可能都不固定,需要遥测数据处理模块通过总线指令的同步头对接收到的每一个遥测帧进行搜索。而搜索到总线指令后,还要对指令进行校验,校验通过后才能提取其中的遥测参数并进行计算。同时在处理遥测帧时也可能需要对遥测帧进行记数操作,以便统计通信状态或超时重传等。

由于飞行器内传感器及设备工作状态各异,其遥测参数的数据类型也千差万别,通常情况下提取出的遥测参数的数据类型并不一致,需要经过一系列变换、统计等操作。比如某遥测帧中的遥测参数就可能包含8位无符号数、16位无符号数、32位单精度及64位双精度浮点数等多种数据类型。

综上所述,在使用FPGA进行遥测参数处理时,会遇到以下两方面的难点:

1)遥测参数的提取涉及到复杂的搜索、判断、校验过程,如果使用RTL级代码实现,其描述工作状态的状态机将异常复杂,相关代码量也将非常大,不利于代码的维护和调试。

2)遥测参数的计算会经常遇到浮点计算、数据类型转换以及复杂公式计算(如正弦、对数计算等),使用RTL级代码进行描述较为困难。

针对以上问题,本文将FPGA高层次综合技术引入到遥测数据处理过程中。利用高层次综合技术对遥测数据进行处理具有以下优势:

1)开发周期短。应用高层次综合技术编写的遥测数据处理相关代码属于行为级描述,抽象层级较高,比较符合高级语言的编程习惯。相对于RTL级的实现方式,其代码精简易懂,也便于修改,因此可以有效缩短产品的开发周期。

2)实时性高。相对于DSP或通用CPU等软件实现方式,应用高层次综合技术编写的遥测数据处理相关代码仍属于硬件实现,延时可控且可以多模块并行处理,实时性高。

3)支持浮点计算。高层次综合技术支持IEEE754标准的浮点数据计算[7,10],且支持标准32位单精度及64位双精度浮点数据类型,因此非常适合描述复杂遥测参数计算。

2 基于高层次综合技术的遥测数据处理

2.1 高层次综合技术介绍

高层次综合(High-Level Synthesis)并不是最近才发展起来的技术,早在20世纪70年代就提出了相关的概念,随着软、硬件技术的不断发展,高层次综合的相关技术才逐步完善、成熟[14]。

对于高层次综合技术的应用,目前国外的相关报道较多,比如基于FPGA或GPU的计算加速[13]、图像处理[11-12]、算法开发[17-18]等。尤其在异构计算方面,利用高层次综合技术能够有效提升异构计算平台的设计、开发效率[20-21]。国内目前高层次综合技术相关报道主要集中于图像处理及算法开发上,在卫星测控领域的应用还较少。

简单来说,高层次综合是一种代码的综合技术,其作用是将抽象层级较高的语言(如C、C++、SystemC、OpenCL等)编写的行为级描述代码自动转换为RTL级代码。而利用高层次综合技术的FPGA开发工具[15-16](如Xilinx公司的VIVADO HLS),除了提供高层次综合的功能外,还提供了如寄存器分配、I/O接口生成、操作调度、状态机生成等诸多功能,有效提高了FPGA设计、开发效率。

利用高层次综合工具进行FPGA设计开发,可以带来以下几方面的优势[19]:

1)开发周期短。高层次综合技术可以屏蔽很多的硬件具体实现细节,使设计师将更多精力放在算法设计、产品功能描述上,从而大大缩短开发周期[5]。根据统计,相对于手工编写RTL级代码,采用高层次综合技术的代码设计效率可以提高约4倍~10倍,结果质量(quality of results,QoR)约0.7倍~1.2倍。

2)测试激励开发效率高。对于FPGA的设计、开发,测试激励(Testbench)的编写非常重要且非常耗时,而高层次综合技术可以将基于高级语言(如C/C++)的测试激励直接用于RTL级代码的功能验证,这就有效提高了代码验证的效率。

3)便于代码的修改和维护。由于基于高层次综合技术编写的代码是属于行为级的描述,其抽象层级较高,便于设计师的阅读理解,也便于代码的后期维护。

基于高层次综合技术的特点,其非常适合应用于卫星、火箭等飞行器的遥测数据处理过程中(如遥测参数的提取、计算、重组等过程)。

2.2 遥测数据处理模块的对外接口设计

为了实现对遥测参数的处理,首先需要对遥测数据处理模块的对外接口进行定义。这里使用的开发平台为Xilinx公司的VIVADO HLS[3-4,8],且使用C语言对遥测数据处理模块的功能及接口进行描述。

假设所有遥测数据均以1Byte为单位存储于遥测帧中,而遥测帧是一种M*N的二维表格,经过遥测数据处理模块的处理后会生成一个长度为L的一维数据帧输出给后续处理模块。遥测数据处理模块的对外接口定义如图3所示。

图3 遥测数据处理模块对外接口定义

其中input_data为unsigned char类型的二维数组,用于存放接收到的遥测帧;output_data为unsigned char类型的一维数组,用于存放处理后的数据帧;tm_process_block为该遥测数据处理模块函数名,经过VIVADO HLS综合后会转换为相应的RTL模块。

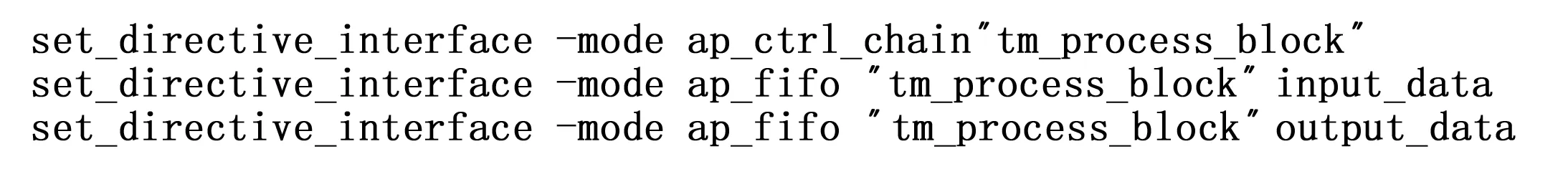

由于遥测帧内部数据是按照地址的先后顺序输入到遥测处理模块的,不存在随机访问情况,输出结果也是如此,因此可以将模块的对外接口理解为一个FIFO,而在VIVADO HLS中可以使用约束语句对其进行约束。

为了使VIVADO HLS能够正确识别对外接口的输入输出关系和具体接口形式,需要在代码中添加相应的约束语句,具体如图4所示。

图4 遥测数据处理模块的外接口约束

其中,第一条约束语句用于指导VIVADO HLS为遥测数据处理模块添加模块级握手信号。模块级握手信号用于控制和监测模块的工作状态,以便于不同模块之间的数据交换;第二、三条约束语句用于通知VIVADO HLS对input_data、output_data采用FIFO接口形式。

图5为经过VIVADO HLS综合后生成的遥测数据处理模块的对外接口,可以看出主要分为三部分:输入接口、输出接口以及相关的握手信号。

图5 遥测数据处理模块的硬件接口

2.3 基于高层次综合技术的遥测数据处理的设计与实现

前文简要介绍了对卫星、火箭等飞行器的遥测数据的处理过程,而使用高层次综合技术对遥测数据进行处理,主要的技术难点在于如何使用高级语言描述遥测数据的数据结构,以及如何使用高级语言描述遥测数据的处理过程。

从前面的分析可以看出,遥测数据的数据结构可以由高级语言的一维或二维数组描述,并且可以很方便地对数组中的指定数据进行寻址访问,而遥测数据的处理过程可以使用高级语言的循环、条件判断等常用的语句描述,其工作流程如图6所示。具体描述如下:

图6 遥测数据处理模块工作流程图

1)对input_data、output_data以及其他用于存放中间结果的临时数据缓冲区进行初始化,可以使用For循环完成。如输出结果中还要包含帧计数功能,则初始化帧计数相关变量。

2)将input_data中的遥测帧数据拷贝到临时数据缓冲区中。由于遥测帧是二维结构,存放遥测帧的缓冲区可以声明为unsigned char类型的二维数组,并使用二级For循环实现数据拷贝。

3)校验遥测帧内部数据(如奇偶校验、CRC校验),如果校验正确则进行下一步处理,如果校验不正确则返回FALSE,表明本次遥测帧处理失败。

4)遥测参数提取。该过程实际上就是对二维数组的访问过程,将二维数组中指定遥测数据拷贝到临时数据缓冲区,或按照一定规则在二维数组中指定区域搜索指定的遥测参数集再进行进一步处理。

5)遥测参数计算。对提取出的遥测参数进行计算,并将计算结果保存到临时缓冲区。

6)将遥测参数计算结果保存到临时缓冲区,并根据一定的规则重新组帧,同时将计算结果填入帧内。如输出结果中需要有帧计数功能,则将帧计数变量加1并填入帧内相应位置。

7)根据一定规则计算输出帧的校验和并填入输出帧的相应位置。

8)将临时缓冲区中的输出帧拷贝到output_data中,该过程可用For循环实现,最后返回TRUE,表明本次遥测帧处理成功。

遥测地面站在输出处理结果时经常需要标记当前输出帧的帧序号,以便于后端设备根据帧序号进行通信握手或误码统计,这就要用到帧计数功能。帧计数变量需要在不同的遥测帧处理过程中持续保持更新,而不像其他变量那样每次处理过程都置零或恢复初始状态,因此帧计数变量需要设置为static类型,这样帧计数变量就可以保持上一次调用遥测数据处理模块时的状态。

对于浮点计算,VIVADO HLS支持标准IEEE754浮点数(32位单精度及64位双精度浮点数据类型)及相关浮点计算。因此使用高层次综合技术实现遥测参数的浮点计算非常简洁、高效。以标准32位单精度浮点数为例,配合C语言的强制类型转换及位操作便可以实现复杂的浮点计算。

这里假设提取遥测帧中的11行85列的遥测参数(unsigned char类型),将该参数进行浮点计算(float类型)并将计算结果存储到输出帧中的[10:13]位置,其实现代码如图7所示。

图7 浮点计算实现代码示例

可以看出基于高层次综合技术的浮点计算代码非常简洁,遥测数据的寻址、浮点运算等只需一条语句描述,将计算结果存储到输出帧中也仅需要简单的移位、强制类型转换等操作完成,而如使用RTL方式实现相同功能,则代码量将大大增加。

3 测试结果与分析

本文将以上描述的遥测数据处理模块使用VIVADO HLS进行了设计、仿真,同时将转换的RTL代码进行了硬件测试。代码在VIVADO开发环境[9]中进行综合、布局、布线,最后在Xilinx公司的XC7A200T[6]平台上进行了硬件测试。

硬件测试过程中,遥测数据处理模块对96 Byte*64 Byte的遥测帧进行处理,输出帧长度为360 Byte。处理过程涉及到若干次的参数集提取、浮点计算以及校验和计算等操作,模块工作时钟为10 MHz。

图8为该模块的FPGA资源占用情况,LUT及DSP资源占用率分别为5%和1%。可以看出其 FPGA资源占用率是非常低的。

图8 遥测数据处理模块FPGA资源占用情况

图9是遥测数据处理模块的时钟及延时情况。可以看出,该模块最高工作频率可以达到11.2 MHz,延时最高为24 367个时钟周期,约2.4 ms,因此理论上达到400帧/s的处理速度。由于遥测数据处理模块使用的是FPGA的基本逻辑资源,因此也可以多个模块并行处理遥测数据,以适应更高速的遥测数据处理需求。

图9 遥测数据处理模块时钟及延时情况

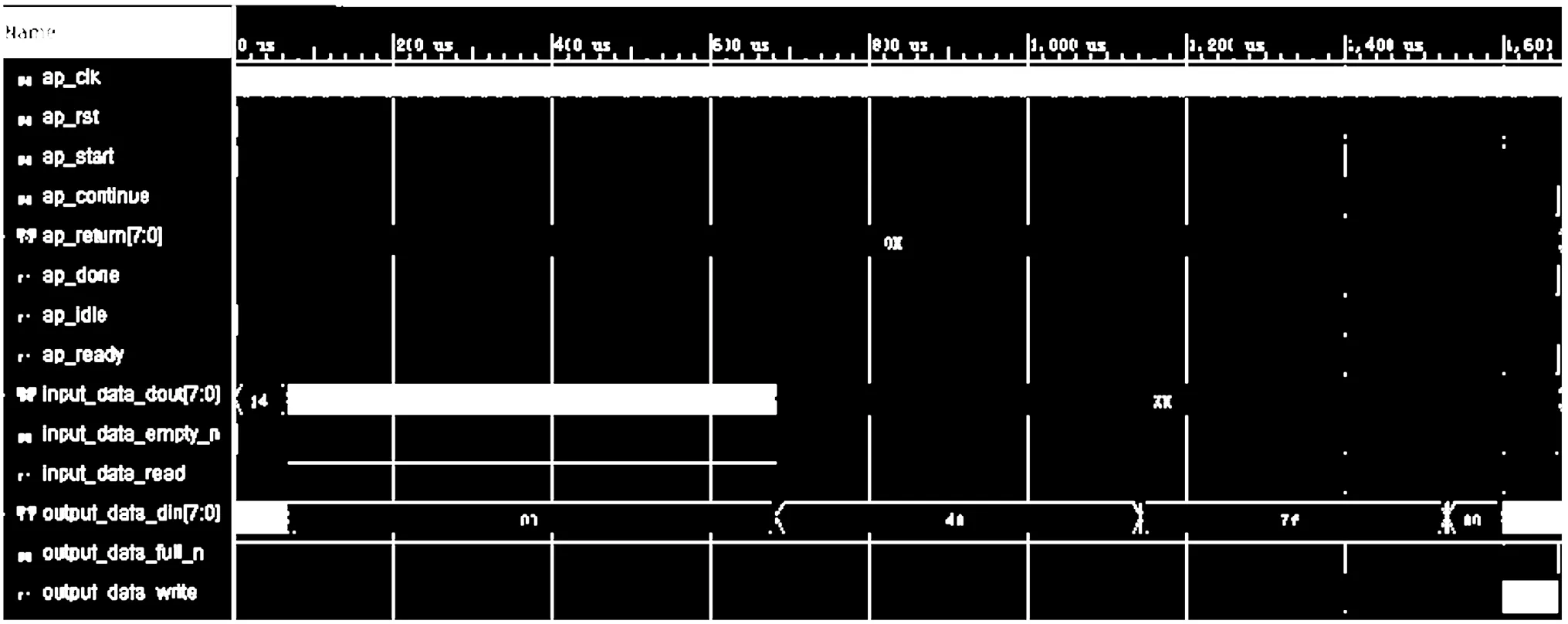

图10是遥测数据处理模块接口部分的RTL级仿真图。可以看出,当遥测帧输入到模块后,经过一定的处理周期,模块输出处理结果,RTL级仿真结果与行为级仿真一致。

图10 遥测数据处理模块接口部分RTL仿真图

从开发周期上进行对比,应用高层次综合技术,整个模块从代码设计、仿真直到最后的硬件测试仅仅耗费了1周的时间,而如果使用传统的RTL开发流程,保守估计预计要耗费2个月的时间。

从代码量上进行对比,由于模块是基于C语言描述的,其抽象级别较高(行为级描述),因此相关代码极为精简,模块主体代码量仅300行左右,加上Testbench的代码量为500行左右。与之对比,如果采用基于RTL的设计流程,整个设计的代码量预计要增加10倍以上。

4 结束语

综上所述,使用高层次综合技术对遥测数据进行处理,在同样满足设计要求的情况下,其设计、开发效率要远远高于传统的基于RTL的开发流程,同时也在很大程度上减轻了设计工程师的工作量。

目前高层次综合技术主要应用在图像处理、数据编解码[11-12]等领域,而在卫星测控领域的应用报道还很少。本文将高层次综合技术应用到地面站的遥测数据处理过程中,证明了利用高层次综合技术可以有效提高卫星测控产品相关FPGA的设计、开发效率,缩短产品的研制周期,因此具有推广价值和参考价值。