多模数转换器并行接口的FPGA 设计与实现

陆 鹏,王 晶,臧 越

(中海油田服务股份有限公司,天津 300450)

在井下仪器项目开发中,地层响应信号较微弱(10~100 nA 级)且环境噪声较大,加上对高测速的需求,因此在进行信号采样时需要较高的精度和速度。此外,仪器使用了多频率的发射信号和多个接收电极,因而需要使用多通道的采样电路进行信号采集。

为实现高速高精度多通道采样,需要具有高采样率和高位数的ADC 器件以及能够实现高速采样的多通道接口电路。因FPGA 器件具有高速、可重构性、管脚丰富等特点,因此设计中使用FPGA 来实现ADC 的接口电路。文中基于ADI 公司的ADC——AD7674 进行FPGA 并行接口设计,最终实现多通道的高速高精度数据采集。

1 AD7674简介

AD7674 是ADI 公司生产的18 位分辨率、最大非线性积分误差2.5LSB、最高800 kSps 采样率的单通道全差分输入ADC[1]。它采用逐次逼近型(SAR)结构,具有低功耗、高精度、无延时等特点。AD7674 有WARP、NORMAL、IMPULSE 3 种转换模式,在WARP模式下采样率最高可达800 kSps。

数据通信接口有并口模式(8 位、16 位、18 位总线)和SPI 串口模式。采用SPI 串口通信的设计如文献[2-3]中所讨论,这种方式具有占用管较少、连接简单等优点,但传输速度受限于串行时钟SCLK,如当传输18 位串行数据时需要18 个SCLK 时钟;而采用并口通信时,18 位采样数据同时出现在并口总线,一个时钟即可读取,速度上有明显优势,而缺点是占用管脚较多、连接较复杂。

在测量精度方面,当参考电压为2.5 V时,AD7674的最小量化电平为9.5 μV,误差为±23.8 μV,远低于目标信号最小幅值,完全满足测量要求。

为实现高速采样,文中采用了WARP 转换模式及18 位并口数据通信模式。

2 AD7674接口工作原理

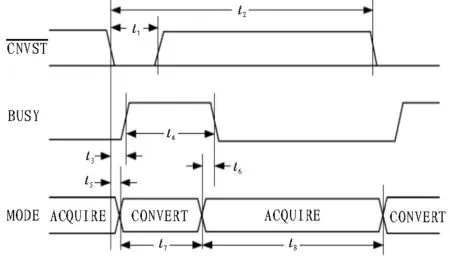

AD7674 的内部结构和转换原理在文献[1-2]中均有介绍,这里不再赘述。为实现AD7674 的FPGA接口,重点介绍其接口工作原理。设计中将AD7674的接口分为模数转换控制和数据读取控制两个部分进行分析[4]。

图1 模数转换时序

图2 从机读并口时序(转换结束后读数据)

AD7674 使用WARP、IMPULSE 两根信号线来设置转换模式,当使用WARP 模式时,WARP=1、IMPLUSE=0。使用MODE0、MODE1、D0/OB/、PD等信号线来设置通信接口模式、数据输出格式、低功耗模式等。当使用18 位并口时,MODE0=0、MODE1=0,D0/OB/在此模式下为并口总线的Bit0位,数据输出格式为标准二进制格式。这些信号可以通过在AD7674引脚设置固定电平的方式来配置,也可以将其与FPGA 的引脚相连,通过FPGA 来配置,这样的优点是能够根据需要灵活更改ADC 配置。

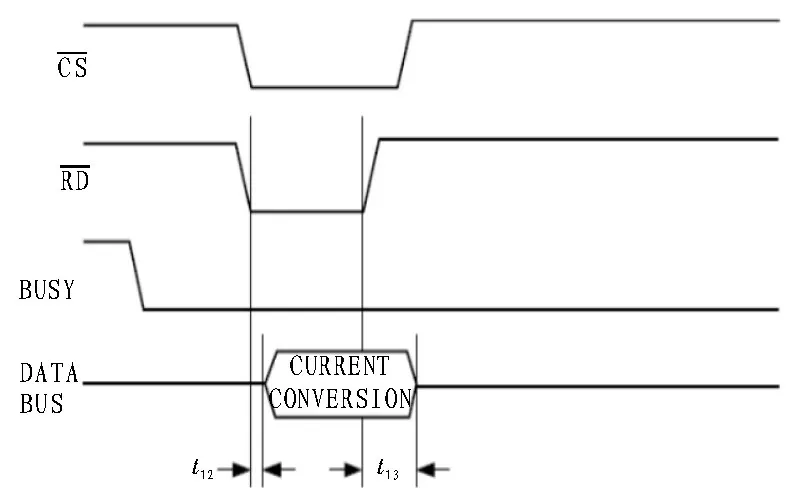

3 多通道接口设计

由于AD7674 为单通道输入,因此若要实现多通道的信号采集,则需要多片AD7674。ADC 的接口设计就是对其控制信号的设计,根据其工作时序在FPGA 上实现相应的信号及逻辑。多通道接口的设计难点在于如何实现在多个ADC 情况下进行有序高效的数据读取[5]。文中根据AD7674 的特性,采用单独使能信号轮询ADC 的方法,进行多ADC 的数据读取[6-7,14]。

以两ADC 并行接口设计为例,AD7674 的控制信号按照图3 的方式与FPGA 进行连接。

图3 两AD7674与FPGA的信号连接

4 FPGA设计实现

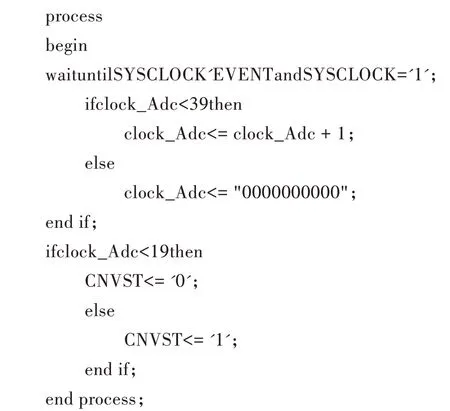

FPGA 设计实现根据AD7674 的接口原理亦分为模数转换和数据读取两部分进行。文中程序代码使用VHDL 语言[10]。

结合图3,SYSCLOCK(系统时钟)、Din(18 位并行总线)以及ADC_Busy 信号为FPGA 输入信号,其他信号均为FPGA 输出信号,模块的端口代码如下:

数据读取部分根据AD7674 的并口时序,当检测到BUSY 信号为低时,将信号置低,开始准备进行数据读取,接着按需要将指定ADC 的信号置低。在信号变低的t12时间后,ADC 会将当前的转换结果输出到并口总线上,此时FPGA 可以进行数据的读取。待完成此ADC 的数据读取后,置高该信号,同时使能下一个ADC 的信号,进行下一个ADC 的数据读取。如此循环,实现ADC采样数据的读取。

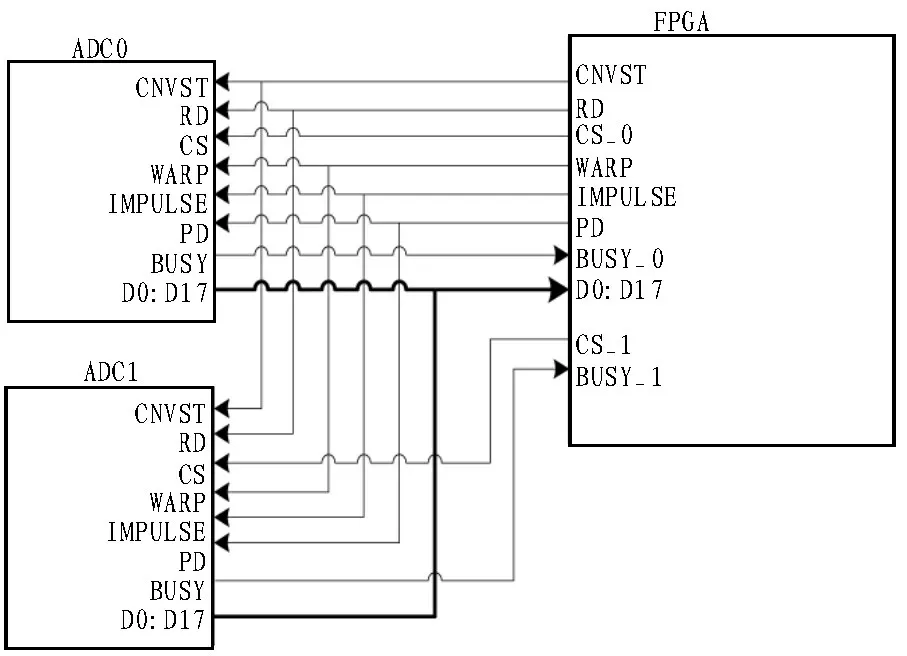

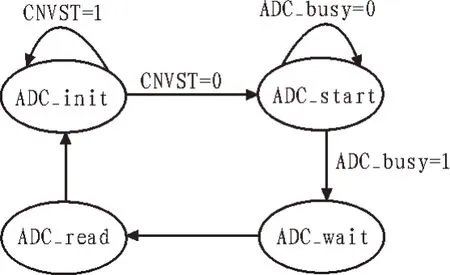

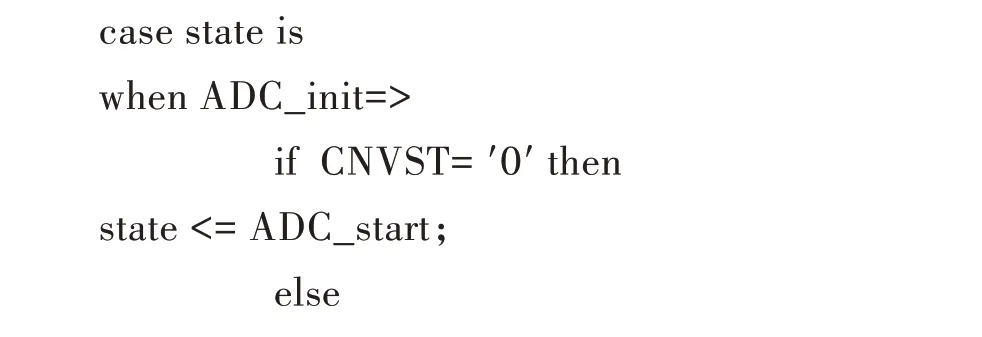

以上逻辑采用状态机的方式实现,状态转移图如 图4 所 示,分 为ADC_init、ADC_start、ADC_wait、ADC_read等状态[13]。数据读取状态机实现代码如下:

图4 数据读取状态转移图

5 仿真结果

假设被测信号频率为100 kHz,后期处理需要进行8 点FFT 计算,则采样时钟需要800 kHz,AD7674最大采样率为800 kSps,因此能够满足要求。当系统时钟为32 MHz 时,进行40 分频可得到800 kHz 的采样时钟。

在仿真testbench 中,对输入型信号进行如下配置:SYSCLOCK 为32 MHz;Din 采样输入值设定为模拟值;ADC_Busy 信号在下降沿t3时间(35 ns)后产生;脉冲宽度为t4(1 μs)。

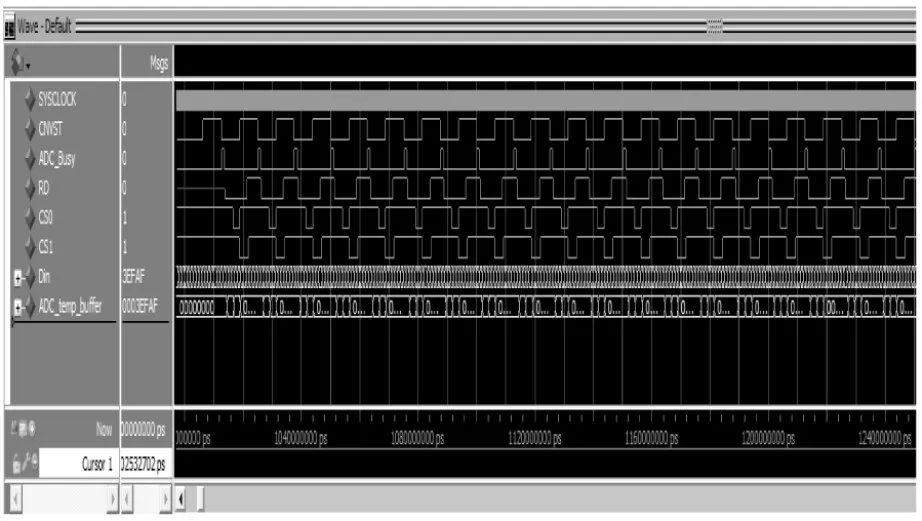

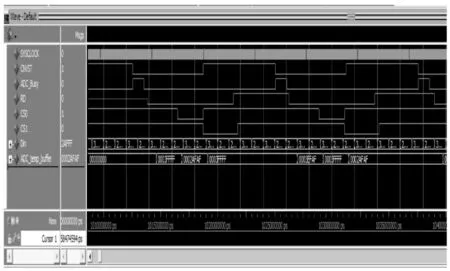

使用testbench 在ModelSim 仿真软件中对FPGA接口程序进行仿真[15-16],仿真结果如图5、图6 所示。

图5 总体仿真波形

图6 起始部分仿真波形

分析仿真波形可知,SYSCLOCK 频率为32 MHz,采样时钟输出为800 kHz(占空比为50%)。ADC_Busy 信号在下降沿后35 ns 产生上升沿,RD 读使能信号则在ADC_Busy 下降沿120 ns 后置低,此时开始准备读取AD7674 并口数据。RD 置低240 ns 后,开始置低CS0,使能ADC0 数据输出,此时ADC0 的18 位并行数据出现在总线上,在请求到数据有效45 ns(t12)后,读取数据到FPGA 内部的18位Buffer,完成采样数据存储。CS0 持续2 μs 后,置低CS1,开始使能ADC1,按同样方法处理ADC1 的并行数据。上述工作均在的一个时钟周期内完成,而且数据读取处理的时间裕度较大,能够保证程序运行的稳定性。

以上结果表明,程序实现了目标逻辑,符合AD7674的工作时序要求,能够有效稳定地读取多ADC 的并口数据。将程序综合编译并下载到实际的电路中进行测试,亦能得到正确的结果。

6 结论

文中首先介绍了AD7674 的特点和接口工作原理,然后详细分析了其接口工作时序,通过采用单独使能信号轮询ADC 的方法,实现多通道的并口数据读取。文中给出了基于该思路下两ADC 并行转换接口的FPGA 代码,并给出了仿真结果。

设计中需要注意的是,FPGA 输出信号的时间要求应符合ADC 的工作时序,否则会出现数据读取异常错误。另外,如果将文中方法应用在其他ADC,则需注意其信号是否对转换有影响,当禁止时,ADC 会停止转换,则文中方法不适用。

文中介绍的FPGA 接口设计方法可应用到逐次逼近型ADC 的采集驱动中,适用于多通道高速高精度的信号采集等场景。