HIAF-Kicker电源通信系统设计与实现

刘 艳 高大庆 张华剑 李继强 高 杰 上官靖斌 李明睿 金雪剑

1(中国科学院近代物理研究所 兰州 730000)

2(中国科学院大学 北京 100049)

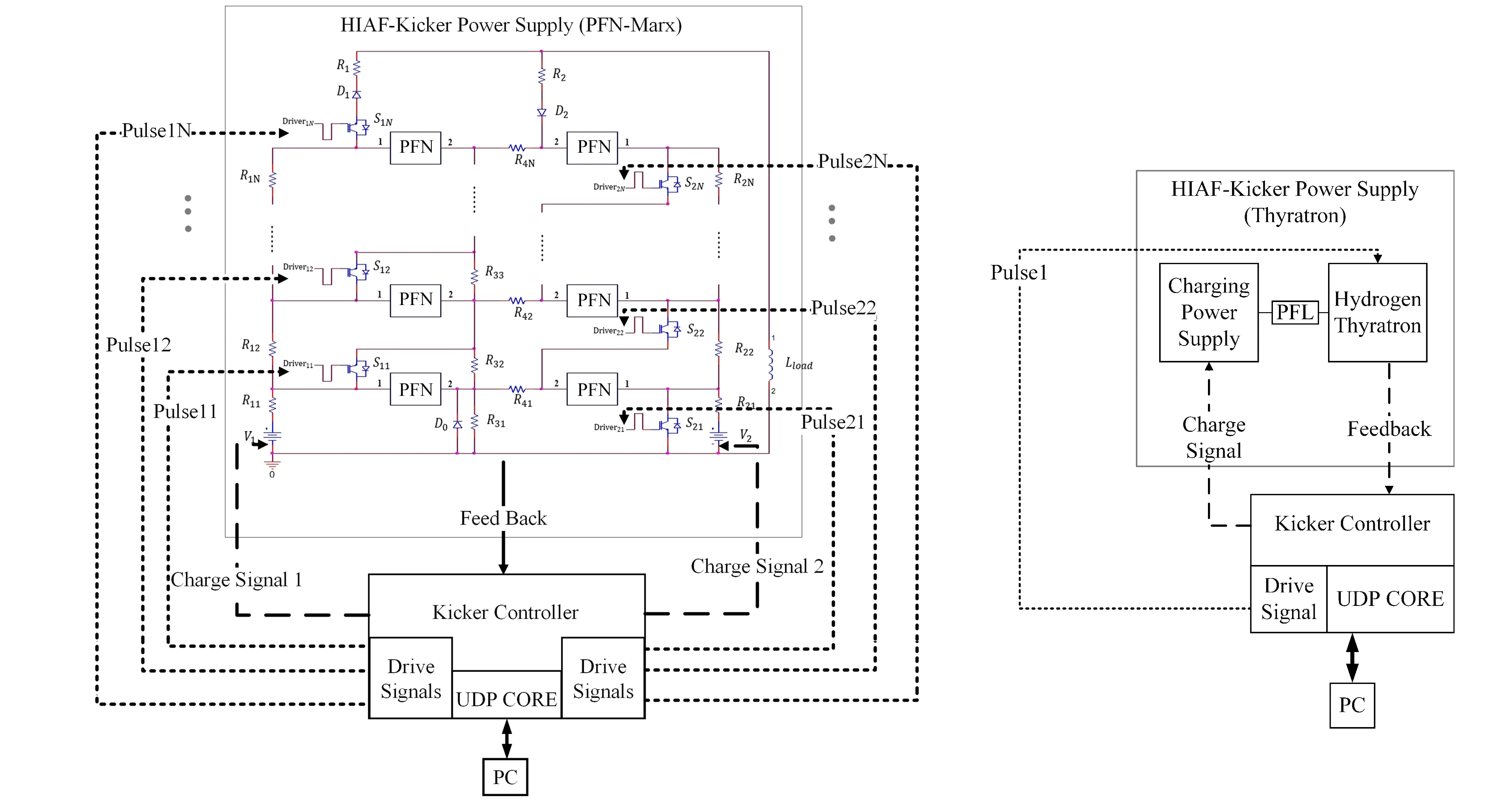

Kicker电源是强流重离子加速器(High Intensity Heavy-ion Accelerator Facility,HIAF)实现束流快速注入引出的关键设备之一。HIAF-Kicker电源由多个Kicker电源模块组成,电源模块全部放置在加速器隧道外电源间内,通过传输电缆与负载磁铁相连接。单模块Kicker电源采用氢闸流管作为放电开关和脉冲形成网络(Pulse Formed Net,PFN)结合固态马克斯(Marx)发生器技术[1]的两种方案来获得脉冲励磁电流,单模块电源工作方式如图1所示。

图1 HIAF-Kicker单模块电源工作框图Fig.1 The working block diagram of HIAF-Kicker single module

HIAF-Kicker电源对通信系统提出了以下要求:

1)单个双极性固态PFN-Marx发生器中绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor,IGBT)数量庞大,目前使用64个,之后最大扩充至160个。Kicker电源通信系统需要通过网络将上位机设定的160路IGBT的周期、延时、脉宽控制参数(大小约1.875 KB)精确下发至每个IGBT开关,完成多路开关的驱动控制。

2)HIAF-Kicker电源输出波形速度快,上升、下降时间在几十纳秒到百纳秒范围内,平顶宽度约为几个微秒。HIAF计划采用2.5 GSPS采样率、12 bit精度的单通道模/数转换(Analog-to-Digital Converter,ADC)采集卡对每台Kicker电源波形进行采集,并将多台Kicker波形数据在控制器汇总后通过通信系统回读至上位机。为了缩减数据量,高速采集卡拟采用截取包含波形脉冲及其前后部分进行传输的方案,截取波形部分不超过周期的千分之一,即单个Kicker采集卡每秒获得有效数据量最大约3.6 MB。根据HIAF设计要求,单个电源间内的Kicker电源最多为13台,因此通信系统每秒回读的最大波形数据量为46.8 MB,即传输速率为374.4 Mbps。为方便将来提升波形采样速率,并为Kicker波形数据添加控制信息留出余量,要求通信系统预留千兆级波形数据回读通路。

3)Kicker电源高电压大电流工作方式对通信系统会造成一定的电磁干扰,要求通信系统工作稳定。

在加速器注入引出电源系统中有多种数据通信方式。德国重离子研究中心、大型强子对撞机(Large Hadron Collider,LHC)系统和上海同步辐射光 源(Shanghai Synchrotron Radiation Facility,SSRF)采用分布式机箱、现场总线和基于德国西门子(SIEMENS)公司的可编程逻辑控制器(Programmable logic Controller,PLC)的方案用于快Kicker磁铁和电源的互锁控制[2-5]。兰州重离子加速器冷却储存环(Heavy Ion Research Facility in Lanzhou,HIRFL)Kicker电源控制器采用内嵌微处理器(Advanced RISC Machine,ARM)的现场可编程门阵列(Field Programmable Gate Array,FPGA)为核心处理单元[6],通过软件操作方式进行数据通信。其中PLC和分布式机箱应用广泛,但灵活性不足,且不适用于特殊控制场合。采用可编程片上系统(System On a Programmable Chip,SOPC)技术和内嵌ARM处理器的FPGA方案能提升系统集成度、有效减小硬件的尺寸和功耗[7],但会大大消耗系统资源、降低CPU的工作效率[8]。而FPGA硬件描述IP核(Intellectual Property Core)的并行处理结构可以提高数据的传输和处理能力,因此HIAF-Kicker控制器内部通信和逻辑单元全部采用硬件描述语言处理方案。在工业控制领域通信协议方案中,Modbus因传输速度慢、距离短而应用受限。Modbus/TCP将Modbus协议嵌入到TCP协议的应用层,传输可靠性高,然而其采用轮询式闭环的通信方式,传输效率较低[9],实时性不能满足HIAF-Kicker的需求。TCP协议适用于可靠性要求高的应用环境,UDP协议没有TCP协议的3次握手、确认应答等环节,因此速度更快,且在点对点传输应用中可靠性较高。此外,由于TCP协议通信方式复杂,通过硬件描述方式实现难度较大,而UDP硬件设计的方案复杂度低、易于实现[10]。因此采用UDP硬件描述协议栈的通信方式更适用于HIAF-Kicker电源通信的需求。本文介绍了基于Xilinx Kintex-7 FPGA可编程硬件平台,采用HDL硬件描述UDP协议栈的HIAFKicker电源通信系统,并通过多路IGBT通信功能测试、参数收发稳定性测试、回读通路速率测试,验证该系统满足HIAF-Kicker电源通信需求。

1 HIAF-Kicker电源通信系统

1.1 基于HDL硬件描述语言的UDP核

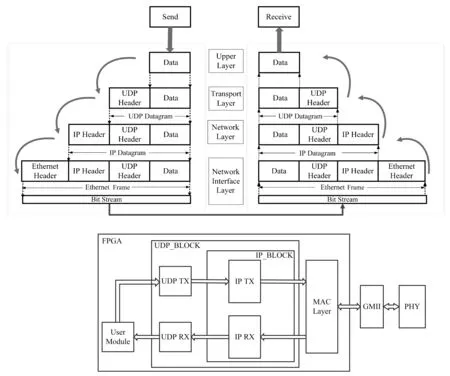

TCP/IP是当今计算机网络界广泛使用的协议,分为应用层、传输层、网络层和网络接口层。UDP协议属于TCP/IP结构体系的传输层协议。Kicker通信系统百路IGBT控制参数下发和高速波形数据回读保留不同的传输通路,两种数据通路都基于相同原理的UDP核作为数据通信控制单元。UDP核原理图如图2所示,其中UDP核内的数据发送和接收实际是一个打包和解封的过程,发送时将原始数据按照TCP/IP规定模型从内到外依次添加当前分层所必须的“首部”信息,最终将打包好的以太网帧发送到物理层通过网络传输出去,数据接收过程则顺序相反[11-12]。

图2 基于HDL硬件描述语言的UDP核原理图Fig.2 The principle framework of HDL based UDP core

系统采用分层模块化设计,既保证设计的稳定性,同时提高系统的可维护性[13]。基于HDL硬件描述语言的UDP核从上到下分为UDP模块、IP模块和MAC层模块。其中,MAC层通过千兆媒体独立接口(Gigabit Medium Independent Interface,GMII)和88E1111以太网芯片进行数据传输。当数据从主机通过网络介质传输至本地控制器时,MAC模块将经过地址匹配后的数据传输至网络层IP模块。IP数据报包含版本、首部校验和、源地址和目的地址等信息。UDP TX将数据通过源端口发送出去,而UDP RX通过目标端口接收数据。在接收数据时UDP模块通过125 MHz数据收发时钟接收从IP模块传达的8 bit的字节流,然后将这8 bit数据流在User Module中进行格式重组、解析和数据分发。

硬件UDP核由于可调用函数资源较少,为保证逻辑功能完整需要消耗较多芯片资源。为了提高运行的稳定性,硬件方案选用高性能、高性价比的Xilinx Kintex-7 FPGA器件,其相比于传统FPGA资源丰富,有利于减小因为逻辑资源短缺带来的故障风险。此外,Kintex-7 FPGA内嵌入了数字信号处理单元(Digital Signal Processing,DSP)、高速串行扩展总 线(Peripheral Component Interconnect Express,PCIE)、高速收发器(Gigabyte Transceiver,GTX)等,便于升级优化。各模块采用FPGA并行处理方式,模块间相对独立、通过模块例化方式进行不同层级数据流控制。每个协议层模块根据相应协议处理各自数据,并使用有限状态机控制数据的处理流程。图3以百路IGBT控制参数下发通路中的通信控制单元为例,主要包含:TOP模块、UDP模块、IP模块,每个模块初始运行在IDLE循环等待模式下,当接收到上位机发送的参数时,每个模块内部根据设定状态图流程处理各自数据,直至当前层数据输出则回到原始状态,如此循环。

图3 数据接收状态图Fig.3 The state chart diagram of data receiving

1.2 HIAF-Kicker电源通信系统结构

在保证UDP核稳定运行的基础上,电源通信系统还需要考虑系统集成度、数据收发稳定性等关键问题。为此,系统基于中国科学院近代物理研究所自主研发控制器,通过以太网物理层收发芯片88E1111、RJ45接口连接千兆网线与PC操作软件进行数据通信。此外,为了适应HIAF-Kicker高压强电磁干扰的工作环境、提高数据传输的稳定性,采用光纤触发模式进行IGBT开关控制。具体控制结构为:单模块Kicker电源内采用主控制器加多模块光纤扇出子卡的结构。控制器预留多组光纤子卡接口、每个接口包含4个IO输出端口,可根据所需控制信号数量不同增减子卡数量,子卡配备HFBR2522Z光电接收器和HFBR1522Z光电发射器。同时对控制器外加屏蔽壳以减少电磁干扰、增强了系统的稳定性。

通信系统的结构如图4所示。其中,DATA STREAM1为电源控制参数下发通路,由上位机操作软件写入参数、通过千兆网线由RJ45和以太网芯片传输至数字控制器FPGA内部,UDP Receive模块接收、处理参数后将其传给Logic1模块,Logic1模块经过计算缓存后把数据分发给不同光纤扇出子卡,最终光纤扇出子卡输出光控制信号至各自连接的IGBT驱动,由驱动控制电源的各个IGBT开关。DATA STREAM2为预留的高速波形数据回读通路。其中,UDP Receive和UDP Send分别为控制参数下发通路和波形数据回读通路中的通信控制单元。

图4 HIAF-Kicker电源通信系统结构图Fig.4 The structure diagram of HIAF-Kicker communication system

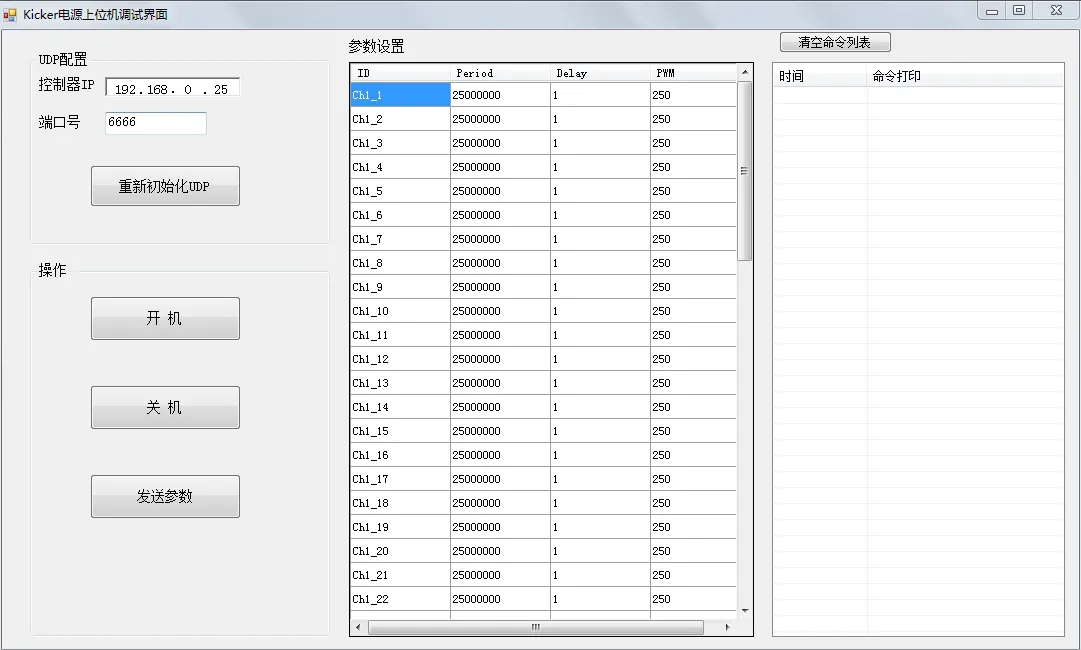

1.3 Kicker电源上位机操作软件

根据HIAF-Kicker电源多路IGBT的控制需求,Kicker电源上位机采用Socket套接字通信机制和C#网络编程技术实现。操作软件主要由控制器端口信息设置区、电源开关机按键、电源配置参数设置区、信息打印区4部分组成。通过C#网络编程技术完成UDP数据发送和接收,设计流程包含:创建Socket、设置服务端信息、监听客户端、创建链接、接收、发送数据、结束几个环节,上位机界面如图5所示。

图5 Kicker上位机用户界面Fig.5 User interface of Kicker software in host PC

2 系统测试

2.1 HIAF-Kicker电源多路IGBT控制参数通信测试

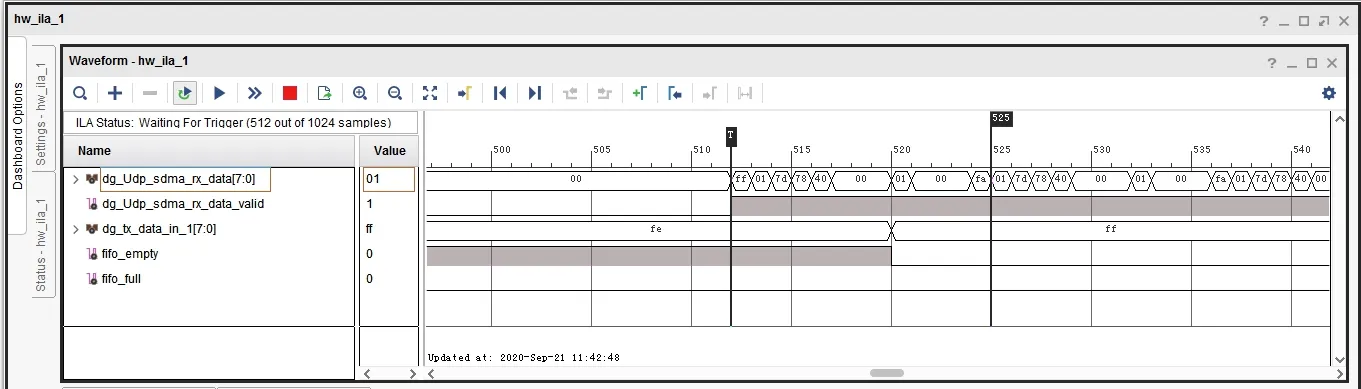

如图6所示,通过Vivado ILA逻辑分析仪观测从Kicker上位机发送至FPGA内的控制参数。ILA触发后在Udp_sdma_rx_data端口接收到的第一组数据分别为ff(标志位)、01、7d、78、40;00、00、00、01;00、00、00、fa;与图5配置的Chl_1 Period(周期)、Delay(延时差)、PWM(Pulse Width Modulation,脉冲宽度调制)3个参数:25 000 000、1、250的十六进制格式一致,表明多路IGBT控制参数下发、解析成功。

图6 ILA接收数据观测Fig.6 Receiving data observed in ILA

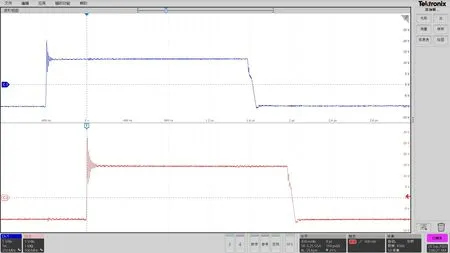

图7以HIAF-Kicker电源PFN-Marx发生器两路IGBT驱动控制为例。Kicker上位机发送chl_1控制参数为:周期(Period)为1 s,脉宽(PWM)为2μs,延时差(Delay)为1 ns;chl_2参数为:周期(Period)为1 s,脉宽(PWM)为2μs,延时差(Delay)为400 ns。图7中结果显示:通信系统完成上位机与HIAFKicker电源的数据通信,满足多路IGBT开关精确控制功能。

图7 上位机控制Kicker IGBT驱动板波形输出Fig.7 Output waveform of Kicker IGBT driver controlled by host PC

2.2 参数收发稳定性测试

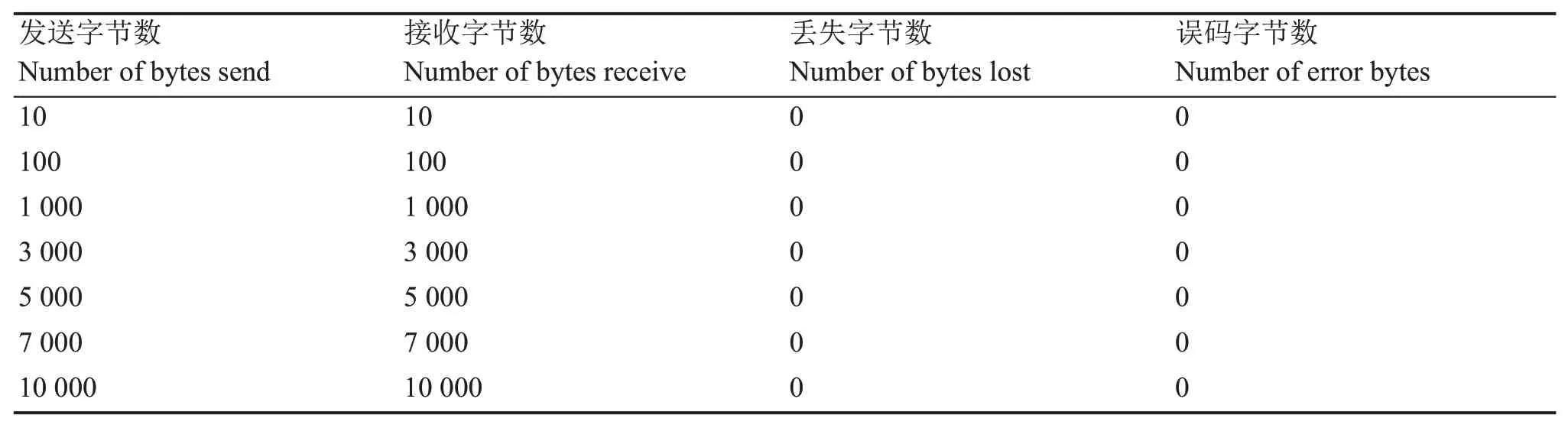

通过网络调试助手对IGBT参数下发通路进行7次不同数据量的UDP回环测试。为了模拟HIAFKicker高压强电磁干扰的工作环境,测试在HIRFLCSRe Kicker电源间进行。测试结果如表1所示,该结果显示在Kicker高压强电磁干扰环境下多次参数收发过程中无数据丢失与误码现象,满足系统在实际电源参数下发操作中的稳定性需求。

表1 参数收发稳定性测试Table 1 The stability test of Kicker parameters sending and receiving

2.3 数据回读速度测试

通过抓包工具Wireshark对系统回读通路中数据发送速度进行测试,具体过程如图8所示。在回读通路中,当UDP Send模块连续发送3 236个数据包至上位机时,Wireshark软件抓取3 236个数据包用时0.028 282 s,其中,每个数据包包含有效数据为1 023个字节,通过计算得传输速率(传输速率=数据包个数×单数据包字节数×8/传输时间)约为936.406 Mbps,测试结果表明该系统满足HIAFKicker电源在高速采集波形回读应用中千兆级通信速率的要求。

图8 Wireshark软件抓包测试回读速率Fig.8 Communication test of readback rate by Wireshark software

3 结语

基于硬件语言描述UDP核的HIAF-Kicker电源通信系统具有高速、高稳定性、低资源等优点。通过对多路IGBT控制参数通信功能测试、参数收发稳定性测试和数据回读通信速率测试验证该系统满足HIAF-Kicker电源的通信需求。下一步计划将该系统的通信软件进行优化升级,并在HIAF-Kicker高速波形采集系统设计完成后进行实际的波形回读应用。