一种典型功率运算放大器芯片粘接故障分析及改进

刘岗岗,蔡景洋,谢炜炜

(贵州振华风光半导体有限公司,贵州贵阳,550018)

1 概述

0041 型功率运放是通用丙类功率运算放大器,具有较大输出电流,适用于马达驱动电路。某批次0041 产品使用时,存在部分产品进行系统测试出现“输入10V 信号,输出电压负满偏为-14V,正常为-2.4V;输入-10V 信号,输出电压2.4V,正端输出正常”信息。对故障样品进行分析可知开封后电测内部电路可知Q1上B-C串阻为268Ω,基极-发射极无串阻,目检样品键合良好。运放芯片及Q1~Q4 晶体管芯片玻璃钝化层完整,金属化良好,未见明显过电损伤或机械损伤,仿真分析确认失效样品失效由Q1 管集电极串阻引起。切片分析Q1 背金界面未见裂缝、空洞、腐蚀等异常形貌,银浆银颗粒分布不均匀。将编号分别为230#(故障样品)和3449#(未装机样品)的两样品返厂测试和分析。

2 产品结构分析

■2.1 引脚功能简介

0041 型功率运放产品采用T0-8-12 金属圆壳封装,各引脚功能如表1 所示。该款功率运算放大器最大输出电流200mA,封装形式与MSK0041 基本一致。电路具有输出过载保护功能,采用补偿电容消除寄生振荡、确保电路稳定工作。

表1 产品引脚功能表

■2.2 产品内部结构

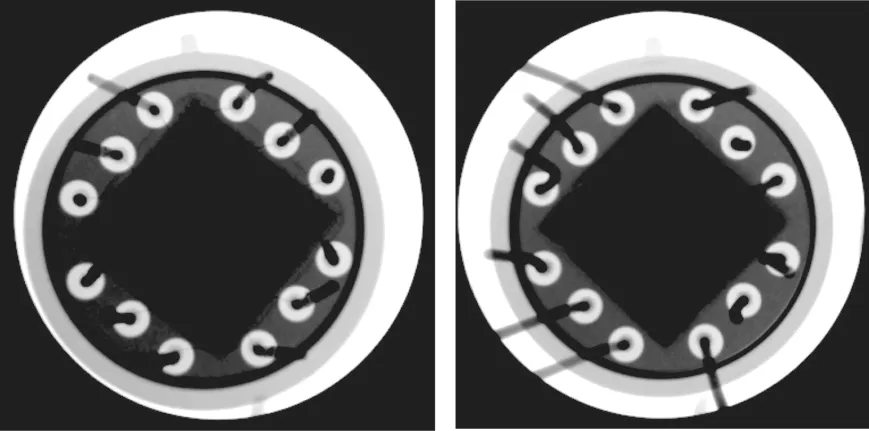

0041 型功率运算放大器采用厚膜混合制造工艺,基片上集成4 个厚膜电阻,通过金导带实现内部互联。厚膜基片采用Al2O3陶瓷,基片与管基采用真空合金焊烧结。内部5 个芯片(C8051 型、A8551 型晶体管各2 个,LM741运放1 个)。封装时采用导电胶粘接在金导带上,选用Φ25μm、Φ50μm 两种规格金丝进行热-超声键合,其中Φ25μm 键合丝7 根、Φ50μm 键合丝19 根,显微镜观测的产品内部结构如图1 所示。

图1 产品内部结构图

3 样品故障分析与定位

针对返厂故障样品和未装机样品分别进行外观检查、电参数测试、密封性检查、PIND 检测等测试,采用X 射线照射等手段定位失效产品内部故障。

■3.1 样品内部故障测试与分析

外观检查表明两样品引脚上锡完整,230#样品引线被剪短,未发现外部金属壳体开裂、变形、鼓起等异常,其玻璃绝缘子无开裂或缺损。依据Q/FA 20003B-2013 规范要求,采用STS8105A 型混合信号测试系统对样品进行了常温电参数测试,测试结果合格。

依据GJB548B 标准试验条件对样品A1、C1 进行密封性检查,样品密封性检测合格。按GJB548B 2020.1 要求进行PIND 检测,样品检测合格。经X 射线设备拍照,样品基片及芯片表面及粘结表面空洞较小,空洞率符合相关规定,键合丝无断裂、无塌丝,键合点无脱落情况,X 射线照射下两样品内部结构如图2 所示。

图2 X 射线下样品内部结构图

■3.2 故障定位

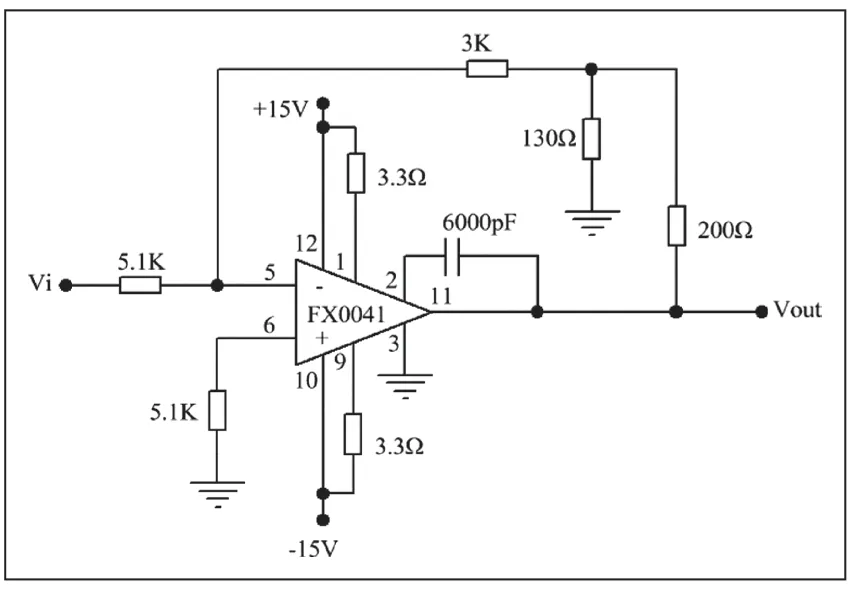

0041 产品最大输出电流200mA,测试线路中采用的限流保护电阻Rsc 为3.3Ω,模拟产品实际工况搭建的测试电路如图3 所示。VIP-P=20V、f=50Hz 正弦波信号下,对两样品进行测试并与合格产品对比分析可知,输出波形无异常、产品线性区放大工作正常。

图3 测试电路原理图

保护晶体管导通电压VBE为0.6~0.7 V,限流保护电阻Rsc=3.3Ω,输出短路电流180mA ≤Ios≤212mA。当限流保护电阻≤3.3Ω 时,产品输出短路电流Ios≥180mA,电路中保护管Q1、Q3 集电极串阻小于10Ω。产品工作时Q1、Q3 未能给输出管Q2、Q4 提供偏置,不出现正、负满偏。当产品输出短路电流小于180mA、集电极串阻大于10Ω 时,此时保护管Q1、Q3 处于工作状态,持续为输出管Q2、Q4提供偏置,使其工作在放大状态,输出电压随着输入信号变化。

综上,当保护管Q1、Q3 集电极串阻小于10Ω 时,不能为输出管Q2、Q4 提供偏置。若保护管Q1 集电极间串联电阻变大,使Q2 基极电压提高并持续给Q2 提供偏置,Q2仍处于放大状态,使产品输出处于负满偏,导致故障产生。

4 失效原因排查

构建的失效分析故障树如图4 所示。为确定引起芯片粘接失效的最终故障源头,对引起晶体管集电极串阻的银浆颗粒分布不均匀、粘接面污染和导电胶退化等因素进行排查。

图4 失效分析故障树示意图

0041 产品制造时采用导电胶将元器件粘接在厚膜基片上,高温固化后经导电胶实现芯片背面集电极和金导带连接。导电胶异常、回温异常、粘接固化异常导致导电胶颗粒分布不均匀或粘接提前固化,造成集电极串阻增大。经检测未见异常,可排除提前固化异常。

自动贴片可保证产品点胶量一致、平整度和导电胶分布均匀性,经复查所用导电胶入厂检验合格,该批导电胶也用于其他批次0041 产品,相关检测未见异常。根据GJB 548B-2005 混合电路目检和FA3.500.008 检验要求,对导电胶多少、芯片划伤、有无短路等进行检测,合格后再进入下道工序,经检测未发现异常,可排除导电胶异常。从低温储存室内取出导电胶,按称取规定剂量导电胶放入盛胶皿,取出后室温回温30~40 分钟,经同一方向搅拌均匀后放入点胶管。经复查未见异常,可排除粘接前导电胶准备过程异常。

固化工艺对导电胶性能有显著影响,固化不佳会导致胶点脱落或接触电阻增大。导电胶固化采用自动控制。检验完成后将合格产品放入烘箱,启动设定固化程序运行从常温升温至120℃±3℃恒温1 小时;再升温至170℃±3℃恒温2 小时,后自然降温至50℃以下取出产品。经复查,同批次产品未发现导电胶固化异常。

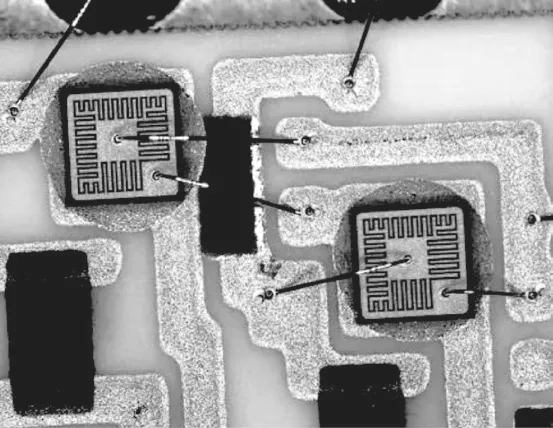

产品芯片通常减薄至200μm 后再进行背面金属化,金属化层一般为Ti-Ni-Ag 三层结构,导电层为芯片背面最外层,接触界面如图5 所示。若芯片背面金属化存在氧化、基片焊盘表面污染或氧化、导电胶粘接污染会即粘接面污染会导致粘接导通电阻增大,经测试可排除粘接面污染异常。芯片粘接后在导电胶与金导带间及背面金属化层与导电胶间存在两接触面,粘接后产生的接触电阻R=R金-胶+R胶-芯。固化后对接触电阻R金-胶进行测试,R胶-芯则通过测量晶体管导通饱和压降和输出电流进行计算。

图5 内部粘接示意图

排查芯片背面氧化,背面氧化或沾污会在粘接时形成原子团阻挡层,造成导电胶与芯片背面相互渗透变差,引起Ag 颗粒分布不均,形成粘接夹层,进而使得接触电阻增大,芯片粘接时集电极串阻增大。对230#样品进行开帽操作,用探针和YB4812 型特性图示仪对Q1、Q2 晶体管饱和压降进行测试,饱和压降分别为1.5V 和0.12V,接触电阻分别为0.42Ω 和0.41Ω。在使用线路中限流保护电阻Rsc 为100Ω,保护功能启动时输出电流6.5mA。产品投料前由检验人员对0041 使用的芯片和外壳100%镜检。经复查,同批次产品A8551 晶体管、C8051 晶体管入厂检验合格。

产品固定检验员分别长期从事芯片材料和外壳材料,经复查当天安排外壳材料生产任务较少且芯片检验任务较重,临时安排个别平时主要检验外壳的检验员参与产品芯片检验。检验过程中,检验员对芯片背面金属层氧化程度把控不好、不适应芯片检验,后期停止了其检验操作。不排除检验员因检验经验不足、对芯片背面金属层氧化程度把控不准等人为疏忽导致的背金氧化芯片未剔除的情形。芯片背面金属发生氧化或沾污,背面金属化层与导电胶之间接触电阻增大,导致集电极与金导带间串联电阻变大。为减小信号衰减,要求导体材料对氧化铝基片有良好附着力、细线分辨率及线焊特性。测得连接导电胶与金导带的接触电阻分别为0.42Ω和0.41Ω,可排除基片导带氧化异常。

通过上述排查与分析,可知造成该批次0041 产品输出电压负满偏的原因是部分芯片的背面金属化层存在氧化沾污,材料检验时因检验员经验不足、人为疏忽而未能有效剔除不合格产品。造成出厂产品芯片粘接后存在夹层,在环境作用下发生一系列理化反应,原子团阻挡层电阻增大,造成保护Q1 三极管芯片粘接时造成集电极串阻,进而使得Q1不能实现保护功能,输出管Q2 仍处于放大状态,使产品输出处于负满偏。

5 结束语

经前述故障定位与排查、分析,针对0041 产品检核过程存在的问题,拟采取改进措施如下:

(1)芯片装结前对其背面金属化进行氧化程度分析,若出现氧化,可在粘接前进行等离子清洗,可有效从源头解决该问题;

(2)进一步完善、细化测试规范,产品测试时增加输出短路电流Ios测试,当180mA ≤Ios≤210mA 时保证Q1、Q3 集电极串联电阻小于10Ω,可有效剔除不合格产品。

综上,造成0041 产品故障的原因是部分产品采用的C8051、A8551 芯片背面金属化层存在氧化沾污,进行芯片检验操作时存在检验员人为疏忽未进行有效剔除,造成芯片粘接后存在夹层,在电场、温湿度共同作用形成原子团阻挡层电阻变大,造成晶体管芯片粘接时造成集电极串阻偏大,失去了保护能力,造成输出管持续处于放大状态、导致产品输出异常。通过采取上述措施,可有效解决和防止类似问题再次发生。