微弱振动信号检测技术的研究

杨雪凯,胡 辉,顾俊杰,郝志阳,张 婷

(北华航天工业学院 电子与控制工程学院,河北 廊坊 065000)

随着现代信号处理技术和电子集成技术的发展,越来越多的人把想要分析的物理信号(比如振动信号、声音信号等)进行数字量化,然后将数字信号进行相应的计算,存储和传输至上位机进行计算分析。

通过文献[1]和文献[2]可知,传统的数据采集系统多采用单片机(例如STM32)或者DSP来作为数据采集的实时性、高采样率、宽动态范围的要求。DSP虽然能够满足微弱信号采集对主控单元的运行速度和实时性的要求。但是DSP的价格高昂,研发周期长,更适用于对采样率要求低的数据采集系统。从文献[3]、文献[4]和文献[6]中可得到,FPGA具有时钟频率高、内部时延小、运行速度快、集成度高、执行效率高、功耗低、能完成复杂的时序逻辑设计、编程灵活方便等特点,非常适用于高采样速率、大数据量、处理任务固定且重复的多通道微弱信号采集系统。从文献[5]和文献[2]可知,USB接口具有传输速率快、接口控制灵活、功耗低、使用方便、易扩展等优点,是数据采集系统的理想接口。

1 噪声分析

噪声是电子系统中不需要的信号。噪声会对降低我们采集信号的质量以及增大采集误差。噪声包括固有噪声和外部噪声,这两类噪声均会影响电子电路的性能。外部噪声来自外部噪声源,例如数字交换、60Hz噪声以及电源交换等。固有噪声由电路元件本身产生,最常见的例子包括宽带噪声、热噪声以及闪烁噪声。我们可以通过计算来预测电路的固有噪声。

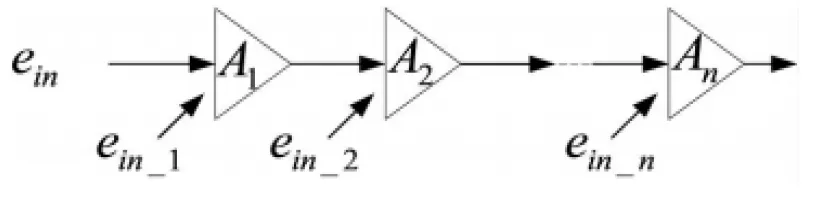

本系统前级可以认为是包括程控运放电路、衰减电路、滤波电路的多级放大电路。我们对多级放大电路的噪声建模便得到如图1所示的噪声模型。

图1 系统噪声模型

在多级放大电路中我们可以将噪声分为电压噪声和电阻热噪声。我们可以根据产品说明书中的频谱密度曲线来确定上述噪声源的大小。其中电阻热噪声的计算公式是:

(1)

k为玻尔兹曼常数,T为开氏温度,Req为等效电阻,Δf为信号带宽。

电压噪声又分为1/f区噪声和宽带区噪声。

1/f区噪声公式:

(2)

(3)

efnorm为1Hz的归一化噪声。

eat_f为f时电压噪声密度。

f为已知噪声电压密度的1/f区域的频率。

fH为操作高频(使用噪声带宽BW)。

fL为操作低频(一般为0.1Hz)。

宽带区噪声公式:

(4)

enBB为宽带电压噪声。

eBB为宽带电压噪声密度。

Kn为滤波器阶数对应的换算系数。

总电压噪声:

(5)

根据两个不同电阻器或者不同运算放大器的噪声彼此不相关,两个随机不相关的噪声信号相加得到总噪声为:

(6)

我们可以得到多级放大电路的总的输入噪声为:

(7)

2 系统硬件组成

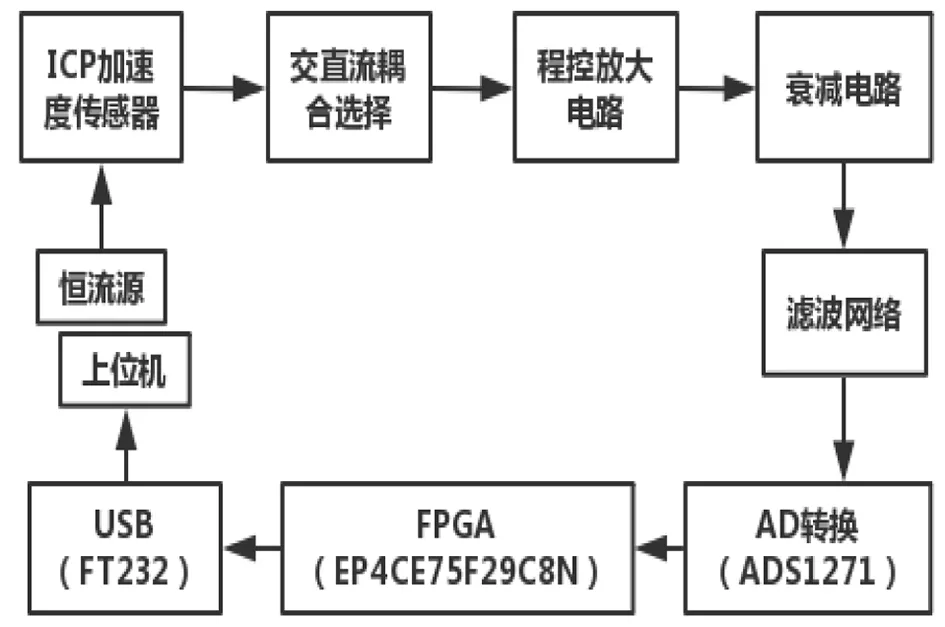

系统结构框图如图2所示。

图2 系统硬件

ICP加速度传感器采用恒流源供电,内置压电传感器,用集成电路技术将电荷放大器置于传感器中,并以低阻抗电压方式输出,输出的幅值与加速度成正比。

模数转换模块选用ADS1271,其采样率最高达105KSPS,采样精度为24位。数据传输选用单通道USB2.0转FIFO的芯片FT232,数据传输速率最快为40MB/s。

3 系统软件实现

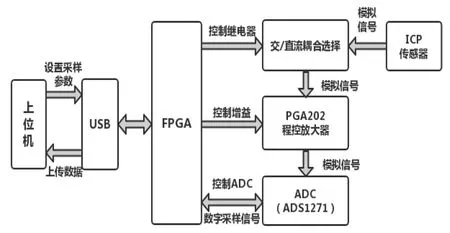

系统软件运行如图3所示。系统上电后,用户通过上位机设置系统的采样参数,例如系统放大倍数、系统采样率、交直流耦合方式和触发方式。上位机设置的采样参数通过USB2.0芯片传输到FPGA中进行解码。FPGA按照用户设置来控制继电器,程控增益放大器,数模转换器,USB2.0通信模块。12路采集到的模拟信号经过12片ADS1271数模转换器后成为数字信号,再通过FIFO数据缓冲模块,经USB2.0后将采集到的数据上传至上位机进行处理和显示。

图3 系统软件

3.1 ADS1271控制模块设计

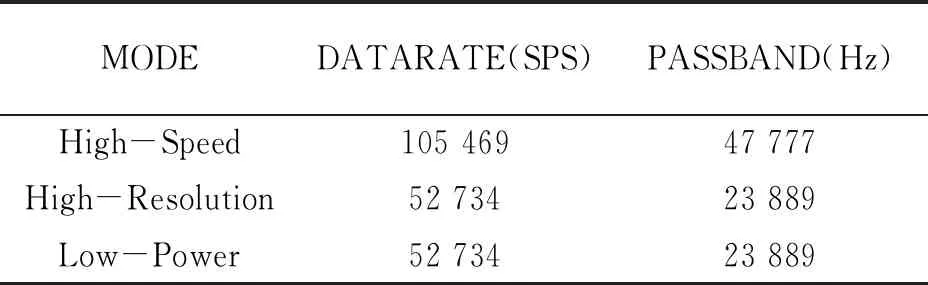

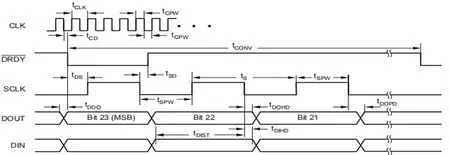

本系统采用TI公司的ADS1271数模转换芯片。ADS1271提供了SPI和帧同步两种通信方式以及高速模式、高精度模式、低功耗三种工作模式。我们在本系统中应用的是SPI通信模式和高速工作模式。不同工作模式下有着不同的输出采样率,如表1所示。

表1 ADS1271操作模式性能表

图4 ADS1271在SPI通信模式下的时序逻辑

3.2 USB通信模块

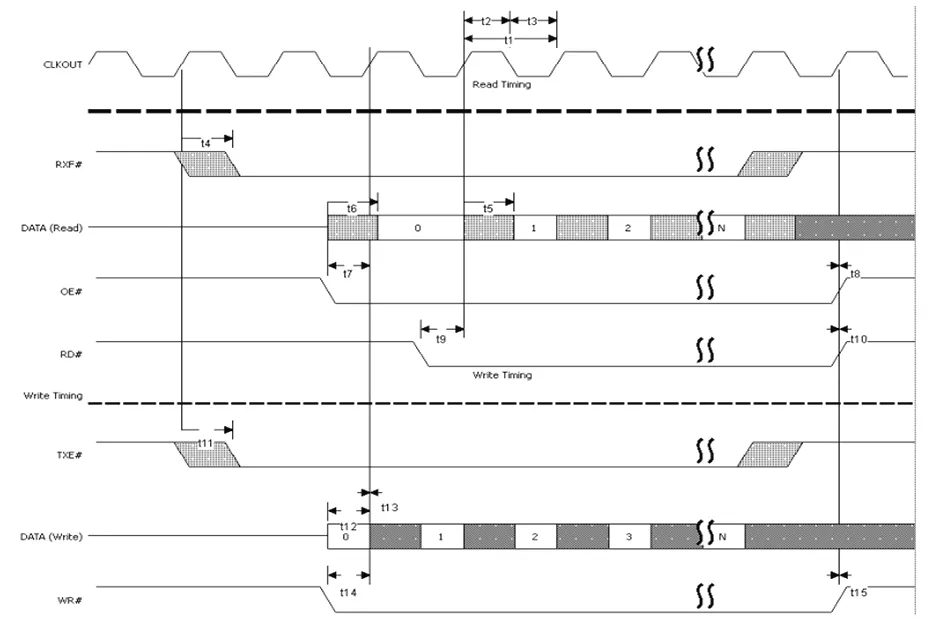

FPGA通过同步FIFO实现与FT232的通信数据传输。RXE#、TXE#是FT232的读写标志信号;OE#为使能控制信号;RD#、WR#是FT232的读写信号;SIWU#是FPGA命令FT232唤醒PC机或向上位机发送数据的控制端口;ADBUS[7:0]是双向数据传输端口。CLKOUT是FT232的60MHz的时钟驱动引脚,所有信号应该和该时钟保持同步;FPGA通过Verilog编程实现对FT232的控制,进而实现与上位机软件的双向数据通信。图5为同步FIFO的读写控制时序图。

图5 同步FIFO的读写控制时序

3.2.1 FPGA读上位机数据控制进程(见图6)

图6 同步FIFO读标准连接

IDLE读取命令发生,进入状态1。

状态1:检测RXF#引脚状态,如果RXF#为低电平时,则拉低OE#,进入状态2。

状态2:检测RXF#引脚状态,如果RXF#为低电平时,则拉低RD#引脚,读取上位机下发命令,进入状态3。

状态3:读取上位机命令,根据不同的命令(传感器类型选择、增益倍数选择、采样率选择,触发方式选择、触发电平设置)分别进入状态4、状态5、状态6、状态7。

状态4:根据上位机下发指令,进行传感器类型配置。继续读取则返回状态2,否则进入IDLE。

状态5:根据上位机下发指令,进行增益倍数配置。继续读取则返回状态2,否则进入IDLE。

状态6:根据上位机下发指令,进行触发方式配置。继续读取则返回状态2,否则进入IDLE。

状态7:根据上位机下发指令,进行触发电平配置。继续读取则返回状态2,否则进入IDLE。

3.2.2 FPGA向上位机写数据控制进程(见图7)

图7 同步FIFO写标准连接

IDLE:读事件发生,进入状态1。

状态1:接收上位机复位信号,进入状态2。

状态2:检测FIFO中是否有数据,当有数据时进入状态3。

状态3:检测FIFO半满或全满。当FIFO全满时进入状态4。

状态4:驱动数据到数据线上,如需继续传输数据进入状态2,否则进入状态IDLE。

4 实验结果

本数据采集系统应用LabVIEW来搭建上位机软件通过上位机实现对采集系统的增益控制、交/直流耦合选择、采样率设置、触发方式选择、触发电平选择等设置以及FPGA采集数据的显示、处理和储存。

利用RIGOL的DG1022函数信号发生器产生频率为1kHz,峰峰值是5mVpp的正弦信号,通过上位机来设置采样率为10kHz,增益为1 000倍,直流耦合方式,并显示实时采样波形图,如图8所示。

图8 实时采样波形

从图8的实时采集波形图和表2中数据可看到,系统采样结果与输入信号具有较好的一致性,在输入信号为5mVpp,频率为1kHz,1 000倍增益的情况下,误差仅为0.17mV左右。在输入短路的情况下,我们从表中数据可以知道本系统的短路底噪为0.4mVpp左右,具有比较好的一致性,可以满足实际使用需要。该方案搭建的采集系统具有成本低、底噪低、功耗低的特点,同时也具有高速、实时、高可靠性等优点。

表2 实时采集数据