一种高性能跨阻式测量放大器的设计*

马玉清,李如平,吴房胜

(安徽工商职业学院信息工程学院,安徽 合肥 231131)

引言

运算浮地电流传输器(Operational Floating Current Conveyor,OFCC)[1,2]是一种功能强大的有源构建模块,它为电路设计人员提供了充分的灵活性.它继承了电流传输器和电流反馈运算放大器的特点,增加了电流输出端、输入端的高阻抗、输出端的低阻抗可用性也为电路设计提供了更好的性能;近年来,OFCC已经用于实现测量放大器、读出电路、对数放大器、整流器、滤波器、可变增益放大器和惠斯通电桥的设计[3-13].

测量放大器(Instrumentation Amplifier,IA)也称为仪表放大器或数据放大器,它是一种可以用来放大微弱差值信号的高精度放大器.测量放大器在应用中通常作为一个输入模块,如汽车传感器[14]、工业过程控制[15-17]、线性位置感知[18]和生物电位采集系统[19-24]来放大差分信号,并抑制不需要的共模信号.一般而言,基于运算放大器的IA分为电压模式IA(Voltage Mode IA,VMIA)和基于电流模式构建模块的IA,称为电流模式IA(Current Mode IA ,CMIA);另一种分类方法是基于IA工作的输入和输出信号类型.跨阻IA(Transimpedance IA,TIA)就是这种分类中的一种,它把检测到的电流放大并转换为电压.尽管有文献针对TIA进行研究,但很少有文献针对采用OFCC实现的TIA可用.表1比较了常见的3种TIA[25-27]设计,它们是根据采用的有源和无源元件的数目和类型以及输入和输出端的阻抗进行分类的.从表1可以看出:

表1 三种常见TIA设计的特性

1)基于运算放大器拓扑结构设计的TIA[26]采用的电阻数量太多;

2)基于运算跨阻放大器(Operational Transimpedance Amplifier,OTRA)设计的TIA[27]有低的输入阻抗,这对于电流传感是理想的选择,而基于CCⅡ型结构设计的TIA[25]和基于运算放大器拓扑结构设计的TIA[26]的输入阻抗较高,显然不适于电流传感;

3)基于运算放大器拓扑结构设计的TIA[26]和基于OTRA设计的TIA[27]的输出阻抗提供了合适的输出阻抗,低于基于CCⅡ型结构设计的TIA[25];

4)对于基于运算放大器拓扑结构设计的TIA[26]的输入端和基于CCⅡ型结构设计的TIA[25]的输入端和输出端的阻抗匹配,需要额外的有源元件,从而增加了电路的设计成本和非理想特性.

显然,只有文献[27]的结构提供了合适的输入和输出阻抗电平,而且不需要额外的阻抗匹配电路.因此,本文提出了一种高性能的TIA设计,电路结构基于OFCC ,以提供合适的输入/输出接口.它仅使用3个有源模块和4个电阻,即与文献[27]有相同数量的有源模块,但比文献[27]有更少的无源元件,而且本文提出的电路结构有更低的输入和输出阻抗;仿真实验结果表明,本文提出的TIA设计不但能够提供一个稳定的电压输出和较小的输出噪声电平,以及具有与频率无关的差分增益,而且在更宽的带宽上能够有独立于TIA有限开环增益的共模抑制比.

1 TIA电路结构设计

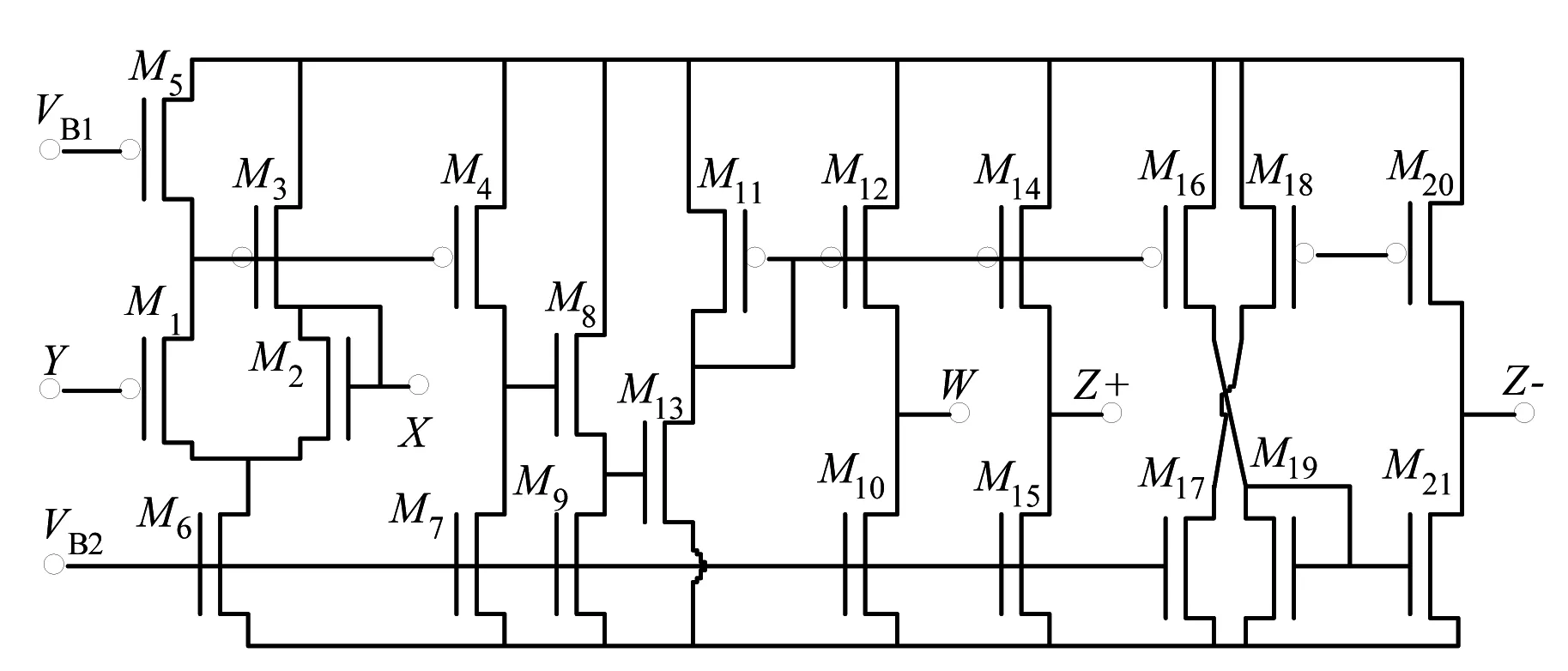

本文提出的TIA电路结构的主要部件是OFCC有源模块,如图1所示.它有2个输入端(X,Y)和3个输出端(W,Z+,Z-).

图1 OFCC有源模块

端口X是一个低阻抗电流输入端,端口Y是一个高阻抗电压输入端.端口Z+和Z-都是高阻抗电流输出,其中Z+具有正极性,Z-具有负极性.端口W为低阻抗输出电压端.OFCC的端口特性由式(1)的矩阵来描述:

(1)

式(1)中开环跨阻增益ZT是端口X和W之间的阻抗.

图2所示为本文提出的采用OFCC设计实现的TIA电路.它由3个OFCC(OFCC1, OFCC2和OFCC3)和4个电阻构成,其中的OFCC采用CMOS实现的电路结构如图3所示.

图2 本文提出的采用OFCC设计实现的TIA

图3 OFCC的CMOS实现的电原理图

图2中的第3个OFCC模块仅用作为一个电流-电压变换器,它将接收到的放大后的电流差(作为OFCC1和OFCC2的输入)变换为电压.在理想情况下,测量放大器的差分跨阻增益计算如下.

流出OFCC1和OFCC2的W端子的电流(iW1,iW2)分别为:

(2)

(3)

输出电压为:

vout=-R2(-iW1+iW2)

(4)

采用式(4),得到差分增益AD为:

(5)

式(2)~(5)中的iin1和iin2分别为OFCC1和OFCC2的X端口的输入电流,iW1和iW2分别为OFCC1和OFCC2的W端口的输出电流,vout为OFCC3的W端口的输出电压,R1、R2和RG为外接电阻.显然,从式(5)中可见,差分增益与频率无关.

2 非理想特性分析

实际上,有两种类型的OFCC非理想特性.第一种非理想特性来自于端口电压和电流之间的跟踪误差,其影响严重依赖于电路的拓扑结构.由于本文提出的拓扑结构中的Y端子接地,故性能不受电压跟踪误差的影响.仅需考虑电流跟踪误差,在Z+和Z-端子上的电流为:

iZ+=αiW2

(6)

iZ-=-γiW1

(7)

式中α和γ为非理想特性常数.

因此,式(4)需修改为:

(8)

假设式(8)中的α=γ=1,则差分增益AD可写为:

(9)

对于共模运算来说,考虑式(8)中的iin1=iin2=iCM,则可得到共模增益ACM为:

(10)

因此,最后电路的共模抑制比CMRR为:

(11)

第二种非理想特性是由于有限的跨阻增益ZT以及它的频率依赖特性,在较高频率时近似为ZT=1/(sCP).CP=ZOTωCF,这里ZOT和ωCF分别为开环跨阻增益和它的截止频率.

考虑到有限的ZT,式(4)重新计算为:

vout=[ε1(s)iW1-ε2(s)iW2]ε3(s)R2

(12)

即:

(13)

式中:

假设ε1(s)=ε2(s),则差分增益计算为:

(14)

考虑iin1=iin2=iCM,则共模增益为:

(15)

因此,共模抑制比CMRR为:

(16)

3 仿真结果

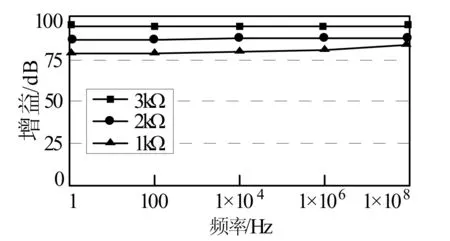

为了验证本文提出的TIA设计的功能,实现OFCC电路所采用的各组晶体管的宽长比如表2所示.我们采用SPICE执行仿真,电源电压采用±1.5 V,偏置电压为±0.8V.对本文提出的TIA仿真设计得到的差分增益的频率响应如图4所示,仿真时取RG=1 kΩ,R1=5 kΩ,R2从1 kΩ变化到3 kΩ,以1 kΩ步长增加来得到不同的增益.从图4可见,本文提出的TIA设计的差分增益与频率无关,具有很好的频响特性;对本文提出的TIA设计仿真得到的共模抑制比的频率响应如图5所示.从图5可见,共模抑制比与增益无关,是独立于增益的,而且有一个高达112 kHz的带宽;图6所示为对本文提出的TIA设计对应于不同增益(即对应于不同的R2取值)时仿真得到的噪声频谱分析,即R2上的噪声电平频谱(采用与获得差分增益响应相同的元件值).从图6可见,输出噪声电平即使在高增益时(即R2=3 kΩ也具有较小的输出噪声电平,最大不超过10 pV,而且在整个频率范围内有着几乎不变的噪声特性,这对于TIA获得稳定的电压输出和功耗来说是至关重要的.

表2 实现OFCC电路的CMOS管特性

图4 TIA的差分增益频率响应

图5 不同增益值的TIA的共模抑制比频率响应

图6 不同增益值的TIA的噪声谱密度

4 结论

本文提出了一种采用OFCC设计的高性能TIA.电路仅需要3个OFCC,3个反馈电阻和1个接地电阻.为了得到放大输出,电路工作在电流输入模式,而无需采用复杂的输入信号.交流分析表明,电路具有较高的增益效率和较大的带宽;所提出的TIA设计不仅提供了在基于现有的运算放大器设计的TIA上的优势,而且在更宽的带宽上能够有独立于TIA有限的开环增益的共模抑制比;所提出的TIA设计相比于现有的基于运算跨阻放大器的设计,还减少了元件数量.