基于FPGA的存储内建自测试的研究

薛 凯,侯荣彬,李 勇

(中国核动力研究设计院 核反应堆系统设计技术重点实验室,成都 610213)

0 引言

在现代数字控制系统中,储存器是现代数字系统的重要组成部分之一。随着半导体工艺技术的发展,以及各领域对储存器件速度、容量的要求日益提高,在使系统性能变得更强的同时,系统也变得越来越复杂,对电路的故障诊断也提出了更高的要求。由于储存器件硬件电路结构的复杂性,为了保证系统能够稳定地运行,有必要对储存器件进行有效的测试,及时发现错误,确保系统正确稳定地运行。

1 储存器类型

储存器的类型多种多样,有易失性(如SRAM、SDRAM、DDR等)、非易失性(如FLASH、EEPROM等)、静态性(如SRAM等)和动态性(SDRAM、DDR等)。它们都有自己的特点和结构,也有着与逻辑测试不同的测试和故障诊断的方法。尽管不同器件在储存容量和硬件结构上有所不同,但它们在地址的硬件结构上非常相似[1],所以它们的测试方法也基本类似。

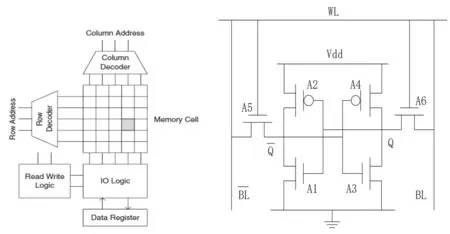

SRAM有高速和不用刷新等优点,故本文以SRAM(静态随机储存器)[1]作为讨论和研究类型。图1显示了一个内存数组的基本结构,内存的硬件包括单元数组、解码行和列地址的解码器、读和写逻辑,以及用于处理内存数组之间的输入输出的逻辑块。SRAM中的每一位都储存在由4个场效应管(A1、A2、A3、A4)构成的两个交叉耦合的反相器中,另外两个场效应管(A5、A6)是储存基本单元,用于对读写位线(Bit Line)的控制开关。访问SRAM的时候,字线(Word Line)拉高,使控制每个基本单元的两个晶体管A5和A6导通,把基本单元与位线(Bit Line)连通。

图1 储存器基本结构图Fig.1 Basic structure of memory

2 SRAM的测试方法

1)自动化测试

自动化测试是利用自动化测试设备(Auto Test Equipment,ATE)对SARM的储存阵列进行访问,通过封装引脚直接对储存器进行读写测试,经过多种测试算法进行故障诊断[2]。其缺点是:随着自动化测试设备上算法复杂度的提升,对设备上储存器容量的要求也越高[3],自动化测试设备对嵌入式储存器进行测试也相对较难。

2)微处理器测试

通过嵌入式微处理器对储存器进行写读测试,测试向量由微处理器内执行测试的程序生成[4],在需要对储存器进行测试的时候,直接调用这部分代码进行测试诊断。其优点是:不需要硬件上的改动,而且测试算法可在微处理器上灵活修改与实现。

3)储存器内建自测试(MBIST)

储存器内建自测试技术(Memory Build - In Self Test,MBIST)的工作原理是在储存器外围产生测试控制电路,包括数据生成、地址控制、读写控制以及测试结果比较等电路[5],实现储存器测试向量的自动产生,以及测试结果的自动判断。正常工作的时候旁路该部分控制电路需要进行测试的时候,可通过外部通信接口发送指令,自动进入储存器测试模式[5]。

3 SRAM的故障类型

SRAM的故障类型主要有以下几种:

1)固定故障(Stuck-At Faults,SAF)

固定故障是指一个储存单元的值总是0或1,并且不能改变。

2)跳变故障(Transition Faults,TF)

储存阵列中的一个储存单元或多个储存单元中的一位或多位不能从0到1进行跳变,或不能进行从1到0的跳变。存储器单元能进行1到0的跳变,不能进行0到1的跳变,称为向上跳变故障;存储器单元能进行0到1的跳变,不能进行1到0的跳变,称为向下跳变故障。

3)耦合故障(Coupling Faults,CF)

存储单元中一些位在跳变的时候,导致相邻其他位的值也发生变化。这种现象既存在于不同储存单元之间,也存在于在同一储存单元的不同位之间。同一单元中,字与字之间相互影响产生的故障称为字间故障,同一字节内比特位之间相互影响产生的故障称为字内故障。耦合故障中,包含翻转耦合故障(CFin:inversion)、幂等耦合故障(CFid:idempotent)、状态耦合故障(CFst:state)[6]。当某个储存单元的值的跳变使其他某个储存单元的值发生翻转的现象,称为翻转耦合故障(如储存单元M的状态由1跳变为0时,储存单元N的状态发生翻转);当某个储存单元的值的跳变使其他某个储存单元的值变为一个固定的值的现象,称为幂等耦合故障(如当储存单元M的状态从0跳变为1或从1跳变为0,此时储存单元N的状态会变为某个特定的值);某个储存单元的某个确定的状态,使其他储存单元发生跳变为某一状态的现象,称为状态耦合(如当储存单元M状态为1时,储存单元N跳变为一个随机值)。

4)地址译码故障(Address Decoder Faults,ADF)

地址译码故障,其实就是地址译码器发生的故障,主要有以下4种类型:

◇ 对于给定的地址,不存在相对应的储存单元。

◇ 对于一个储存单元,没有相对应的物理地址。

◇ 多个单元被一个地址访问。

◇ 多个地址访问一个单元。

5)桥连故障(Bridging Faults,BF)

指由两个或多个位线(BL)一起短路引起的。短路的结果表现为两个单元格的and或or逻辑,所产生的短路只影响其中一个单元,另一个单元的值不变[7]。

4 SRAM的测试方法

4.1 SRAM的测试原理

SRAM的测试原理非常简单,通过内建自测试的方法,由电路自己生成针对每一种故障类型的测试向量,通过程序控制逻辑对每一个储存单元进行反复读写,依靠自身逻辑来判断所得到的测试结果是否正确,从而确定储存器中是否存在故障[8]。

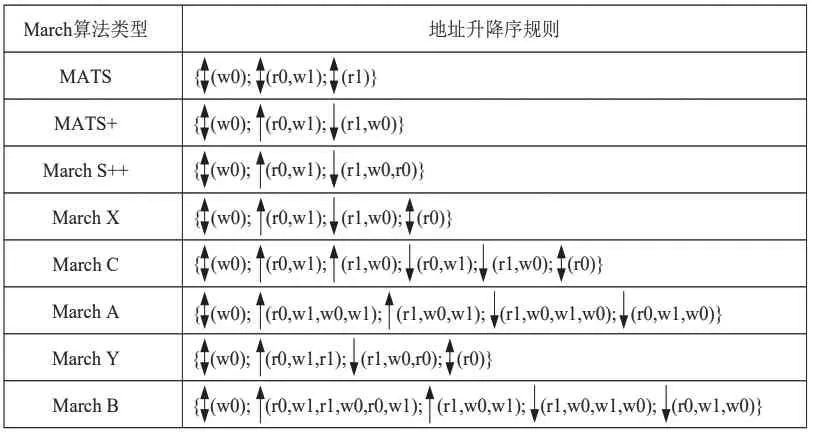

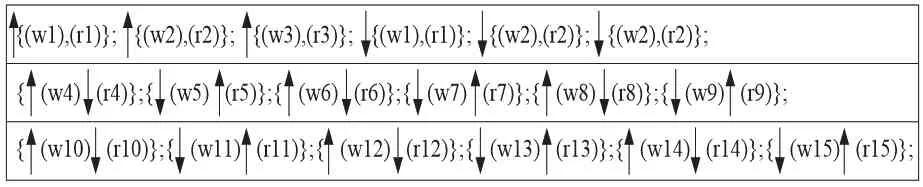

表1 March算法表Table 1 March algorithm table

4.2 常见的测试算法

由于March算法不仅实现方式简单,而且测试方便,使其在储存器测试方面得到广泛应用。March算法也有很多不同的类型,主要有MATS、MATS+、MATS++、March X、March C、March A、March Y、March B[9]等类型,各种March算法的不同在于测试向量的不同(这里的测试向量又称为March元素)。不同March算法的每个March元素对于地址的升降顺序都有规定,具体每个March算法的读写规则见表1。

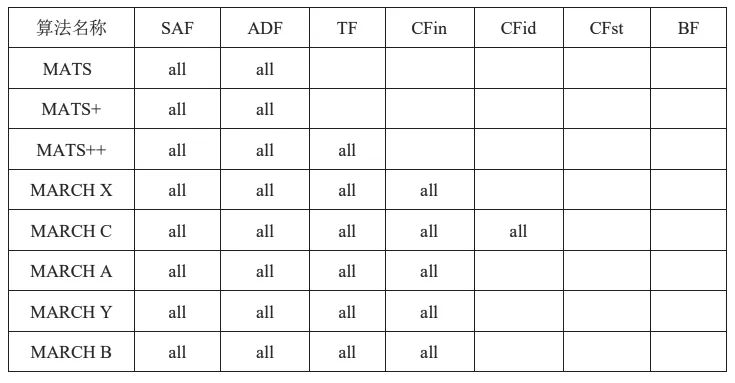

4.3 不同March算法的故障覆盖率

4.4 优化的March算法

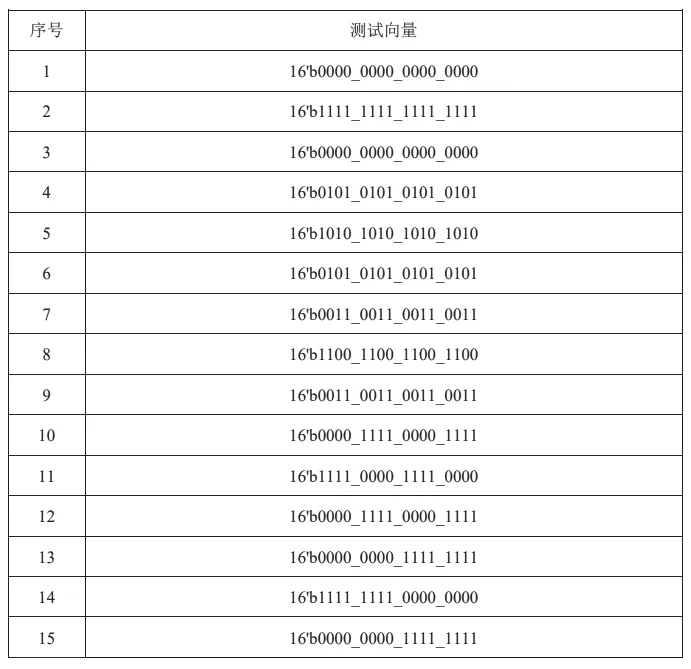

通过表2可以看出,各种March算法都不能把故障进行全面覆盖,比如耦合故障中的状态耦合故障和桥连故障,它们的发生与周围某一个储存单元的状态有关。本文提出一种可以覆盖全部故障的测试方法,通过增加测试向量的复杂度,使测试向量中相邻两比特位出现00、01、10、11这4种值来检测这类故障。以16位位宽的SRAM为例,测试向量见表3。

对以上测试向量进行读写,w(n)表示向储存中写入第n个测试向量;r(n)表示从储存中读取的第n个测试向量。具体操作规则见表4。

5 系统设计及验证

由于FPGA内块RAM与SRAM的控制接口类似,所以本文以FPGA内部16位块RAM代替SRAM,每次操作128个地址长度,通过故障注入的方式进行仿真验证。

表2 各March算法故障覆盖率Table 2 Fault coverage of each March algorithm

表3 测试向量表Table 3 Test vector table

表4 测试向量操作规则表Table 4 Test vector operation rules

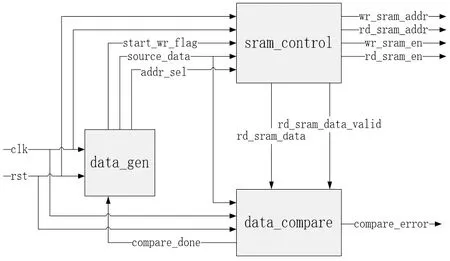

图3 数据产生模块仿真波形图Fig.3 Simulation waveform of data generation module

图4 SRAM读写模块仿真波形图Fig.4 Simulation waveform of SRAM read / write module

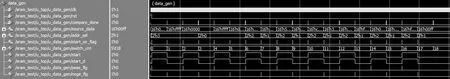

图2 软件设计框图Fig.2 Software design block diagram

5.1 软件设计

软件模块主要由3个模块组成。

1)测试向量产生模块:用于产生所需的测试向量。

2)SRAM读写模块:用于控制SRAM的读写。

3)数据对比模块:将写入的测试向量与从SRAM读出的数据进行比对,当比对错误时报出故障。

5.2 软件设计流程及框图

如图2所示,首先data_gen模块产生开始写SRAM的标志(start_wr_flag)以及测试向量(source_data),还有用于对读写地址升降顺序的控制信号(addr_sel),当addr_sel为2'b00的时候表示写地址和读地址都为降序;为2'b01的时候表示写地址为降序,读地址为升序;为2'b10的时候表示写地址为升序,读地址为降序;2'b11的时候表示写地址和读地址都为升序。sram_control模块根据指令进行写读操作,把从读出来的数据送入data_compare模块与source_data信号进行比对,当比对正确时data_compare模块发出compare_done信号,当比对有错误时发出compare_error信号。

5.3 仿真验证

1)数据产生模块

产生测试向量source_data,地址读写升降顺序控制信号addr_sel,开始写SRAM信号start_wr_flag,每当compare_done信号为1(即全部比对正确)时,开始发送下一组测试向量,一共18个测试向量,若任意一组向量测试比对出错停止发送。

2)SRAM读写模块

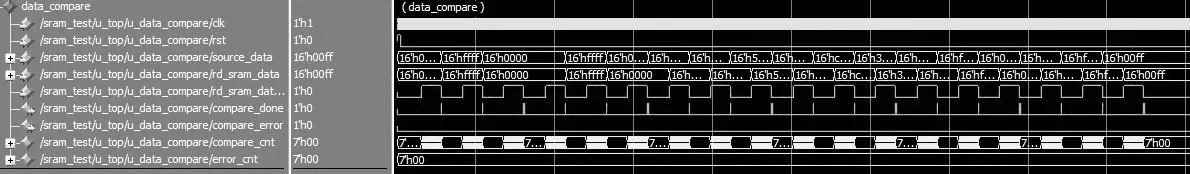

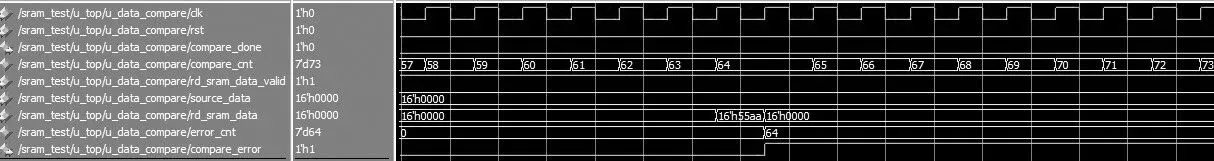

图5 数据比对模块仿真波形图Fig.5 Simulation waveform of data comparison module

图6 插入故障的仿真波形图Fig.6 Simulation waveform of insertion fault

根据data_gen模块发出的数据及控制信号对SRAM进行读写。

3)数据比对模块

将SRAM读出的数据与data_gen模块发出的写入数据进行比对,比对成功拉高compare_done信号,比对出错拉高compare_error信号。

4)插入故障的数据比对模块

当插入故障时,可见图6中的compare_error信号拉高。

6 结论

本文以SRAM为例,介绍了SRAM中几种故障类型,以及针对不同故障的测试方法。在现有算法的基础上,通过增加测试向量的复杂度,对原有算法进行优化,拥有了较高的故障覆盖率,并通过搭建储存器内建自测试模型对SRAM进行测试验证。储存器内建自测试的优点在于不需要使用专用的测试仪器,通过代码编写测试逻辑产生激励信号以及对测试结果的特征分析来找出故障,实现自我诊断,使芯片在完成原有逻辑功能的前提下,还能根据外部测试命令进入自我测试并输出结果,不仅能降低对测试设备的要求,还能及时发现故障,实现方式也相对简单。缺点是:由于储存器内建自测试技术需要占用额外的芯片资源,可能会对原有逻辑电路的时序特性产生影响[10]。