UHD 视频流无线传输方法研究

张 宽,张 铭,张志刚,刘 娟,唐立军

(1.长沙理工大学 物理与电子科学学院,湖南 长沙 410114;2.近地空间电磁环境监测与建模湖南省普通高校重点实验室,湖南 长沙 410114)

0 引言

超高清视频无线传输现在主要有三种方案:第一种是利用公共通信系统进行信号传输[1⁃2];第二种是利用WiFi 进行短距离、低延迟的视频传输[3];第三种是利用微波无线电技术[4⁃5]。在抗震救灾或者战场侦察等特殊场所,需要视频远距离无线传输,但又没有公共通信系统可以利用。所以微波无线电技术就变成了视频远距离无线传输唯一可用的方案,但微波无线电技术存在着传输带宽过窄的问题,导致传输的视频流分辨率低或者帧数低的问题。针对存在的这一问题提出了两种方案:第一种是增加微波传输带宽,第二种是通过对视频编解码来减少视频的传输带宽。目前,4K 视频传输带宽至少需要12 GB,增加微波传输带宽来实现4K 的传输显然是无法完成的,现阶段的方法是通过对视频流进行编解码压缩来降低传输带宽,实现4K@30 Hz 视频的无线传输。这种做法虽然实现了4K 视频的传输[5],但帧率只有30 f/s。本文通过异构多核FPGA 和AD9361 搭建了UHD 无线传输系统,利用HEVC 和OFDM 技术实现了4K@60 Hz 视频的远距离无线传输,具有视频分辨率高、帧率高、集成化度高的特点。

1 UHD 视频流处理方案

由于流畅无损传输4K@60 Hz 视频至少需要12 GB带宽,而OFDM 射频的传输带宽仅10 MB,所以4K@60 Hz 的视频流传输的关键是要对视频流进行编解码压缩来降低传输带宽,把原本需要12 GB 带宽传输的UHD 视频压缩至仅需要10 MB 带宽传输。HEVC 编解码技术对视频流压缩的压缩比[6⁃10]最大可达1∶500,因此,本文选取HEVC 编解码方案对视频流进行压缩。

目前视频流的HEVC 编解码主要有以下三种方法,一种是利用PC 机实现4K@60 Hz 视频流的HEVC 编解码,但由于受到体积过大的限制,难以实现集成和小型化;一种是ARM 芯片进行HEVC 编解码,但由于ARM运算速度慢会导致编解码产生巨大的延迟;还有一种是利用专业的HEVC 编解码芯片,但开发周期非常长[8]。鉴于此,本文提出异构多核的视频流的编解码方法,采用ARM+FPGA 架构,利用FPGA 硬件加速的优势搭建IP核,利用ARM 多任务处理的性能实现对FPGA 模块进行控制,结构灵活,开发周期短,为实现高效灵活的4K@60 Hz 视频流传输提供一定的技术支撑。

1.1 HEVC 编解码方案

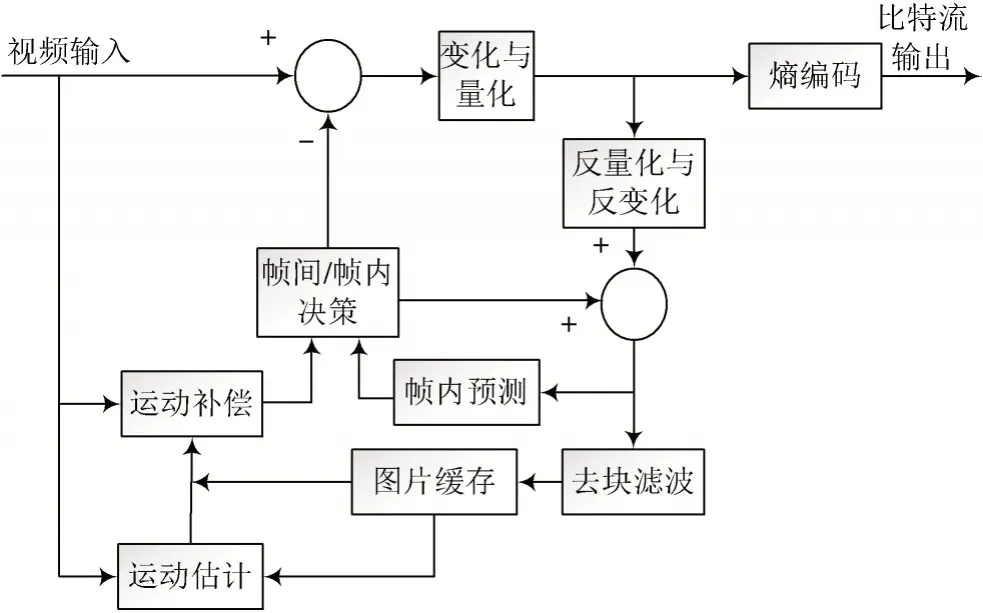

本文利用异构多核结构的编解码器VCU 来实现。VCU 编解码器最大可支持4K@60 Hz 的视频流数据,其编码架构如图1 所示,相应环节的方法说明如下:

图1 视频流编码架构

1)帧内编码方法。当图片缓存完毕后,首先对图片进行块状区域分割,并实现对其数据进行帧内估算,完成帧内编码。随后进行帧内预测,利用分块后的原图像帧和帧内预测相减,得到帧内残差信号。残差信号经过线性变化,可得到相应的变化系数,再把变化系数进行缩放和量化得到残差信号系数,经过反处理还原残差信号。把残差信号和帧内预测信号进行相加得到分块预测图像帧。利用环路滤波和自适应补偿除去“分块效应”,得到未经分块的图像帧。最终把帧内编码信号和残差信号系数一起进行熵编码,随后进行输出。

2)帧间编码方法。把分块图像帧数据输送到运动估计模块,通过利用帧内编码所预测得到的上一帧或下一帧图像数据进行帧间编码。通过运动补偿实现对帧间编码数据的补偿。同帧内编码一样,把分块原图像帧和去帧间预测结果进行做差,得到残差信号。利用残差信号和帧间预测信号相加得到分块预测图像帧。把得到的分块预测图像帧利用环路滤波和自适应补偿去除“分块效应”进行滤波,可得到分块的图像帧。最后将帧间编码信号和残差信号系数一起进行熵编码,将得到的结果输出。

解码器结构相对简单,视频流解码架构如图2 所示。解码器只需把接收到的比特流信号进行熵解码得到帧内/帧间编码信号和残差信号系数。首先,把帧内编码信号和残差信号相加,经过去块滤波得到第一帧图像。然后,把帧间编码信号和残差信号相加,再与前一帧图像进行运动补偿得到当前帧图像数据,最后经过去块滤波得到当前帧图像。

图2 视频流解码架构

1.2 视频流格式转换方案

HEVC 编解码方案的输入端是受到限制的,输入信号必须为YUV 格式的视频流,但视频流大部分的格式为RGB 格式,所以需要对视频流进行格式转换。因此,通过设计IP 核,将RGB 格式视频流转换为YUV 格式的视频流,识别视频流格式,直接将YUV 格式的视频流传输给VCU 进行HEVC 编解码。下面介绍视频流格式转换原理与方案。

在进行HEVC 编解码之前先要对视频流进行格式转换。视频输入端输入的为HDMI 差分信号,无论是ARM 还是FPGA 都无法直接对视频信号进行处理。因而首先,要把差分信号转换为并行信号通过VDMA 存入到内存中,再将非YUV 格式的视频流进行格式转换,使其满足VCU 的要求。

在HMDI 接收端设计视频格式转换器(IP 核),实现对视频信号判断和转换,把RGB 格式和YUV 格式的信号转换为YUV 4∶2∶2 的格式,还原原画质,大大压缩数据量,最大可压缩到原数据量的。为了减少运算量,降低编解码延迟,把RGB 数据转换为YVU 4∶4∶4 格式,再转换为YUV 4∶2∶2 和YUV 4∶2∶0 格式。设Y(x,y),U(x,y),V(x,y)分别为x行y列像素点的Y,U,V的值,RGB 格式转换为YVU 4∶4∶4 格式公式如下:

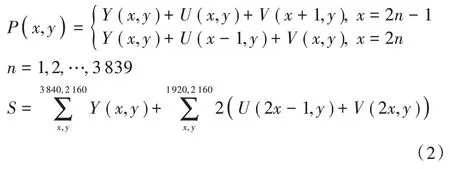

设P(x,y)为一个像素所含有的颜色信息,S为一帧图像包含的YUV 值。当采取YUV 4∶2∶2 时每行间隔去U和V的值,剔除部分信息。YUV 4∶4∶4 格式转换为YUV 4∶2∶2 格式如下:

YUV 4∶4∶4 格式转换为YUV 4∶2∶0 格式如下:

2 抗干扰特性的无线传输方案

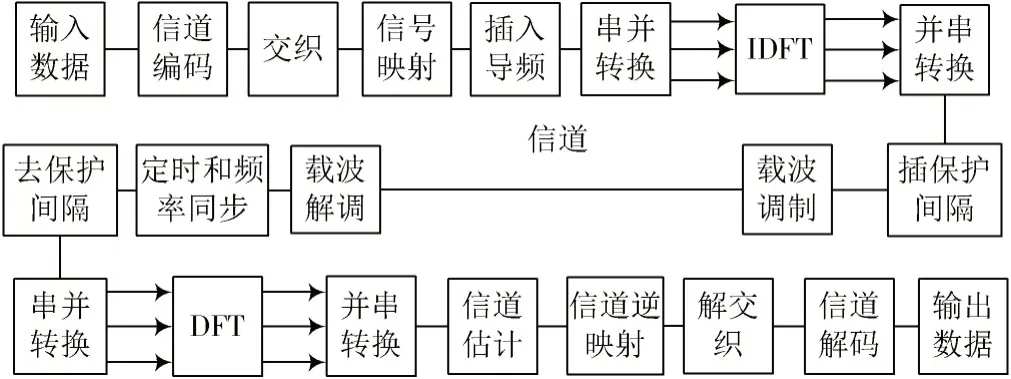

UHD 视频无线传输多用于紧急状况,对于复杂、恶劣环境传输的信号极易受到干扰。采用OFDM 多载波调制方法,在提高频谱利用率的同时,增强了抗干扰能力[11⁃16]。图3 为OFDM 系统原理框图。

图3 OFDM 系统原理框图

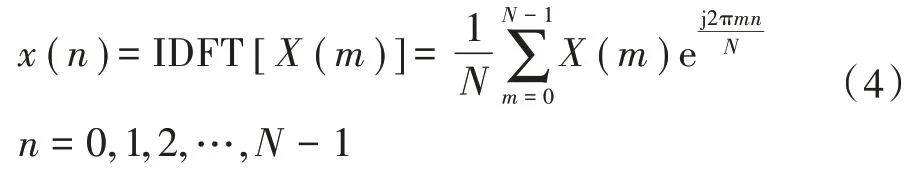

在发射端,将输入的高速比特流信号通过调制映射得到调制信号,通过串并转换生成N条并行的低速数据流,并将每个N个并行数据组成一个OFDM 符号。在OFDM 符号中插入导频信号后进行快速离散傅里叶反变换(IDFT),实现对每个OFDM 符号的N个数据进行调制,变成时域信号,如下:

式中:m为频域上的离散点;n为时域上的离散点;N为载波数。通常在每一时域OFDM 符号前加入保护间隔如式(5)所示,最后经过并/串变化及D/A 转换由发送天线发送出去。

在接收端,先完成定时同步和载波同步,在由A/D转换和串并转换得到信号,把得到的信号进行去前缀和DFT 变化得到如式(6)的信号,把FFT 解调后的信号和信道估值放入检测器进行相干检测,最后通过反映射及信道译码恢复出原始的比特流数据。

由式(4)和式(6)可以看出,利用IDFT 进行调制,把每条信道上的数据率降低,通过多个互不干扰的子信道并行传输,同时通过式(5)在时域上加入周期性前缀,可大大提高无线传输的抗干扰性。

3 UHD 视频流无线传输系统设计与实现

UHD 视频流无线传输系统发射端和接收具有相似的结构如图4 所示,利用异构多核ARM+FPGA 架构,在PS 端搭建Linux 系统,把HEVC 压缩后的ES 流转化为TS 流,通过UART 串口实现与电脑的通信,打印信息和进行功能选择,通过SPI 接口实现对AD9361 的初始化配置。在PL 端进行视频输入/输出、HEVC 编解码和OFDM 调制/解调,通过FPGA 实现硬件加速。利用FPGA 并行输出的特点,提高FPGA 和AD9361 间的数据传输速度。

图4 发射/接收端结构

3.1 发射端设计

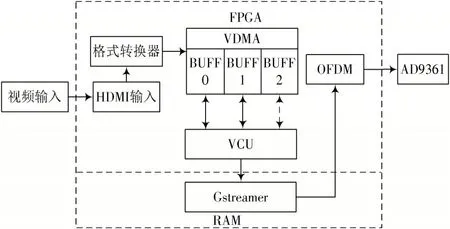

发射端框图如图5 所示,首先视频流经过HDMI 接口流入FPGA,FPGA 利用Video_PHY 和HDMI_Rx 组成的解码器把TMDS 数据流解码成RGB 格式或者YUV 格式进行缓存。由于HEVC 的编码只支持YUV 格式,所以要将非YUV 格式的数据转成YUV 的格式,并将转换好格式的YUV 数据存储到VDMA 中。本文设计中,VDMA 设为3 帧缓存,P 帧编解码只需要对当前帧和前一帧进行对比,而B 帧编码则需要后一帧图像进行预测,即B 帧编码共需要3 帧图像。把当前帧图像通过VCU 进行HEVC 编码生成ES 流,将ES 流通过总线传输到RAM 端,利用Gstreamer 实现将ES 流转换为TS 流码,在通过FPGA 端的OFDM 模组实现对TS 流的调制,最后将调制后的数据传输给AD9361,实现无线发送。

图5 发射端设计框图

3.2 接收端设计

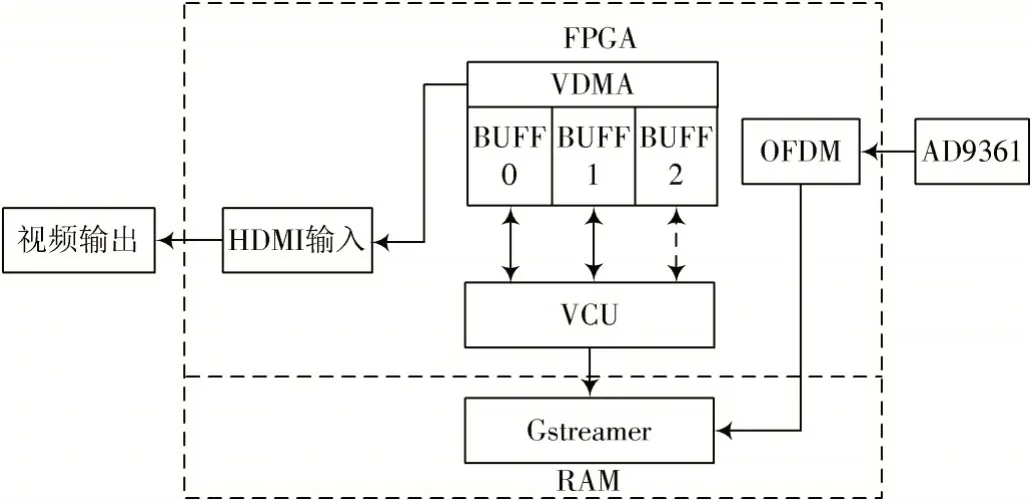

接收端框图如图6 所示。与发射端相似,AD9361把接收到的模拟信号转换为数字信号,经过OFDM 模块解调还原TS 数据流,再通过RAM 端利用Gstreamer 把TS 流还原成ES 流,并采用VCU 实现HEVC 解码,将解码出的图像存储到VDMA 中,通过Video_PHY 和HDMI_Tx 组成的编码模块,把YUV 格式的图像数据变成差分信号输出。

图6 接收端设计框图

3.3 TS 流生成设计

系统利用VCU 实现对图像的压缩并生成相应的TS流。视频流先经过YUV 的格式转换,转换为YUV 4∶2∶0 的格式,通过VDMA 把视频流传入VCU IP 核中,通过Linux 系统中的Gstreamer 将HEVC 编解码后的ES 流转换成TS 流。图7 为TS 流生成流程。

图7 TS 流生成流程

本文初始化VCU 为全P 帧编解码。在Linux 系统下通过ARM 端初始化VCU 的配置,经过YUV 格式变化的视频信号经VDMA 搬运到VCU 硬核中进行编解码,得到视频的ES 流,ES 流经过分组器得到PES,PES 流按照MPEF⁃2 标准分割成TS 包,实现TS 流数据包的转换。

在解码端,利用ARM 搭建的Linux 中的Gstreamer实现TS 流到ES 流的转换,转换后的ES 流通过总线传输给VCU 硬核进行HEVC 解码,把得到的原始视频存储在VDMA 的帧缓存区,最后通过PHY 和HDMI_TX 系统进行HDMI 信号输出,完成解码。

3.4 OFDM 参数设置

为了选取最优的无线传输带宽,对4K@60 Hz 视频流在不同传输带宽下压缩测试,根据测试结果在不同传输带宽下与解码后图像的SSIM 值进行对比,结果如图8所示。由图8 可以看出,传输带宽和SSIM 成对数式增长,尤其是当传输带宽大于10 MHz 时,SSIM 值增加速度明显变缓,即传输带宽大于10 MHz 时,画质近似于无损传输。为了节约带宽,系统把视频压缩后的传输带宽设定为10 MHz,考虑到OFDM 信号的完整性,左右各设有1 MHz 保护间隔。

图8 不同传输带宽下图像SSIM 值

表1 列出了本文设计的OFDM 通信系统的系统参数,其中,OFDM 子载波调制方式采用BPSK,子载波数目为512。循环前缀采用的OFDM 符号长度,保证多径干扰严重时仍可以防止符号间干扰。每个OFDM帧长度为15 个OFDM 符号长度,包含1个短训练序列,4 个长训练序列和10 个数 据OFDM 符号[16]。

表1 OFDM 系统参数

4 测试与分析

本文测试视频分为两种,一种是利用4K@60 Hz 的视频来验证,使显示器可直接观察UHD 视频流无线传输系统,使UHD 视频流无线传输系统生成相应的视频文件,通过和原始文件同一帧图像的对比,得到SSIM值;另一种是利用帧率测试视频,进行延迟测试。PC机通过GPU 输出两路完全相同的4K@60 Hz 视频流,一路直接连接显示器,另一路则通过UHD 视频流无线传输系统连接到显示器上。OFDM 系统按照表1 所示参数进行设定;HEVC 采用全P 帧编解码模式,在实验室内进行测试。

测试结果如图9 所示,图9a)所展示的是4K@60 Hz视频利用UHD 无线传输系统效果,左半屏显示的是直接从显卡输出的视频,右半屏显示的是经过UHD 无线传输系统所输出的视频。经过对比,2 张同一画面的SSIM 值约为0.98,具有较好的还原性。

图9 测试结果

图9b)则是延迟对比,同样左半屏显示的是直接从显卡输出的视频,右半屏显示的是经过UHD 无线传输系统所输出的视频。从视频帧数计数器来看,UHD 无线传输系统大约有35 帧的延迟,即约为500 ms 的延迟。而且在距离约为500 m 处可以得到图像,满足远距离UHD 无线传输的要求。

5 结语

本文研究了UHD 视频无线传输方法,使用异构多核ARM+FPGA 架构,采用VCU +HEVC 编解码算法,实现视频流的高压缩、快编解码的处理,有效解决了UHD视频流帧率不足的问题。根据该方法设计实现了4K@60 Hz 视频流的无线传输系统,系统采用OFDM 技术,硬件电路采用Zynq®UltraScale +™MPSoC 和AD9361 芯片搭建。实验结果表明,经过UHD 视频无线传输系统输出的视频流与原视频流的结构相似值(SSIM)约为0.98,画面延迟约为500 ms,在传输过程中没有明显的画面丢帧和缺失状况,实现了4K@60 Hz 视频流的高质量、抗干扰性强、低延迟的无线传输。