一种LVDS 高速数据传输电路*

乔 锐翟成瑞*张彦军

(1.中北大学电子测试重点实验室太原,山西太原 030051;2.中北大学仪器科学与动态测试教育部重点实验室,山西太原 030051)

目前,航天技术日新月异地改变,面对不同无法预料的航天情况,数据的存储依然起着至关重要的作用[1]。所以高速高可靠性数据传输和存储是非常重要的。然而,传统的接口技术都难以满足现在要求的数据传输速度。

LVDS 接口技术结合PCM 数据混合编码的方式,不仅能够加快数据的传输速度,还使得数据存储也稳定可靠;加上使用大容量的FLSAH,可以让系统存储更多的数据。LVDS 是具有极高效率的数据传输技术,是可以满足高速传输速率和远距离传输的低压差分信号,它的理论传输速度可达1.923 Gb/s,能满足高速数据传输[2]。

1 总体方案设计

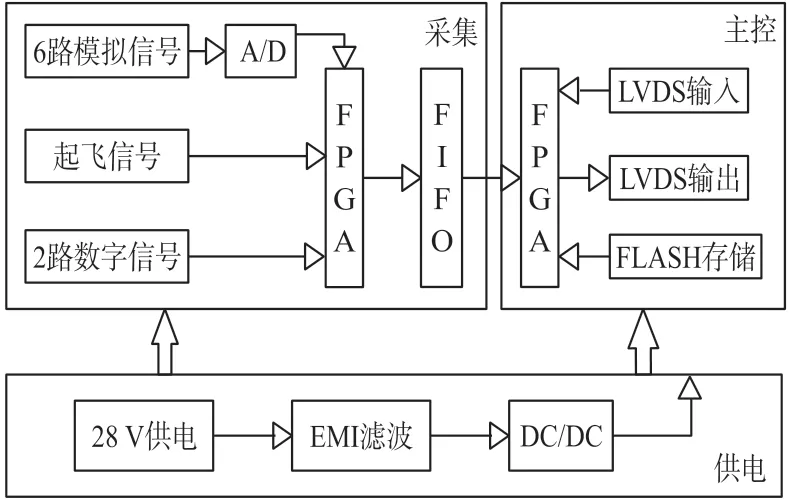

存储设备系统主要由采集模块、数据传输模块、供电模块组成。采集部分的信号输入分别为起飞信号、冲击信号、噪声信号等,其中冲击信号和噪声信号是模拟信号共有6 路,需要经过AD 模数转换在传到FPGA,起飞信号是数字量信号,可以直接被FPGA 接收,因此采用PCM 混合编帧的方式同时将模拟量和数字量递送FPGA,内部FIFO 对数据进行缓存。数据传输模块主要控制数据的存储和输入输出操作,FPGA 调取内部FIFO 的数据存储至FLASH存储芯片,采用LVDS 接口技术与地面设备互相通信。供电模块实现系统所需电压的转换,保证各部分的正常工作。系统工作框图如图1 所示。

图1 总体设计系统图

2 LVDS 接口硬件电路

2.1 LVDS 技术

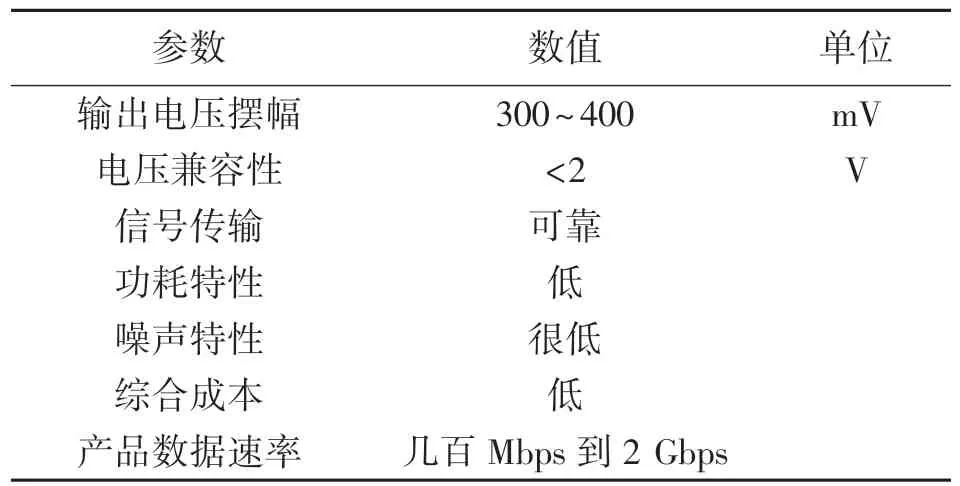

LVDS(Low Voltage Differential Signaling),也就是低压差分信号传输,是一种满足当今高性能数据传输的新型技术[3]。该技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点,或者一点对多点传输。最重要的是它具有低功耗和很低误码率的优点,而且还有低串扰以及低辐射特点[4]。它在对信号要求较高的系统中会有更佳的应用。LVDS 主要参数如表1,从下表能够知道,LVDS 的传输速度可以达到百Mbps[5],甚至更高。

表1 LVDS 主要参数

2.2 LVDS 接口收发电路

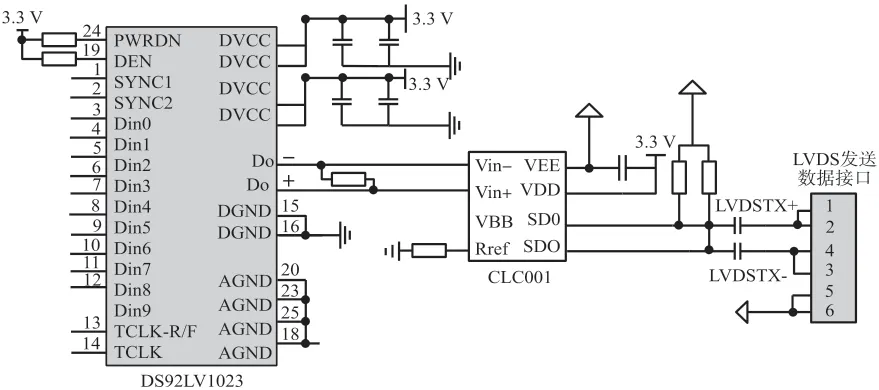

LVDS 接口收发电路主要采用的芯片组为DS92LV1023/DS92LV1224,加入串行数字电缆驱动器CLC001 可以将发送端输出的差分电压提升。自适应电缆均衡器CLC014 加入到接收电路中,可以进行多级自适应滤波[6],图2 是LVDS 发送数据接口电路,图3 是LVDS 接收数据接口电路。

DS92LV1023 将接收来源于FPGA 的并行数据信号,并将其转成串行数据输出到串行数字电缆驱动器CLC001 提高信号传输质量[7]。电路中加入上拉电阻,可以起到限制电流作用。LVDS 信号通过线缆连接传输到自适应电缆均衡器CLC014 均衡。CLC014 具有低功耗和低抖动性的性能,内部含有自适应滤波器,差分信号输入后会进行滤波,并对信号进行恢复;恢复后的信号传输至驱动部分以产生自动平衡信号,该信号用来反馈设置自适应滤波器的宽带以及增益,内部载波模块产生检测信号发送给输出驱动模块,以弥补传输过程中信号的损失,最后DS92LV1224 解码器将传输回来的串行数据转成并行数据[8]。同时,利用数据与时钟恢复技术建立并行数据的时钟,接收并行数据。

图2 LVDS 发送数据接口电路

图3 LVDS 接收数据接口电路

3 FLASH 模块逻辑控制

3.1 FLASH 选型

数据存储模块完成FLASH 存储芯片的读、写和擦除操作。核心芯片选用三星公司生产的FLASH 存储芯片K9WBG08U1M,该存储芯片共有16 384 个存储块,每个存储块有64 个存储页,每页可以存储4 096 byte,整个存储芯片存储容量为4 GB,页编程时间为200 μs,块擦除时间为1.5 ms[9]。对该芯片的存储和读取过程均需通过FPGA 内部FIFO 进行数据缓存以匹配数据传输速度。ADC 转换数据写FLASH 存储芯片时,先对转换数据进行编帧,即每帧数据中加入帧标志和帧计数组成存储数据,再将存储数据缓存至内部写FIFO 模块,然后将FIFO 中数据按照FLASH 地址依次写入FLASH 存储芯片。读取FLASH 芯片中存储数据时,则需要按照FLASH 地址将存储数据读取至内部读FIFO 模块,再将FIFO 数据输出至数据传输模块。具体结构如图4 所示。

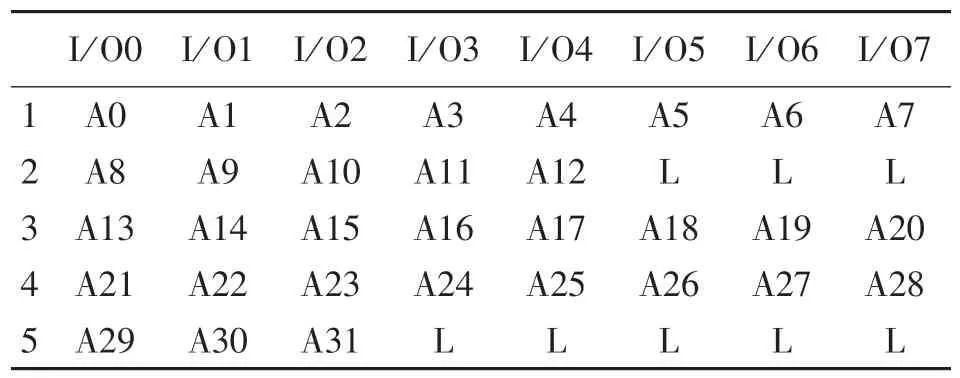

当然,FLASH 在擦除、编程和读取的这一过程里,就是周期地址的不断编写;5 个周期地址,2 个周期列地址和3 个周期行地址在FLASH 中的地址定义如表2 所示。

图4 FLASH 内部结构

表2

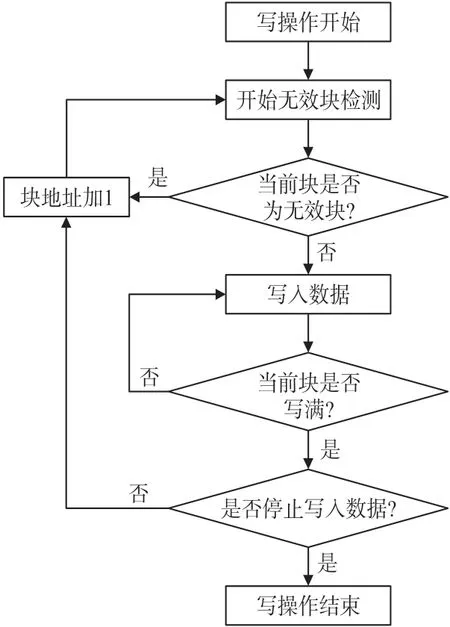

3.2 FLASH 高速写入

FLASH 存储器收到来自FLASH 控制模块的指令,会根据优先级为擦除、写入、读取进行操作[10]。无效块是存储器中不能进行操作的。在NANDFLASH 芯片出厂的时候,无效块的位置就被随机分布在每个块第一页的空闲首字节上,假如它的地址数据为00h,就会认定为无效块。无效块管理就是要检测新旧无效块,保证存储器正常工作。

为了提高FLASH 写入的有效速率,缩短等待时间,提高编程的速度,拟采用双平面交叉编程,结合流水线操作以便能够很好的提升设备存储速度。存储芯片K9WBG08U1M 内部集成2 个互不干扰的存储空间,一共8 个plan 分为4 组,为双平面交叉编程提供基础。利用芯片内部不同平面可以单独进行操作的特性,连续循环对各组进行数据加载和页编程操作,即可大幅度提高存储速度。双平面交叉编程操作流程图,如图6 所示。

图5 FLASH 写入流程图

图6 双平面交叉编程操作流程图

4 实验验证和结果分析

实验结果验证方面主要考虑实际环境中可能出现的影响实验数据的各种恶劣条件。使用信号发生器模拟产生起飞信号、冲击信号和噪声信号,对地面的读数装置采取高低温、振动、老炼等方法进行测试。测量过程中在300 ms 时间内读取了1.8 G 的数据;存储数据用了59 s。使用HexEdit 软件进行结果观察,如图7 所示。结果分析表明,数据传输完全正确,不存在丢帧或者误码的现象。经过后续多次测试,模块在传输过程中出现丢帧现象的几率非常低,符合规定的误差范围,充分验证了数据传输的可靠性。

图7 混合编码的数据