浅谈基于CPLD的G.D伺服的抗干扰系统设计

李华文,倪骏,程倩

(红云红河烟草(集团)有限责任公司昆明卷烟厂,云南 昆明 650202)

随着现代智能化的进步,现代工业发展中,伺服电机的精准度标志着一个国家的工业和科学技术水平是否先进。我国的伺服控制系统虽然发展迅速,但是和国外的伺服控制系统比还有很大的差距;差距表现在响应频率方面,我国伺服电机的响频率几乎只能达到国外的一半;还有就是控制核心,控制核心基本还是依靠国外进口;另外,就是稳定性。昆明卷烟厂的卷包机G.D控制伺服系统是全厂对伺服控制稳定性和精度要求最高的地方。由于使用年限比较长,并且各种线路老化造成伺服控制系统受到各种干扰信号的干扰,对系统稳定性造成巨大影响;无论伺服系统采用速度控制还是采用位置控制,速度反馈信号都在这两种伺服闭环控制系统中起着很重要的作用,而CPLD主要就是速度反馈信号采集和处理,所以,通过更换CPLD提高速度反馈信号的精度,提高G.D伺服的抗干扰性能。

1 CPLD选择设计

1.1 编码器选择

对于伺服测速信号,必须满足极高的更新速度和极高的测试精度,光电编码器正好能满足这两种要求,所以,速度反馈中的传感器通常选用光电编码器。编码器通过A、B、Z三个脉冲来实现,A相脉冲主要是用来做计数脉冲用的,A相脉冲所对应的B脉冲主要是用来作为鉴相脉冲用的,就是用来确定所对应的编码器的旋转方向的。如果A相脉冲的相序滞后B相脉冲相序90°时,这时编码器翻转;如果A相脉冲超过B相脉冲90°时,这时候编码器正转。除了A、B脉冲还有Z相脉冲,它是表示编码器零位的方式。

1.2 M法测速

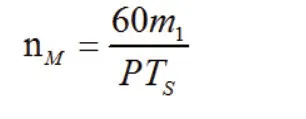

M法测速度反馈就是就是测频法,它的原理就是在固定时间内对输出的A、B两相脉冲进行个数统计,然后,依据统计出来脉冲个数的数量确定在所测时间内的转轴平均速度的准确值。以下是它的速度计数公式:

式中,nM表电机的转速(r/min);P表示编码器的线数;TS表示脉冲计数时间(s);m1为测速时间内的编码器脉冲数量。

1.3 CPLD测速原理

由于直接检测脉冲虽然方法简单,但是,伺服电机在低速运转的情况下,结果更新很慢,所以运算量就会变得很大,使得CPLD难以实现运算处理,所以,将对CPLD中高精度和高速的方案进行改进,这样加快起结果刷新速度,以提高速度反馈信号的准确度。

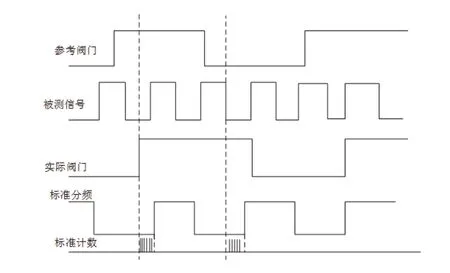

我们可以把选取一个阀门作为参考,它是一个方波,它的占空比为50%,我们只是假定高电平,实际情况是它的高电平期间并不是实际的阀门时间。开始计数的开始端是参考阀门高电平期间的第一个脉冲,从第一个脉冲开始计数,计数结束端是参考阀门的低电平期间的第一个上升沿,到达后立即停止计数;开始端到停止端之间时间就是实际的测速时间,这样就可以确保被测编码器信号是一个完整的计数周期。通过以上的理论原理简介,从而我们可以知道:参考阀门时间是一个固定值,它不会因为情况不一样发生改变。伺服在低速运转的时候,往往会发生在参考阀门低电平期间,没有信号的上升沿这种情况,这种情况会使得测速时间变长,从而减小更新时间;伺服在中高速运转期间,伺服速度变化变得比较快,并且参考阀门的低电平时间非常久,从而使得更新速度变得非常慢。导致参考阀门在中高速时低电平与高电平时间都变得比较短。这时,高电平时间大约是0.2ms,此时,测速时间也同样基本等于0.2ms;在伺服低速运转情况下,低电平与高电平时间也同样发生相同变化,时间都适量地变长,从而导致参考阀门的占空比小于它本来的基准值50%,这时,测速时间基本为0.3ms,如果想解决低速时出现测量多个脉冲从而会导致测量时间增加的问题,并且时间脉冲的计时不利用采用分频计数,一般都是直接对高频时钟进行计数,这样也会带来缺点,那就是使计数的字长变得更长,虽然字数变长,但这样也会使得计数精度会大大提高,然后,通过CPLD计算,改进的高速、高精度、连续测量方法就会提高速度的测量精度以及更新速度,而速度计算公式不变原理图如图1所示:

图1 CPLD测速原理

2 抗干扰

2.1 抗干扰原理

伺服系统反馈信号需要极高的精度,所以,我们在实际生产中,必须考虑速度反馈信号中的干扰信号部分。速度反馈是常用的反馈信号,但是,它的干扰会使得编码器在计数时的时候导致脉冲计数值提高,从而使得速度反馈信号的测量值与实际值结果不符,所以,对系统的稳定性造成影响。所以,我们采用闭环控制降低干扰。

2.2 反馈信号干扰来源

伺服电机运用的地方,往往都有大型的设备,导致伺服系统发生振动,使编码器也发生抖动,就会产生误码脉冲。伺服电机在方向切换频率高和速度比较低的场合时,编码器的码盘缝隙边缘会随着伺服电机一起出现小晃动,这种晃动频率比较高,这样就及易产生干扰,A、B之间相差的90°的相位关系在抖动的情况下是固定的,干扰信号使这种相位关系发生改变,抖动会让编码器误认为是计数脉冲,使得计数结果偏高,从而造成速度测量结果与实际情况不一致。

在速度传输过程中,也可能出现随机的共模及差模信号。屏蔽及硬件之间隔离技术在硬件抗干扰上都被采用来对伺服系统反馈信号进行干扰处理。可是,伺服系统在运行过程中会出现电磁干扰,或者少数误操作情况,这些都会随机出现,从而对伺服速度反馈信号发生干扰。

2.3 干扰信号分类

含伪干扰脉冲的干扰信号和含伪干扰脉冲的干扰信号是常见的两种干扰信。同方向含伪干扰脉冲的干扰信号和反方向的含伪干扰脉冲的干扰信号又是常见的两种含伪干扰脉冲信号。

2.4 干扰信号处理

码盘缝隙边缘引起的干扰信号的滤除原理:滤除编码器信号就是一种边沿信号,产生的感染也会是边沿干扰信号,所以,整个系统就是对部分含伪干扰脉冲的干扰信号进行滤除。并且,在引入了方向信号这种判断条件的情况下,整个CPLD和DSP结合起来,会对滤除反方向含伪干扰脉冲干扰信号起着很大的作用。

本次通过改进后的GPLD对干扰信号进行过滤,然后,通过GPLD和DSP相结合,在信号传到DSP之前,经过GPLD的时候,就将无伪干扰信号和含伪干扰信号进行处理,虽然不能完全消除干扰信号,但是,可以减少大部分干扰信号。

如下列这种情况:当伺服电机沿着正方向旋转时,假定这时不存在干扰,那么A、B的电平状态会根据随机干扰信号的滤除原理和码盘缝隙边缘引起的干扰信号的滤除原理,这样就会使得CPLD发挥作用,在CPLD 中完成码盘缝隙边缘引起的干扰信号的滤除和无伪干扰脉冲的干扰滤除。

3 实验结果分析

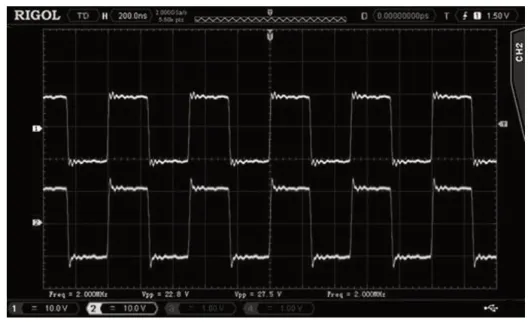

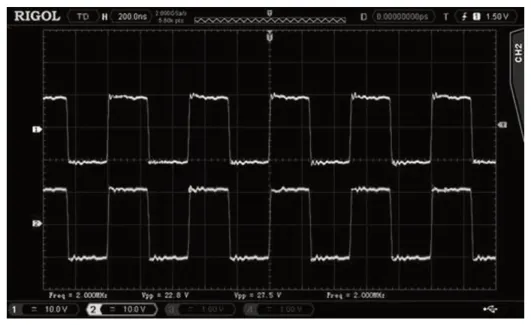

本次实验采用示波器分别采集A、B两相反馈信号波形图,来比较实验结果:

图2 未使用改进GPLD波形图

图3 使用改进GPLD波形图

可以看出,通过使用改进后的系统,干扰明显减少。

4 结语

本次通过对伺服系统GPLD的改进,可以看到实验结果得到明显改善,干扰信号变少,提高了G.D伺服的抗干扰性能,从而提高了整套系统的性能。