基于FPGA 的Nandflash 存储模块设计

唐超

(深圳市汇顶科技股份有限公司,四川 成都610041)

1 概述

该基于FPGA 的Nandflash 存储模块的设计是隶属于随钻测井系统的科研子项目,总体上要求该模块达到以下指标:a.数据出错概率不大于0.1%。存储模块作为随钻测井系统中保存原始数据的唯一单元,其可靠性和安全性就是仪器的生命线,保证数据安全可靠将是本设计的重中之重。b. 存储容量不小于32Gb,电路面积尽可能小。随钻测井系统一次工作会生成大量的数据,一般最大可达30Gb,为保证测井数据不丢失,存储模块必须有足够的空间容纳数据,同时要留出一定裕量空间。另外仪器上的空间资源是非常珍贵的,要求在设计存储模块时在保证存储容量的前提下应尽量减小电路面积。c.数据下载速率不小于5Mbps。

Nandflash 属于闪存的一种,是一种非易失性存储器,相较于Norflash 具有单片容量大、读写速度快、功耗低、温度性能好等优点[1],但其控制器设计相对也更加复杂。目前常见的随钻密度测井系统的存储介质一般都是Norflash,主要是因为Norflash控制简单、操作方便,但由于Norflash 单片容量较小,常见的有512Mb/1Gb/2Gb[2],一般使用Norflash 的随钻测井系统的存储容量都较小,因为要想实现较大的存储容量将会占随钻测井仪器上很大的物理空间,这在实际应用中是不被允许的。因此本设计使用Nandflash 作为存储介质,牺牲控制器的复杂度换取存储大容量、小面积的特性。

对于Nandflash 控制器的选择,本设计在全面比较FPGA 和MCU 的基础上,决定采用并行处理能力更强的FPGA 作为控制器,同时由于FPGA 的设计更为灵活,发现问题可直接更改设计,减少了投片的风险,节省开支[3]。

2 硬件设计

Nandflash 存储模块包括数据采集、实时存储以及数据下载三个单元。采集单元由FPGA 控制高速ADC 实现;实时存储单元由FPGA 控制Nandflash 实现,同时使用RAM缓存数据;数据下载单元由FPGA 控制UART 收发器实现。按照数据采集- >缓存- >存储- >下载流程,硬件设计考虑如下。

2.1 数据采集

构建“FPGA+ADC”的数据采集架构,通过FPGA 控制高速ADC 采样、量化函数信号发生器输出的稳定模拟信号,将采样数据作为存储模块的输入数据存入存储器中。

2.2 数据缓存

构建“FPGA+双RAM”数据缓存架构,采用乒乓切换技术[4],一片RAM用于实时缓存ADC 采集到的数据,另一片RAM 用于将缓存的数据存入Nandflash,以保证数据连续采集。在数据下载阶段,一片RAM用于接收缓存从Nandflash 中读取的数据,另一片RAM用于将已缓存好的数据上传到PC 端,可实现数据的连续不间断下载。

2.3 数据实时存储

以Nandflash 为存储介质,FPGA 为控制器, 构建“FPGA+Nandflash”数据实时存储架构,由FPGA 控制Nandflash实现数据的实时存储。

2.4 数据下载

采用UART 串口总线为数据下载总线,以FPGA 为串口控制器,构建“FPGA+ UART 收发器”数据下载架构,同时使用乒乓切换技术,实现数据连续不间断下载。

基于以上考虑,设计的基于FPGA 的Nandflash 存储模块结构框图如图1 所示。FPGA 通过标准的O NFI 接口与Nandflash通信,实现数据的写入与读出;使用两块乒乓RAM 缓存数据;通过UART 串口将数据传输下载搭配PC 端。

图1 基于FPGA 的Nandflash 存储模块硬件框图

3 软件设计

软件设计的主要任务是在FPGA 内设计实现各种功能接口,保证各功能单元正常运行,下面逐一介绍各功能接口。

3.1 数据采集

在FPGA 内实现一个ADC 接口控制器单元,控制高速ADC定时连续采集量化信号发生器输出的信号,并将采样得到的数据作为存储模块的输入数据。

3.2 数据缓存

在FPGA 内实现RAM接口控制单元,该接口控制单元可由FPGA 厂商提供的IP 核生成。数据缓存采用的是乒乓切换技术将数据依次缓存于在两块RAM中,在RAM接口单元内,ADC端的输入数据将被转换为RAM地址,然后在对应的地址上执行加一操作,完成数据记录。上电初始,系统默认设置RAM1 为用于缓存数据的RAM,RAM2 为空闲态;正常工作期间,当接收到切换RAM命令时,RAM接口控制单元首先检测当前RAM是否正在被占用,如果有程序正在对RAM进行操作,那么RAM接口控制单元就会等到RAM空闲的时候再切换RAM,否则立即切换。

3.3 数据存储

在FPGA 内实现Nandflash 控制器模块。设计的重点是坏块管理和ECC 校验的实现,本设计中使用的是基于块替换的坏块管理办法,基于汉明码的ECC 校验方法。控制器模块逻辑结构图2 所示,分为底层逻辑和上层逻辑,其中底层逻辑是对Nandflash 的基本操作,上层逻辑是将基本的Flash 操作进行封装以实现实际功能需求。

3.3.1 坏块管理

坏块是指Nandflash 中不能保证数据可靠的block 块,坏块一般有两种来源:一个是出厂坏块,厂商会进行标记,另一个是用户坏块,是用户在使用过程中产生的[5],所谓坏块管理就是正确识别、标识坏块并采用一定的办法保证坏块的存在不影响Nandflash 的使用。设计中使用了三种方法来认定坏块:第一,第一次上电时读取特定位置的出厂信息,找到出厂坏块;第二,当擦除某个block 失败时,将该块标识为坏块;第三,当发生编程失败时,直接将当前block 标识为坏块。本设计采用的是基于块替换的坏块管理办法,基本思路是将Nandflash 存储空间划分为划分为工作区和保留区,保留区占比一般为2%左右[6],工作区是数据存储区;当工作区出现坏块时,从保留区找出一块空闲的好块,更新逻辑地址- 物理地址映射表,将坏块对应的逻辑地址映射到保留区的好块上,从而达到规避坏块的目的。基于块替换的坏块管理办法可使逻辑地址始终保持联系,对上层用户来说是感觉不到坏块有坏块存在的。

3.3.2 ECC 校验

图2 Nandflash 控制器逻框图

Nandflash 由于其物理特性和制造工艺的限制,存在bit 翻转误码现象,需要进行纠错处理。因此使用了基于汉明码(hanmming code)的ECC 校验方法,该方法能够纠正1-bit 错误,发现2-bit 错误[7]。ECC 校验方法的基本思路是当往Nandflash中写入数据时,把每256 字节的原始数据按照一定的规则进行异或运算生成3 字节的ECC 校验码,然后将ECC 校验码写入OOB 区(out-of-band);当从Nnandflash 中读取数据时,把每256字节的读出数据再按相同的规则进行异或运算生成3 字节的ECC 校验码,最后将写入时生成的ECC 校验码和读出是生成的ECC 校验码按位异或,若结果为全0,则表示无错误(或出现了ECC 无法纠正的错误),若结果中有11 个bit 为1,则表示存在一个错误且可以纠正,若结果中自存在1 个bit 为1,则表示OOB 去发生错误,其余情况表示出现了无法纠正的错误。

3.4 数据下载

在FPGA 内实现UART 串口控制单元。串口控制单元的核心是UART 收发串口,再辅以命令解析、执行模块,当收到下载数据的命令后,自动完成数据下载。

4 测试结果

实验条件如下:

4.1 FPGA 芯 片 为 Xilinx 的 XA3S500E-4PQ G208;Nandflash 存储器为青岛智腾的LDMF4GA;ADC 为TI 的ADS7883;SRAM 为CYPRESS 的CY7C1049CV 33;UART 串 口芯片为HO LT 公司的HI-4853。

4.2 测试环境:Nandflash 控制模块、上位机PC。使用FPGA内部生成的模拟数据测试,通过写入1Gb 数据后再读出,观察数据是否与预期一致,表1 列出了数据可靠性测试结果,共进行了4 组测试。

表1 模块读写可靠性测试

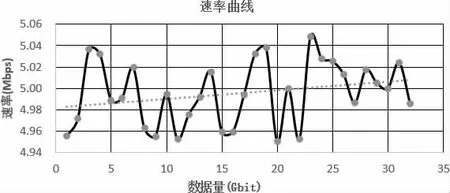

使用 FPGA 内部生产的模拟数据, 分批写入1Gbit.2Gbit,3Gbit,… … ,30Gbit, 31Gbit, 32Gbit,测试模块的数据下载速率。图3 为下载速率测试结果,其中值为100 次实验平均值。

图3 下载速率测试曲线

结果分析,基于FPGA 的Nandflash 存储模块相较于常规的以Norflash 为存储介质的存储模块在容量上有了很大的提高,同时电路面积也减小了很多,数据错误概率约为0.029%,数据下载的平均速率约5Mbps,以上指标均满足设计要求。此外,所有的控制接口单元均在FPGA 内部以硬件电路的形式实现,降低了对操作系统的依赖。

5 结论

本文介绍了基于FPGA 的Nandflash 存储模块的性能指标要求、软硬件设计,该型存储模块针对随钻测井系统对数据可靠性要求高、数据量大的特点,定制化的给出了基于“FPGA+Nandflash”架构的设计方案,其核心就是通过FPGA 对Nandflash 进行读写调度和差错控制,辅以数据采集和下载功能。本设计的重点难点是Nandflash 控制核心的设计,其中尤以坏块管理和ECC 校验的实现最为重要,这是保证数据可靠性的关键。

当前,该型存储模块已成功实现商用,各项性能指标均满足用户需求。下一步考虑从数据的实时压缩和Nandflash 磨损均衡的实现这两方面入手,以期大幅提升模块的存储容量、数据的可靠性以及延长Nandflash 的使用寿命。