高可靠硅压力式静压信号处理电路设计与实现

周 朋, 张兴宇, 刘靖雷, 唐燕彬, 王立武

(北京空间机电研究所,北京 100076)

返回舱回收分系统在返回过程中需要在指定高度根据开伞控制信号完成开伞动作,降落伞打开后,降低返回舱着陆速度,实现回收软着陆。其中指定高度开关信号由静压高度控制器给出,目前中外静压高度的测量通常采用膜盒和硅压技术实现。膜盒能够跟随外界气压变化而产生弹性形变,从而使与其相连的中心杆产生位移,位移量与外界气压符合一定数学关系,当外界气压达到一定值时,中心杆随之到达指定位置,接通触点,发出指定高度信号,中国目前已经掌握了膜盒敏感元件的生产技术,航空领域中大部分飞机采用的就是基于膜盒原理的高度测量单元[1-2],神舟飞船的开伞控制信号也是由膜盒式静压高度控制器给出[3]。虽然膜盒工艺简单,便于生产,但其灵敏度低,机械放大机构使误差增大,性能不稳定,且滞后、弹性后效,使得准确度降低。相比于膜盒式静压高度控制器,硅压力式静压高度控制器利用单晶硅的压阻效应,制成力电变换器,具有更高的精度和抗振性能,同时减小了体积,降低了功耗。外国航空航天领域已被广泛采用,中国硅压力传感器的生产工艺技术有限,应用主要依靠进口,目前中国部分飞机的高度表采用硅压力传感器实现,对体积重量有一定要求的无人机,通常也采用硅压力传感器作为高度敏感元件[4-5]。新一代载人飞船的高度敏感元件选用了硅压力式静压高度控制器和膜盒式静压高度控制器组成异构双机冗余系统提高系统可靠性。其中硅压力式静压高度控制器由静压高度信号盒和静压信号处理器组成。静压高度信号盒中的高精密半导体电阻应变片组成惠斯顿电桥,当外界气压发生变化时,半导体材料产生压阻效应,并依靠良好的弹性形变来进行力电变换,将气压的变化映射至0~5 V的电压模拟量输出。静压信号处理器对采集到的模拟量信号进行处理,将处理后的模拟信号与指定高度相对应的基准电压进行比较,得到对应指定高度的开关控制量,两个单机均采用三模冗余可靠性设计。

基于此,现设计静压信号处理器,研究静压信号处理器的电路组成和优化,并通过仿真计算,论证基于三模冗余备份静压信号处理器的高可靠性,最后通过试验验证电路设计优化对系统性能的改善。

1 静压信号处理器组成

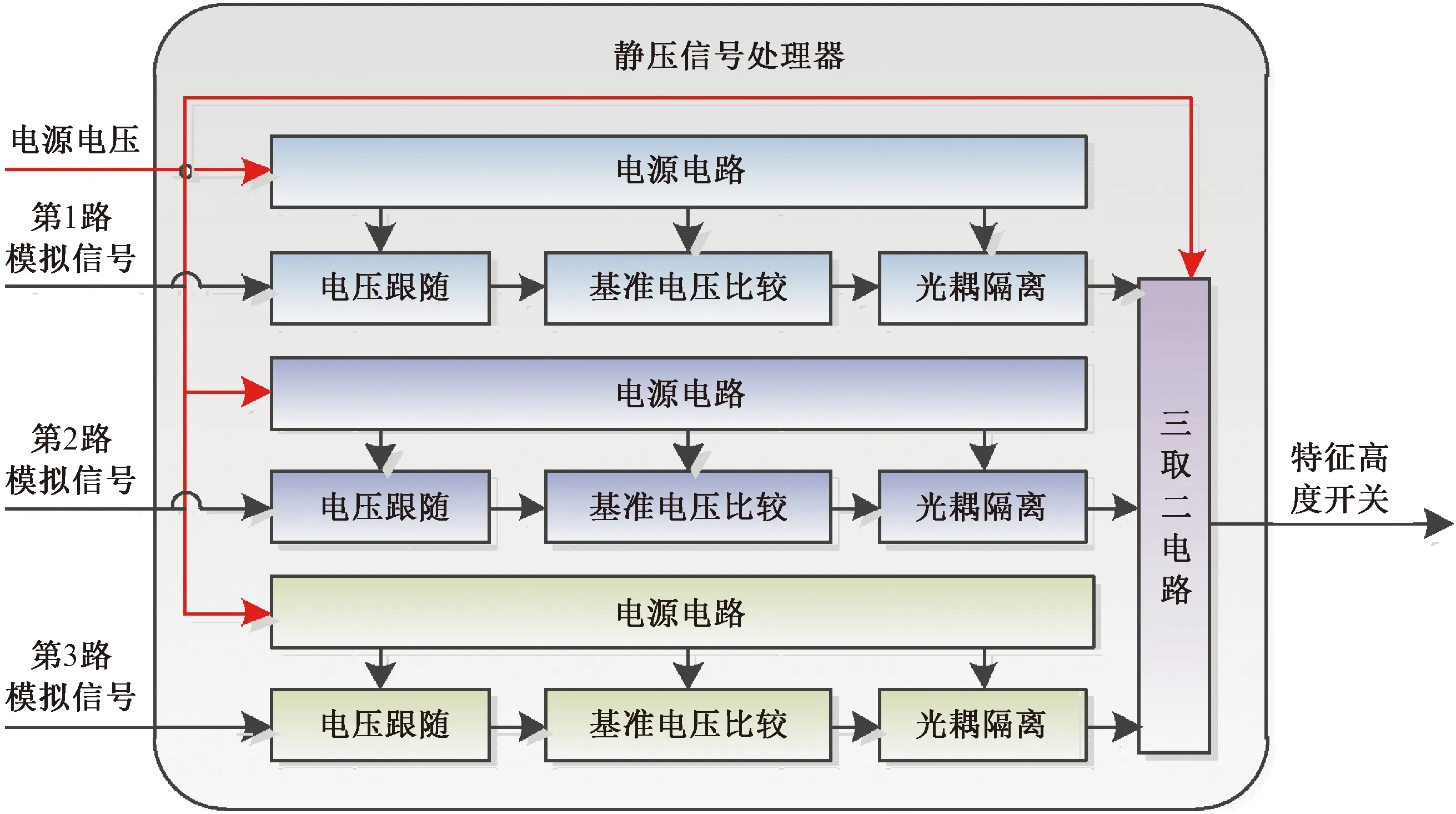

静压信号处理器为三模冗余结构,每一路都是由电源电路、电压跟随、基准电压比较和光耦隔离电路模块组成,最终三路均输出指定高度的开关信号,3个开关信号经过三取二电路进行逻辑判断后,最终输出代表指定高度的特征高度开关,静压信号处理电路组成框图如图1所示。电源电路模块将系统总体提供的+28 V电源电压经过熔断器、滤波器和直流对直流变换器(DC-DC converter)转换为±12 V电源,给电路中的集成芯片供电,同时+12 V经过线性稳压器得到的+5 V电压用于生成代表指定高度的基准电压。静压高度信号盒输出的静压信号模拟量进入静压信号处理器,首先连接电压跟随模块,进行阻抗匹配,随后通过基准电压比较模块与代表指定高度的基准电压模拟量信号相比较,得到代表指定高度的开关量信号,此开关量信号通过光耦隔离电路将前后级电路进行隔离保护。最终三路开关量信号通过三取二表决电路的判断,输出具有较高可靠性的特征高度开关信号。

图1 静压信号处理器功能框图Fig.1 The function block diagram of the static pressure signal processor

2 静压信号处理器电路设计和实现

2.1 电源电路

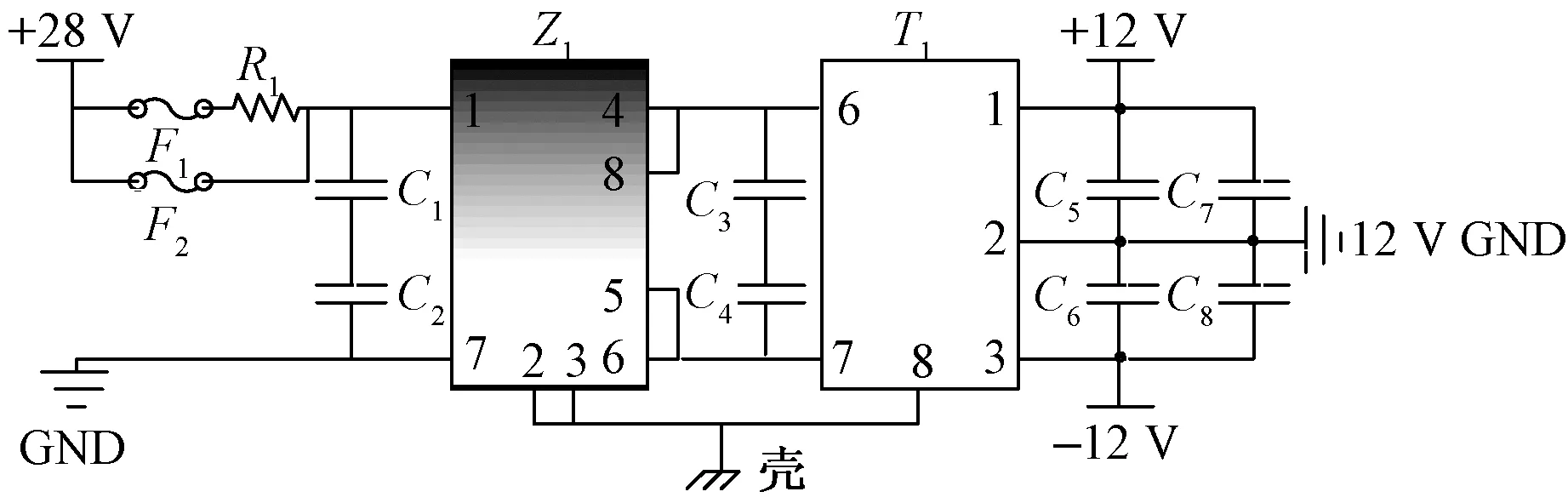

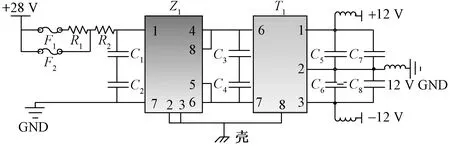

电源电路将+28 V系统电源转换成为各个集成芯片供电所需的±12 V电源以及生成基准电压的+5 V基准电源。生成±12 V的供电主路原理图如图2所示。

图2 供电主路原理图Fig.2 The schematic of the Power main road

F1、F2和R1组成过流保护电路,熔断器F1、F2并联提高系统可靠性,其中一个支路中连接电阻R1,实现两个熔断器的可测试性。+28 V电源通过过流保护电路连接至滤波器FMSA-461(Z1),后通过DCDC-MSA2812(T1)变换,输出±12 V电源,±12 V电源中间连接电容进行滤波稳压。

基准电压供电电路如图3所示,指定高度的基准电压是由基准电源经过电阻分压得到,DC-DC输出电压纹波比较大,不适合用作基准电源使用,线性稳压器输出的电压更加稳定,因此选用线性稳压器MSK5215-5.0H(D1)将+12 V电压变换得到的+5 V电压作为基准电源使用,电解电容C1和C3滤除低频噪声,电容C2滤除高频噪声。

图3 基准电压供电电路原理图Fig.3 The schematic of the reference voltage supply circuit

2.2 电压跟随电路

代表高度的静压模拟量信号传输至静压信号处理器后,首先连接由电阻R1和电容C1构成的低通滤波器,然后连接至由LM124(D2)组成的电压跟随电路。如图4所示,电压跟随电路的输入高阻抗和输出低阻抗的特性完成了前后级电路间的阻抗匹配,起到了承上启下的作用。

图4 电压跟随电路原理图Fig.4 The schematic of the voltage follow circuit

2.3 基准电压比较电路

2.3.1 基准电压比较电路设计

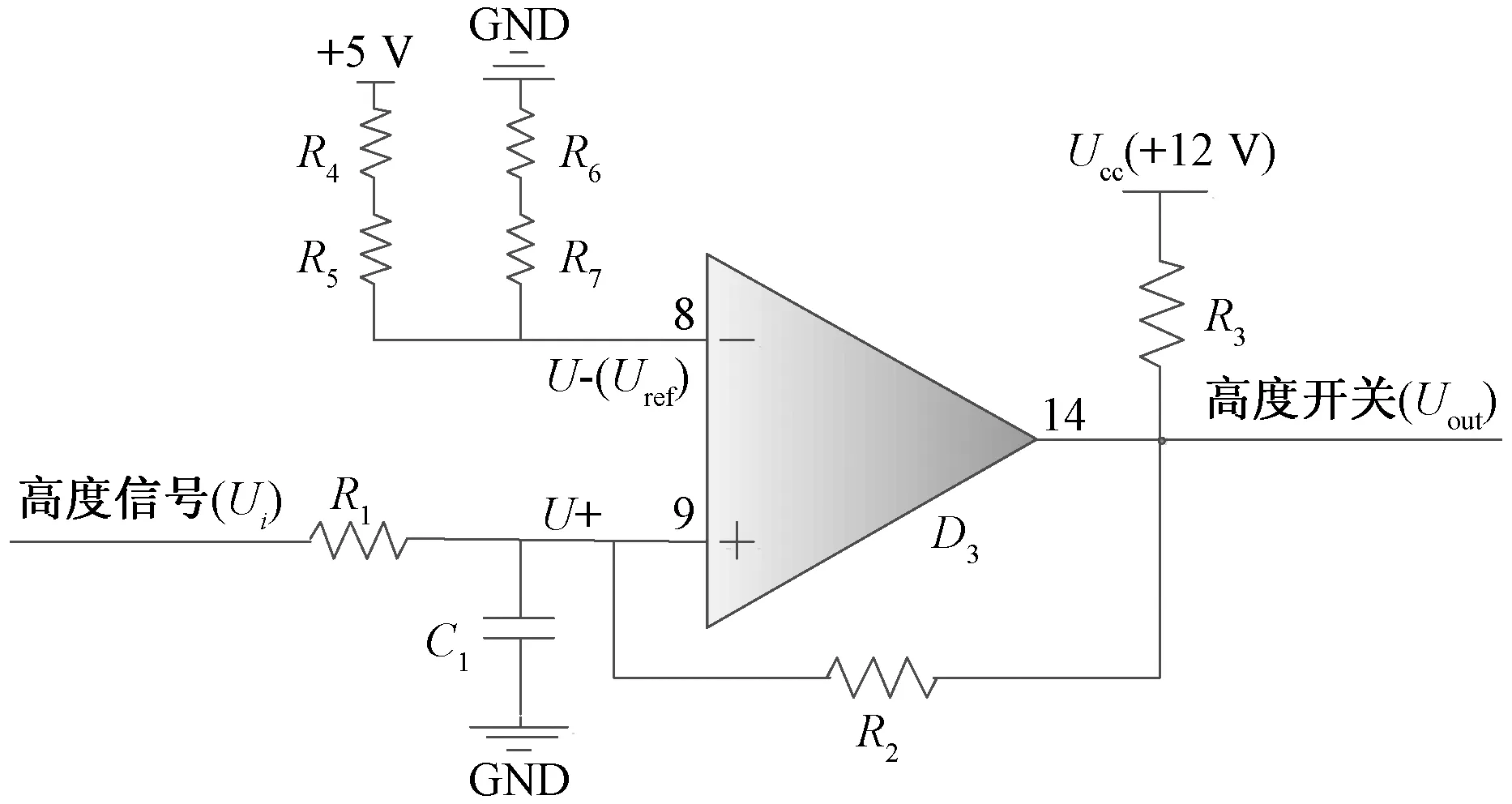

基准电压比较电路采用同相迟滞比较电路,电路原理图如图5所示。电阻R1~R3为迟滞宽度调试电阻,电阻R4~R7为生成基准电压的分压电阻,基准电源+5 V可以通过这4个电阻分压得到代表指定高度的基准电压Uref。此基准电压作为比较器的负端输入:U-。高度信号模拟量连接至比较器LM139(D3)的正端:U+,当U+大于基准电压U-时,比较器的输出为高电平,反之为低电平。

图5 基准电压比较电路原理图Fig.5 The schematic of the reference voltage comparison circuit

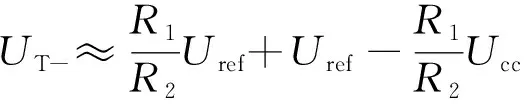

2.3.2 基准电压比较电路原理

基准电压比较电路采用同相迟滞比较电路来防止信号干扰造成的输出电压Uo的抖动,同相迟滞比较电路原理如下。

当输入高度信号Ui由低向高变化时,U+开始时小于U-(Uref),比较器D3输出低电平,当Ui增大到正向阈值电压UT+时,使得U+=U-,随着Ui的继续增大,U+大于U-,比较器D3输出高电平;反之,当输入高度信号Ui由高向低变化时,U+开始时大于U-,比较器D3输出高电平,当Ui减小到负向阈值电压UT-时,使得U+=U-,随着Ui的继续减小,U+小于U-,比较器D3输出低电平。当UT+大于UT-时,形成迟滞环,如图6所示。

图6 电压传输特性图Fig.6 The characteristics of the voltage transmission

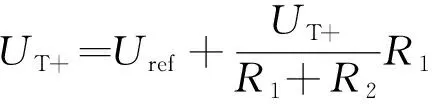

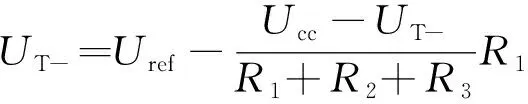

迟滞宽度公式推导过程如下:

在输入电压Ui由低向高的变化过程中,当电压Ui到达门限电压UT+时,输出电压从低电平向高电平翻转,UT+计算表达式为

(1)

即

(2)

在输入电压Ui由高向低变化的过程中,当电压Ui到达门限电压UT-时,输出电压从高电平向低电平翻转,如图6所示,可以推出UT-计算表达式为

(3)

式(3)中:Ucc为比较器LM139(D3)的输出端所连接的上拉电阻处的电压。

即

(4)

R3受后级电路的约束,选定为24 kΩ。

取R2≫R3,可将公式简化为

(5)

由式(2)、式(5)可知

(6)

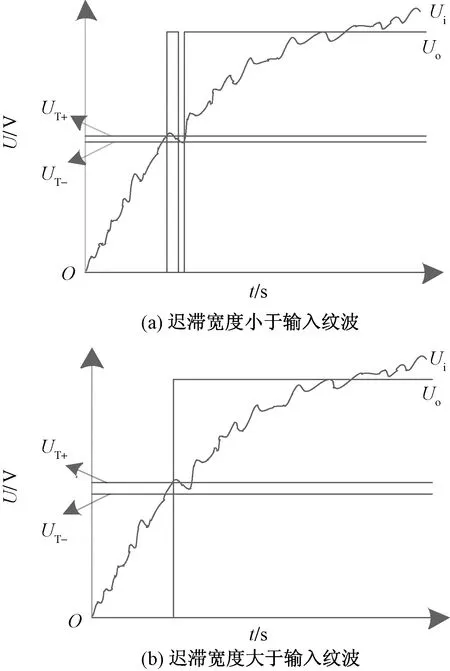

2.3.3 基准电压比较电路抗干扰能力分析

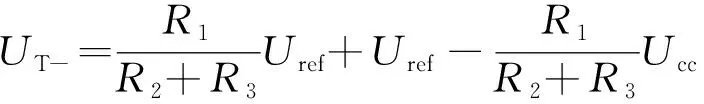

在输入电压Ui由0逐渐增大的过程中,如图7(a)所示,当迟滞宽度小于输入电压Ui的干扰纹波时,在阈值电压附近,干扰纹波会造成输出电压的抖动。结合分辨率的要求,适当放宽迟滞宽度,输入电压Ui达到正向阈值电压后,扰动纹波无法使Ui波动至反向阈值电压以下,由此输出电压保持高电平,消除抖动,如图7(b)所示。

图7 迟滞宽度对输出影响分析图Fig.7 The influence analysis chart of hysteresis width on output

由以上分析可知,ΔUT的存在可以消除由输入电压Ui中的干扰所带来的逻辑抖动,且ΔUT越大抗干扰能力越强,但同时ΔUT不易取值过大,以免影响高度电压模拟量的分辨率[6-9]。

2.4 光耦隔离电路

光耦隔离电路如图8所示。由比较器输出的高度开关量传输至光耦HSSR-7111(V1),经过光电隔离后输出。光耦输入负通过电阻R2连接至电源正,防止高度开关信号无效时,光耦输入负端处于悬空状态。由于比较器的灌电流能力不足,增加三极管V3,满足光耦对输入电流值的要求。

图8 光耦隔离电路原理图Fig.8 The schematic of the optocoupled isolation circuit

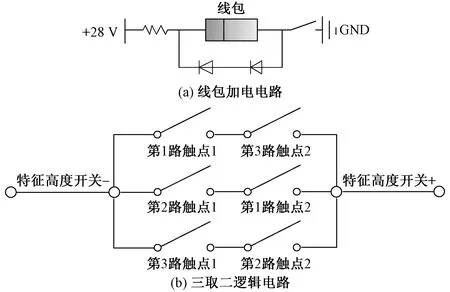

2.5 三取二开关电路

三取二开关电路由双触点继电器2JL0.5-1实现。静压信号处理器采用三模冗余结构,三路隔离后的高度开关分别控制各个支路中的继电器线包加断电,电路图如图9(a)所示。每个线包的状态决定相对应的2个触点的开关状态,3个继电器的6个触点通过组合排列构成三取二逻辑电路,电路原理图如图9(b)所示。

图9 三取二开关原理图Fig.9 The schematic of the three-in-two switch circuit

3 电路优化设计

3.1 电源电路优化设计

为了更好地抑制浪涌电流并减小供电电源的纹波,对电源电路进行优化设计,在输入端增加电阻R2(51 Ω),并在电源输出端增加电感L1、L2、L3,优化后的电路如图10所示。

图10 供电主路优化后设计Fig.10 The optimizing design of the power main road

3.2 基准电压比较电路优化设计

如图5所示,初始设计时,此电路中的电阻R1取值10 kΩ,R2取值1 MΩ,Ucc取值+12 V。由式(6)可知,初始设计ΔUT≈0.03 V。由于高度信号模拟量传输过程中的干扰,此迟滞宽度不能完全消除输入信号波动带来的抖动。优化设计时将电阻R2增大至2 MΩ,优化后ΔUT≈0.06 V。此迟滞宽度在满足分辨率要求的前提下,完全消除了开关抖动,提高了系统抗干扰能力。

4 三模冗余可靠性设计计算

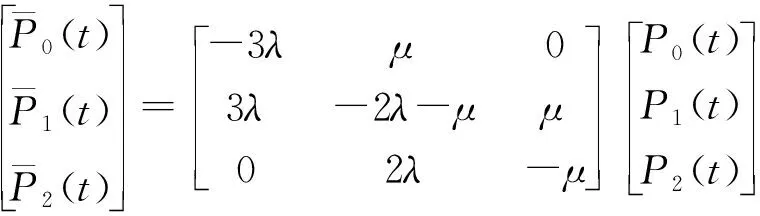

针对本产品选用的三模冗余结构,对此模型的可靠性进行分析,选用马尔可夫模型法进行建模和定量计算。首先对系统进行以下假设。

(1)系统在开始时可靠度均为1,失效率为λ,维修率为μ。

(2)系统开始工作时处于完好状态。

(3)组成该系统的设备、零件的寿命和失效后修复时间分布均服从指数分布。

则某一模块在时刻t处于失效状态,而在时刻t+Δt处于正常工作状态的概率为1-e-μΔt,将其按级数展开,对于很小的Δt可简化为1-e-μΔt≈μΔt;同理,则某模块在时刻t处于正常状态,而在时刻t+Δt处于正常故障状态的概率为1-e-λΔt,将其按级数展开,对于很小的Δt,可简化为1-e-λΔt≈λΔt。

状态参数定义如下:状态P0:系统完好。状态P1:3个模块中1个模块产生失效,被测试出并成功切除故障部件,此时系统成为双机比较系统。状态P2:2个模块都失效,均被定位到且成功切除,成为单机运行状态。状态P3:系统完全失效。

三模系统的马尔可夫状态转移图如图11所示。

图11 三模系统的马尔可夫状态转移图Fig.11 The Markov state transfer chart of the three-mode system

由图11以及对马尔可夫理论和建模、分析的知识,可以列出微分方程为

(7)

式(7)中:Pi(t)为系统中有i个模块失效的概率随时间变化的函数。

初始条件为零时刻三个模块都是正常的,即P0=[1 0 0]。

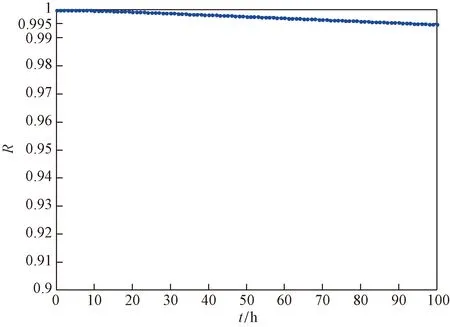

根据以上条件能计算任何系统可发生情况的转移概率,根据对状态定义可知,可靠度为R(t)=P0(t)+P1(t)。取单台计算机的失效率λ=0.001 h-1,模块的维修率u=0.1 h-1。通过MATLAB软件进行计算仿真后得到的可靠度R随时间t变化的曲线如图12所示。从图12中可以看出,80 h以内,三模冗余系统的可靠度高于0.995,静压信号处理器工作在飞船返回着陆阶段,工作时长小于1 h,三模冗余的结构设计使得系统具有较高的可靠性[10-13]。

图12 三模冗余系统可靠度变化曲线Fig.12 The reliability change curve of the three-mode system

5 验证试验

5.1 试验前准备

产品的功能和性能验证试验,需要采集三路继电器触点开关,即3个高度基本开关和由3个基本开关在三取二逻辑后所得到的表征特征高度的逻辑开关状态。采用电阻分压的原理分别将各个开关量转换成可以通过示波器测量的电信号,开关采集电路如图13所示。其中三路基本开关的采集选用每一路继电器第一对触点开关的常闭触点,测试点1连接常闭触点端。逻辑开关的采集电路是将分压电阻连接至逻辑开关+端,测试点2也是通过此点引出。

图13 开关采集电路原理图Fig.13 The schematic of switch acquisition circuit

逻辑开关是3个基本开关的常开触点三取二后得到。在特征高度到达前,继电器线包不加电,常闭触点闭合,测试点1为低电平,测试点2为高电平;特征高度到达后,继电器线包加电,常开触点闭合,测试点1为高电平,测试点2为低电平。

5.2 三路开关输出功能验证试验

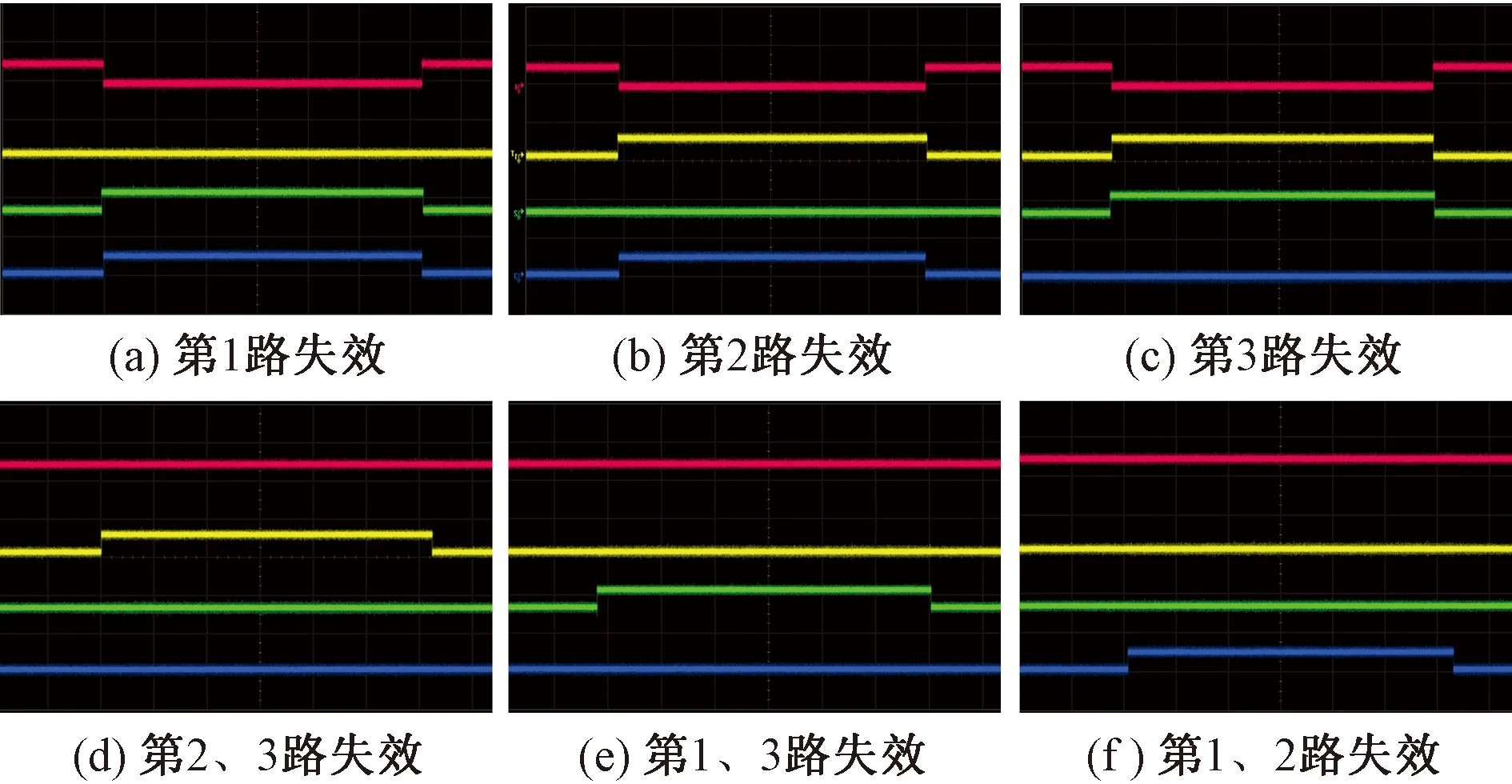

如图14所示,红色波形为0~5 V的模拟量输入信号,黄、绿、蓝波形分别为三路基本开关采集电路的测试点1电压信号,当输入模拟量信号超过特征高度的基准电压(约为+1.5 V)时,三路基本开关常闭触点断开,测试点1输出高电平。试验结果满足设计要求。

图14 三路开关功能验证采集图Fig.14 The function verification acquisition diagram for three switches

5.3 逻辑开关电路功能验证试验

三路基本开关与三取二后得到的表征特征高度的逻辑开关的状态如图15所示。由图15可知,在其中任意一路基本开关失效后,逻辑开关仍然能够正常工作,如果其中两路基本开关失效,则逻辑开关失效。黄、绿、蓝波形分别为三路基本开关采集电路的测试点1电压信号,红波形分别为逻辑开关采集电路的测试点2电压信号。

图15 三取二逻辑开关状态采集图Fig.15 The state acquisition diagram of two out of three logic switch

5.4 浪涌电流优化调试结果

对电源电路的浪涌电流进行调试,使用电流钳测量加电瞬间的浪涌电流,电流钳设置为100 mV/A,用示波器记录,优化前浪涌电流曲线(i-t)如图16(a)所示,优化后浪涌电流曲线如图16(b)所示。

图16 浪涌电流优化前后比对图Fig.16 The comparison of the surge current before and after optimization

如图16所示,优化前浪涌电流持续时间7.4 μs,最大浪涌电流为2.03 A;优化后浪涌电流持续时间7.6 μs,最大浪涌电流为1.43 A。可以得出,最大浪涌电流减小至初始值的71%,优化设计有效。

5.5 供电输出优化调试结果

供电电路输出的±12 V电源优化前波形如图17(a)所示,优化后波形如图17(b)所示。优化前±12 V电源的峰峰值为680 mV,优化后±12 V电源的峰峰值为280 mV,优化设计使电源纹波减小至初始值的41%。

图17 ±12 V电源优化设计比对图Fig.17 The comparison of the ±12V power before and after optimization

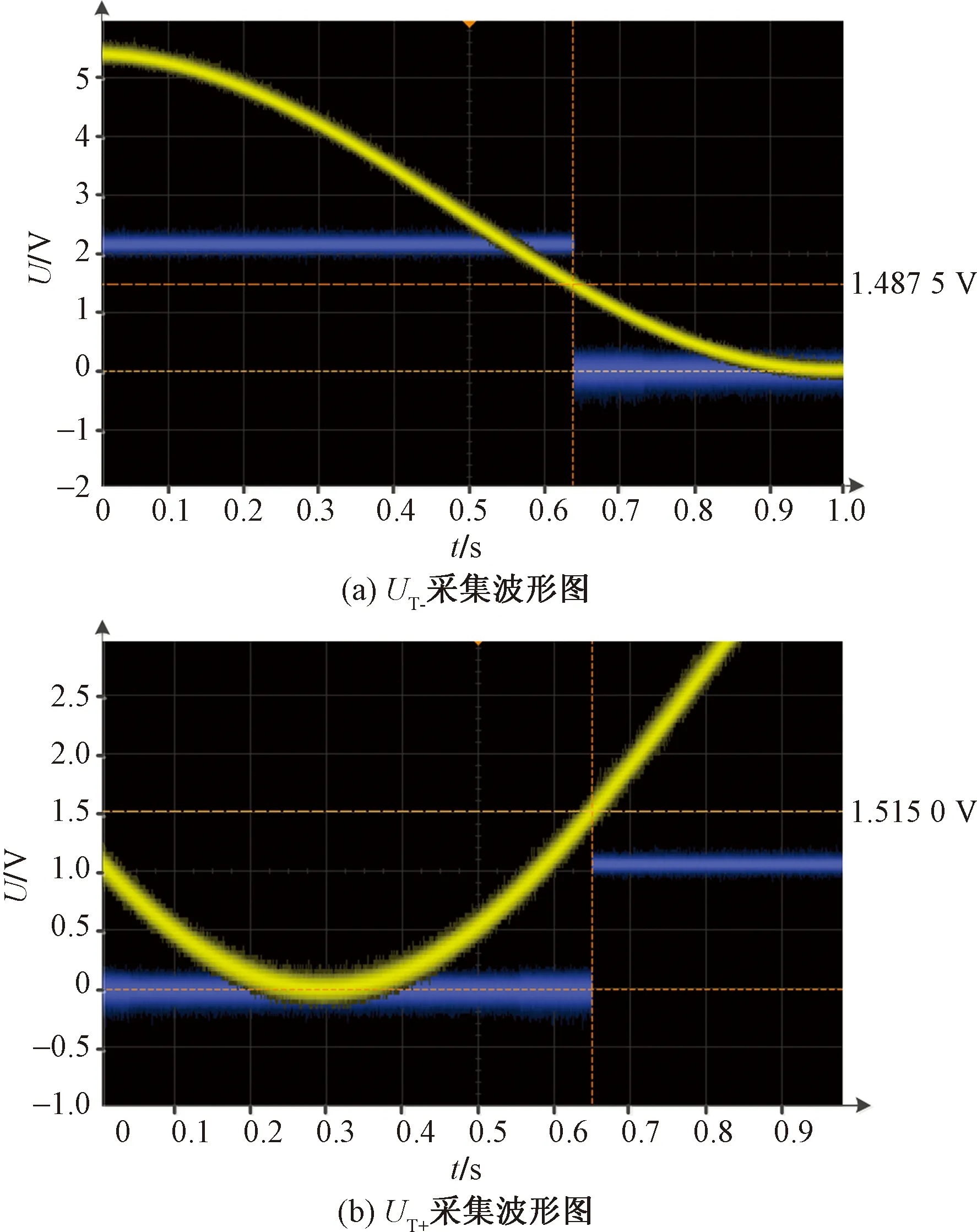

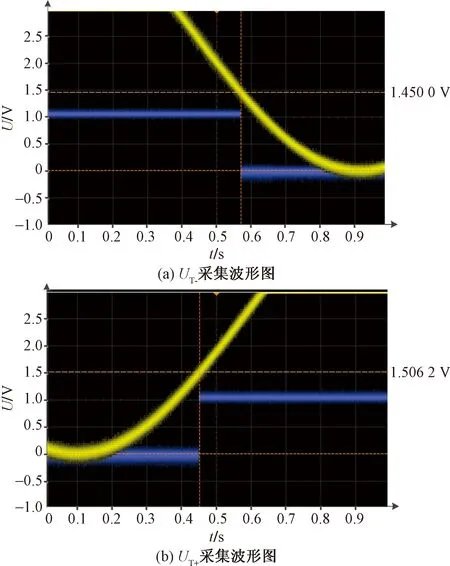

5.6 基准电压比较电路迟滞宽度调试结果

图18所示为迟滞宽度初始设计效果波形图, 图19所示为迟滞宽度优化后设计效果波形图。从图18中可知,迟滞宽度初始设计值ΔUT=1.515-1.487 5=0.027 5≈0.03 V。从图19中可知,迟滞宽度优化后设计值ΔUT=1.506 2-1.45=0.056 2≈0.06 V,与第3.2节计算结果一致。

图18 优化前门限值波形图Fig.18 The value of the threshold before optimization

图19 优化后门限值波形图Fig.19 The value of the threshold after optimization

6 结论

介绍了静压信号处理器电路的功能组成和设计实现,并针对浪涌电流、电源纹波和迟滞宽度,进行了电路的优化设计,同时通过MATLAB研究三模冗余结构的可靠性,通过试验和仿真结果可以得出以下结论:①当输入模拟量高于基准电压时,特征高度开关能够有效闭合、三取二逻辑输出正常,满足功能要求;②一次电源输入端母线串联限流电阻能够有效降低浪涌电流;③DC-DC二次电源输出前端串联电感,可以减小电源纹波;④通过电阻参数调整可以控制比较电路的迟滞宽度,基准电压比较电路的迟滞宽度理论计算过程有效;⑤同时针对三模冗余结构建模计算,仿真结果表明三模冗余结构具有较高的可靠性。