基于LVDS的高速数据回读系统设计

薛 栋,李 杰,张德彪,王 瀚

(1.中北大学 仪器与电子学院,山西 太原 030051;2.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原 030051)

0 引 言

常规弹药在改造过程中,需要进行多次靶场实弹实验以确保其正确性[1].弹载离线式采集存储系统在靶场测试过程中发挥着重要作用[2].在靶场实验后,需要将弹体内置采集系统中存储芯片的数据及时回读.由于弹体在膛内发射和飞行过程中,膛内过载、侵彻信号等部分参数的脉宽极窄,所以,为了最大程度地还原被测参数信号,其内置采集系统在设计时需要使用采样率和采样精度较高的模数转换器(ADC)以及存储速度更快、容量更大的存储芯片,如eMMC等,这同时也提高了对数据回读系统读取速度的要求[3-6].现场可编辑门阵列(FPGA)采用并行方式对外传输数据时,传输的有效距离短,在保证数据稳定性的情况下,传输速度低,约为1 MB/s,传输时间长,无法使用并行传输方式[7-8].

针对上述问题,系统利用低电压差分信号(LVDS)接口将并行数据转为串行数据进行传输,增加了传输速度和稳定性.大多数的FPGA与LVDS的设计均搭配数据串化器与解串器芯片,增加了设计复杂度以及系统体积[9].本文围绕低成本、小型化、高可靠性的原则,设计了利用FPGA内部资源实现LVDS接口的搭建和数据传输.通过将数据串化提高了传输速度和传输稳定性,完成了对Flash数据的快速读取,并使用FT600将数据上传至PC端.LVDS使用350 mV极低电压摆幅通过差分对完成时钟和数据的传输,最高传输速度可达1.923 Gb/s,具有较强的抗干扰能力,提高了数据传输的速率和可靠性[10].

1 总体方案设计

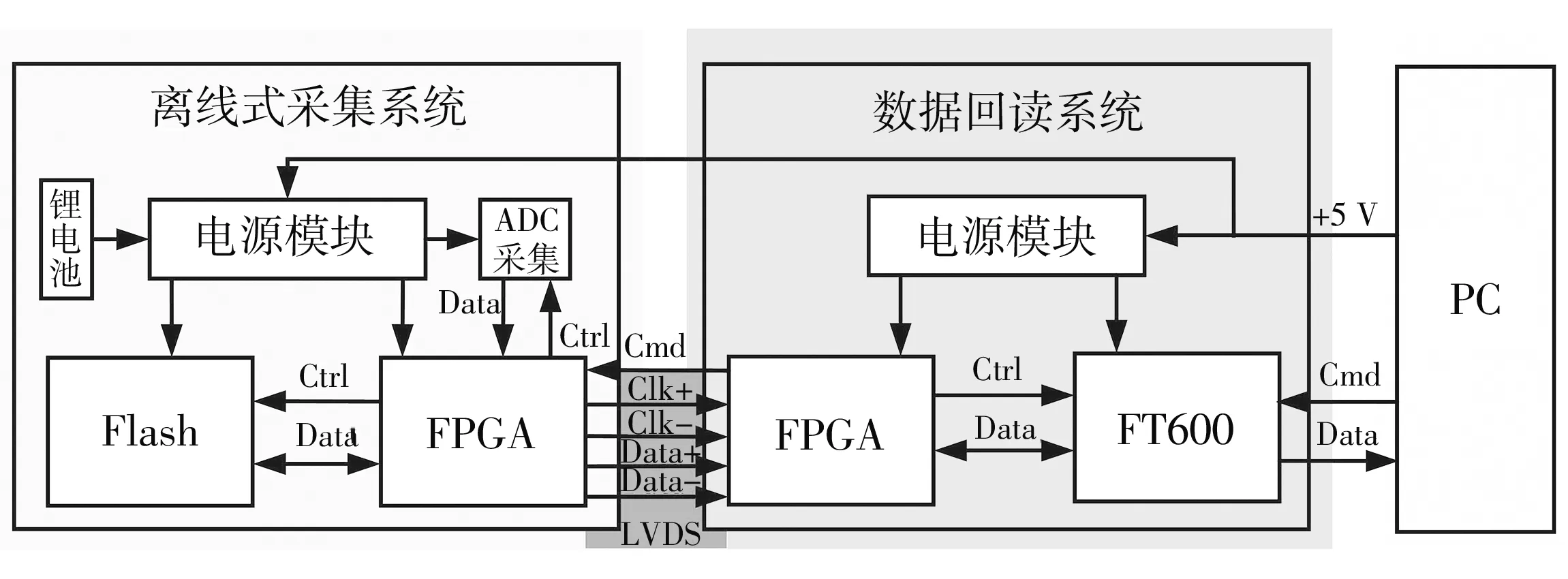

系统使用USB接口进行5 V供电,同时对离线式采集系统供电.系统主要由FPGA作为主控模块,通过控制FT600完成与PC端的指令和数据的交互,通过串口将指令发送给离线式采集系统.利用FPGA的内部资源搭建LVDS接口,将数据从离线式采集系统中的存储器中读出,并发送给FT600,再由FT600上传到PC端.图1 所示为系统总体设计原理图.

图1 系统总体原理图

2 硬件方案设计

系统硬件设计较少,主要由电源模块、FPGA控制模块以及FT600接口模块三部分组成.

2.1 电源模块

系统由PC通过USB口供电,同时为离线式采集系统供电,USB输出5 V电压,电流最高支持500 mA,在没有外接电源的情况下,可以满足系统的功耗.系统各模块供电电压为3.3 V和1.2 V,选择TPS70345作为电平转换芯片,该芯片可以输出高精度的3.3 V和1.2 V并具有快速的瞬态响应,两路输出分别可支持1 A和2 A的电流输出.在PCB布局过程中,电源芯片应尽量靠近被供电器件,以降低噪声并保证供电稳定性.

2.2 FPGA控制模块

该设计采用Xilinx的XC6SLX9芯片作为主控芯片,这款芯片可以兼容LVDS接口,在其BANK0和BANK2支持LVDS接口发送,所有BANK均支持LVDS接口的接收,满足设计需求.在进行LVDS接口差分对的布线时,应尽量保持对称和并行的原则.FPGA芯片使用SRAM工艺,掉电之后会丢失程序文件,所以需要搭配存储程序的配置芯片,FPGA在重复上电后能快速从配置芯片中读入程序文件.选择XCF04S作为配置芯片,该芯片容量为4 Mbit,且由3.3 V供电,满足要求.FPGA的主要作用为控制FT600,使其可以与PC端进行正常的数据交互,并解析FT600接收到的从PC端发出的指令,利用串口对离线式采集系统发出相应的指令,通过LVDS接口接收数据,从而达到控制离线式采集系统中Flash的目的.

2.3 FT600接口模块

USB3.0接口为目前最具性价比的接口之一,其支持多种数据传输方式,最高速度可达 45 Gb/s.选用FTDI公司的FT600芯片,其支持超高速USB 3.0,支持控制传输(Control)、块传输(Bulk)及中断传输(Interrupt)多种传输模式[11].本设计上传的数据量较大,对数据传输的准确度要求较高,且无实时性要求,所以选择块传输模式.FT600支持两种不同的专用同步和总线协议:多通道FIFO总线协议和245同步FIFO总线协议,内部自带时钟生成和上电复位电路.该芯片可以满足系统在数据上传时的速度需求,并且FTDI公司提供该芯片的驱动固件,在完成硬件设计后,进行简单的固件配置即可使用.

3 逻辑设计

逻辑设计主要包括LVDS接口、数据上传和上位机设计.上位机向回读系统发送指令,回读系统转发给离线式采集系统,通过检测指令,离线式采集系统会进行相应的数据发送、数据擦除操作.离线式采集系统通过LVDS发送数据后,回读系统将对数据进行解串,将其转换为8 bit的并行数据并存入4 KB的异步FIFO中,FT600控制模块将数据从FIFO中读出并发送给上位机.

3.1 LVDS接口设计

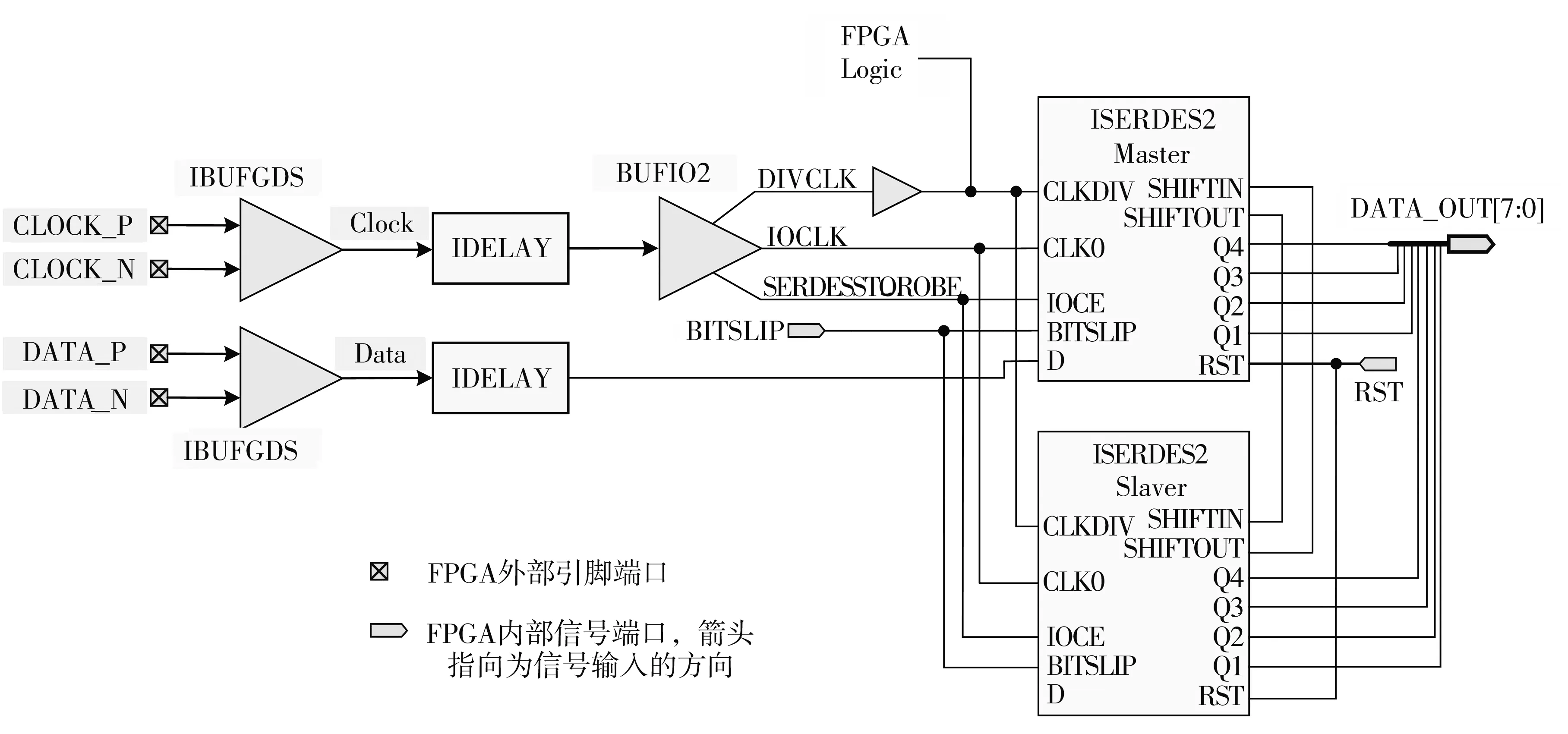

LVDS接口在传输数据过程中,需要对接收到的时钟进行降频并对串行数据进行解串.设计中发送端的FPGA并行数据时钟为100 MHz,单个时钟传输8 bit,所以,LVDS接口的串行传输时钟为800 MHz.将降频后的串行时钟用作FPGA的内部逻辑时钟.LVDS接口主要包括全局差分转单端缓冲器(IBUFGDS)、输入延迟控制器(IDELAY)、时钟降频缓冲器(BUFIO2)和解串器(ISERDES2)4个部分,图2 所示为LVDS接口结构图.

图2 LVDS接口结构图

由于LVDS传输线为差分时钟对和差分数据对,首先需要利用IBUFGDS将输入的差分时钟和差分数据转换为单端时钟和单端数据.单端时钟和数据需要经过IDELAY,由于IDELAY中有鉴相器(Phase Detector),它可以动态调节时钟的相位,使时钟的上升沿与数据中心对齐,确保FPGA采样数据的正确.单端时钟经过BUFIO2后,可以将高速的串行数据时钟降频为低速的并行数据时钟,其中DIVCLK为降频8倍之后的时钟,IOCLK为输入的原始高速串行时钟,SERDESSTROBE为当DIVCLK上升沿时BUFIO2产生的一个脉冲信号,用于指示ISERDES2对串行数据的操作.DIVCLK为并行数据的输出时钟,为了保证数据的输出可以与其他模块同步,需要将其作为FPGA的部分模块的逻辑时钟.单个ISERDES2仅仅可以将串行数据解串为4 bit的并行数据,因此,需要将两个ISERDES2进行级联以得到最后的8 bit的并行数据,将主机的SHIFTIN连接到从机的SHIFTOUT,从机的SHIFTIN连接到主机的SHIFTOUT完成级联.

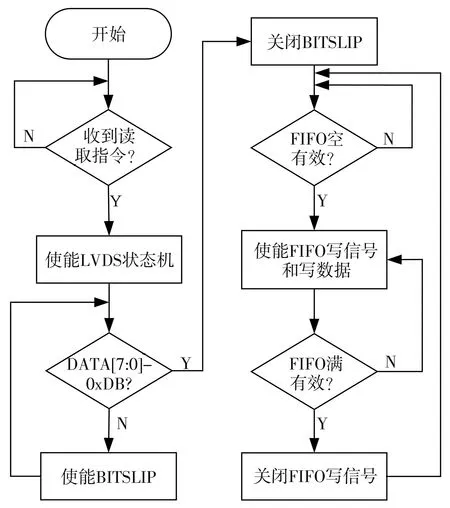

在LVDS传输数据过程中没有任何标志,例如起始标志、停止标志等,所以,在传输过程中首先需要将LVDS的接收端进行数据同步.在接收到PC端发出的读取指令后,LVDS发送端会先发送200次的固定数据0xDB,以保证接收端可以将数据对齐.BITSLIP使能可以使ISERDES2对数据进行移位操作,在接收到读取指令后,LVDS接收端每次都会将接收到的数据与0xDB作对比,通过对比结果来判断是否需要继续进行移位操作,直到数据符合为止.

图3 所示为LVDS接收数据流程图,设计使用Xilinx 公司的IP 核创建FIFO,根据需求来选择组成FIFO的存储器类型、读写是否同步、读写位宽、深度、空满状态标志以及可编程状态标志.在设计中选择了异步FIFO,即读写时钟独立,并设置为首字预现型(First-Word Fall-Through)的数据读取方式,即总是将当前FIFO中的第一个数外挂在数据总线上,这种方式可以实现读信号与数据的同步以及对FIFO的低延时数据访问.

图3 LVDS接收数据流程图

3.2 数据上传

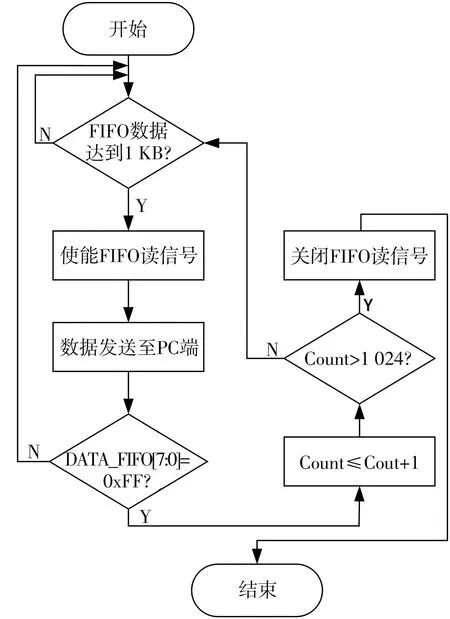

离线式采集系统FPGA识别到读取指令后,将数据从Flash中读出并通过LVDS接口发送,回读系统接收到数据后缓存到内置的异步FIFO中,通过检测FIFO的空满标志位判断是否读取FIFO中的数据.由于Flash的初始值为0xFF,通过判断读出之后的数据是否有连续1 KB的0xFF来判定是否已经将Flash中的数据全部读取.再将数据通过FT600转为串行数据发送给PC端,数据上传流程图如图4 所示.

图4 数据上传流程图

3.3 位机设计

回读系统的FPGA通过FT600与上位机完成通信,在接收到指令后,通过串口转发给离线式采集系统,通过识别上位机发出的指令,进而执行读数、擦除、中止等操作.系统与上位机的通信指令协议如下所示.

读取指令:EB&&90&&A5;

擦除指令:EB&&90&&B6;

中断读取指令:EB&&90&&C7.

在靶场实验中,离线式采集系统通常会记录发射前和落地后静止一段时间的数据,由于采样率高,导致测试过程的数据量很大,若将数据写入一个.dat文件,在后续的数据处理中会造成很大的麻烦,因此,需要将数据文件进行分解,接收到256 MB数据之后就新建一个数据文件.在测试结束后,可以根据测试的时间点来确定被测参数的数据文件范围.

4 系统验证

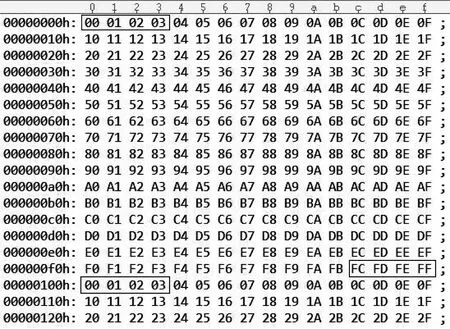

测试过程为将8 bit宽度的循环自增数据先存入采集系统的Flash中,使用Visual Studio编写上位机对回读系统发送指令,然后进行数据回读,通过对0x00~0xFF的数据匹配查找,发现无丢帧、误码现象.图5 所示为回读数据显示图.

图5 回读数据显示图

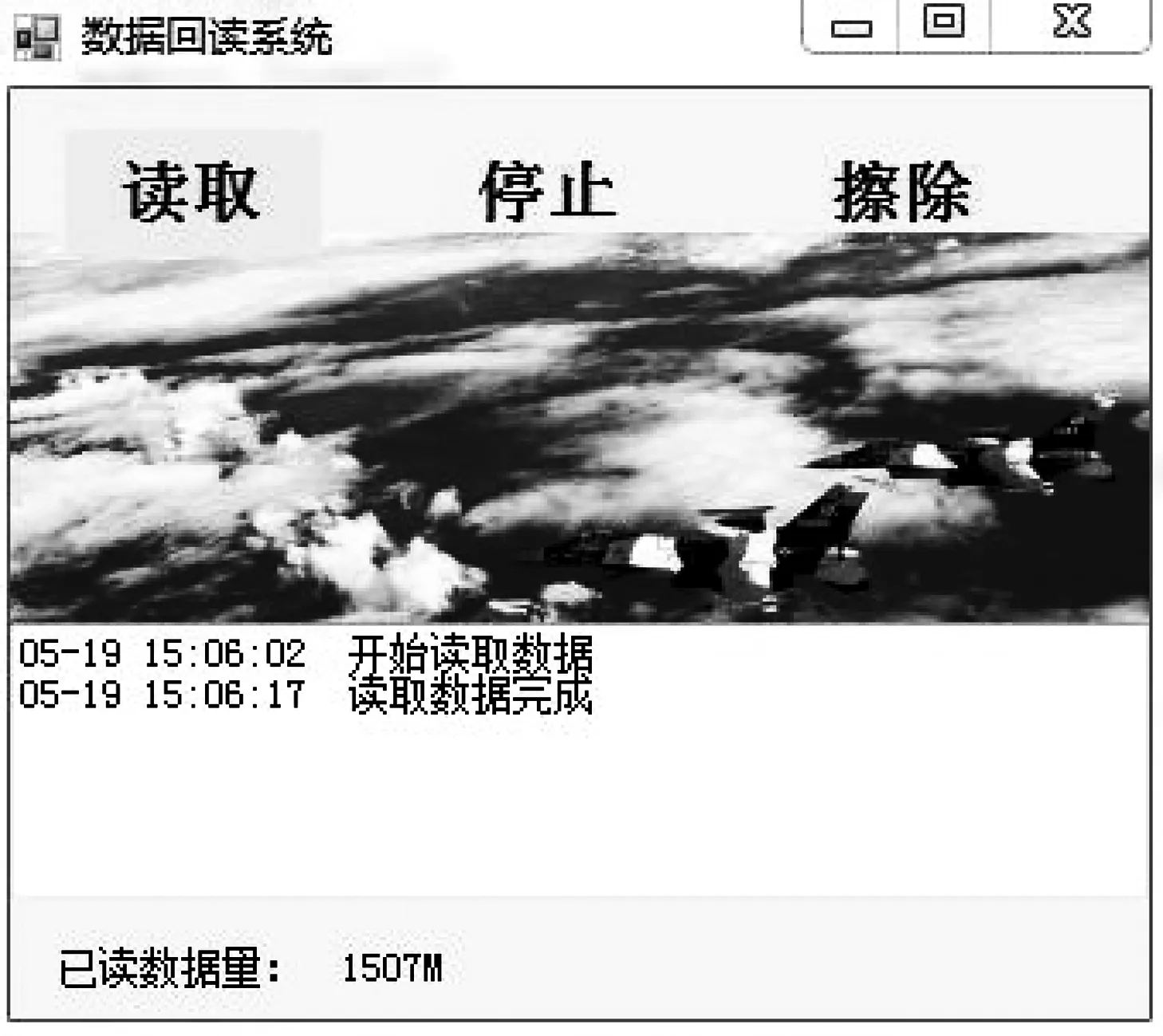

由于无法直接测试LVDS接口的速度,一般的测试方法为根据上位机的回读数据量以及回读时间计算系统的回读速度.15 s内回读的数据量为1 507 MB,回读速度达到100.46 MB/s.图6 所示为上位机读取界面图.

图6 上位机界面图

5 结 论

本文针对因采集过窄脉宽信号导致存储量太大及现有回读装置回读速度慢的问题,设计了基于LVDS的高速数据回读系统,给出了详细的系统总体设计方案.系统利用FPGA内部资源搭建LVDS接口用于数据传输,通过Visual Studio设计上位机,完成指令和数据的交互,测试验证回读数据量为1 507 MB,回读时间为15 s,回读速度为100 MB/s,实现了高速及时回读数据的设计要求.