QPSK调制解调器的设计与实现

公安部第一研究所 洪向宇

本文基于可编程逻辑阵列设计实现QPSK调制解调器,对QPSK调制解调各模块算法进行了研究,包括信道编译码、成型滤波、载波同步等,并在此基础上烧写进FPGA中进行仿真,利用信号分析仪分析调制器的性能。

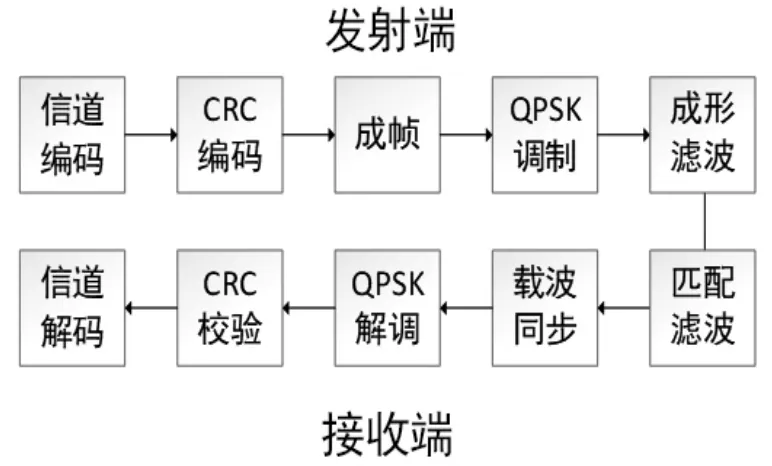

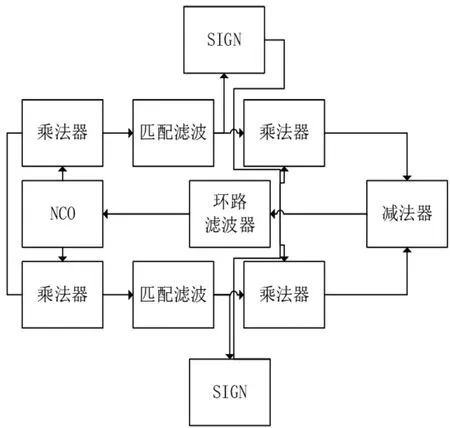

图1 QPSK调制解调结构框图

随着科学技术的发展,通信系统已成为各个领域的技术基础,由于数字传输能够提供数据处理种类的灵活性,因此数字通信系统正受到越来越多的重视。

数字调制技术是数字传输的基础,通过载波调制使数字信号在信道中传输,载波的表达式有三个变量,因此数字信号调制技术分为幅度键控(ASK)、频移键控(FSK)和相移键控(PSK)三种方式。其中QPSK是目前最常用的数字信号调制方式之一,QPSK调制方式的优点为频谱利用率高、抗干扰性强,并且能够很好的权衡频带利用率和接收信噪比的折中要求。本文在FPGA平台上设计实现QPSK调制解调器。

1 QPSK调制解调器的设计

本文设计的QPSK调制解调系统由10个部分组成。信道编解码部分采用Turbo交织器的设计;校验部分CRC校验算法设计;QPSK调制解调部分;成形滤波模块和匹配滤波模块采用根升余弦滤波器实现;载波同步采用改进的科斯塔斯环算法实现。结构框图如图1所示。

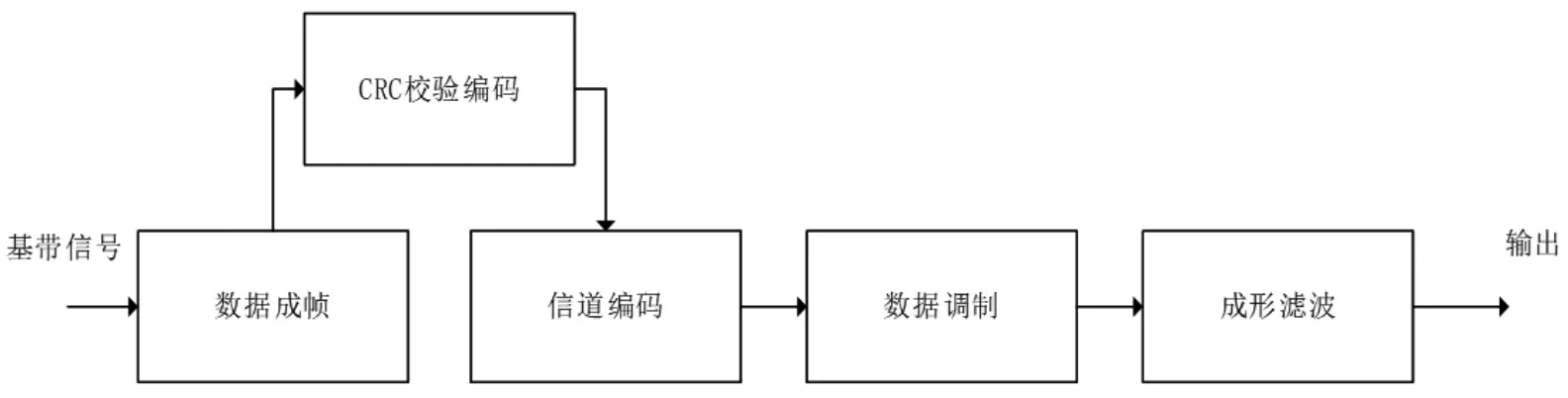

QPSK调制部分如图2所示,QPSK调制器包括信道编码器、CRC校验、数据成帧、数据调制、成型滤波等模块。

图2 QPSK调制部分结构框图

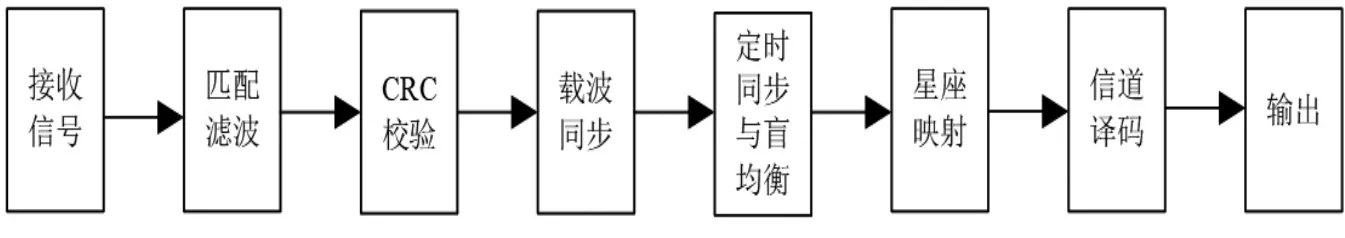

图3 QPSK解调部分结构框图

图4 信道编码部分结构框图

QPSK解调部分如图3所示,QPSK解调器包括匹配滤波、CRC校验、载波同步、定时同步与盲均衡、星座映射、信道译码等模块。

本文使用信道编译码算法为利用Turbo码的信道编译码算法,利用卷积、交织、删余、复用模块实现Turbo码的编码,其中基带信道编码器采用Turbo码中的并行级联编卷积算法结构。信道译码的结构图如图4所示。根据香农信道编码定理,译码过程采用最佳的最大似然译码方案。因此信道译码过程使用最大似然译码算法,译码数据进入解码器后,经过数据缓冲器对数据进行缓存操作,并将数据输入解交织器进行解交织操作,从而实现译码的迭代运算。如图5所示。

图5 信道译码部分结构框图

图6 成型滤波结构框图

图7 载波同步系统框图

本文使用分布式算法实现成形滤波器,分布式算法在FPGA实现中不需要乘法器,而是系数查找表和移位寄存器实现减小了FPGA的逻辑资源。算法结构图如图6所示。

本文采用改进型的科斯塔斯环设计载波同步,其算法框图如7图所示。

本文使用m序列信号发生器实现CRC校验。由于算法结构简单,因此利用移位寄存器的m序列信号发生器就可实现的CRC校验。

图8 QPSK的星座图及眼图

2 仿真与验证

将QPSK算法烧写进FPGA中,利用信号分析仪测设系统的星座图及眼图,结果如图8所示,图中可以看到QPSK调制的星座点收敛,系统的误差向量幅度仅为2%,说明调制设计中的幅度误差和相位误差极小,验证了调制系统设计的性能。

结语:本文的设计基于FPGA的QPSK调制解调器。主要研究了信道编解码算法,成型滤波与匹配滤波算法,CRC校验算法,载波同步算法等。最终将算法烧写进FPGA中进行仿真验证。