MCMM技术在SOC FD_Z801模块中的运用

蔡沅坤,王仁平,孙恒

(福州大学物理与信息工程学院,福建 福州 350108)

1 引言

随着集成电路产业的不断发展,特征尺寸不断缩小,到了深亚微米工艺下,芯片功能受到工艺、电压、温度的影响更为严重,需要使用更多的工艺角来保证所设计的芯片在不同极端情况下能够稳定工作。同时,随着芯片测试需求的增加和芯片功能的增强,芯片工作模式也在不断增加。设计者除了保证芯片在不同的工艺角下时序收敛,也需要保证在各种工作模式下正常工作。对此,工艺角和芯片工作模式的增加使得芯片在时序收敛方面遭受较大的挑战。所谓工艺角是指在保证芯片功能正确的前提下所表现出来的参数波动的极端情况[1-2]。在以往设计过程中习惯性采用传统的方法实现时序收敛,但在这过程中往往需要大量的人工操作进行大工作量的反复迭代并且分析消除模式之间的影响,容易产生时序难以收敛的情况。除此以外,可测试性设计(Design for Test,DFT)技术也可以降低芯片功耗成本和测试成本,在DFT中的扫描链技术(Scan Chain)可以在短时间内检查芯片内部各寄存器的好坏,早一步将因工艺缺陷和尘埃附着的损坏芯片在裸片阶段检测出来,可以防止损坏的芯片流入下一阶段的设计中,从而避免造成更大损坏[3]。目前,很多知名电子设计自动化EDA(Electronic Design Automation)公司已相继发布了系统层面的电路设计软件,被行业广泛应用[4]。本文采用了Synopsis公司IC Compiler软件的MCMM设计技术,以FD_Z801芯片设计为例,对比传统时序收敛方法,证明了MCMM技术有效实现了时序快速收敛,缩短了设计周期。

2 传统时序收敛实现方法

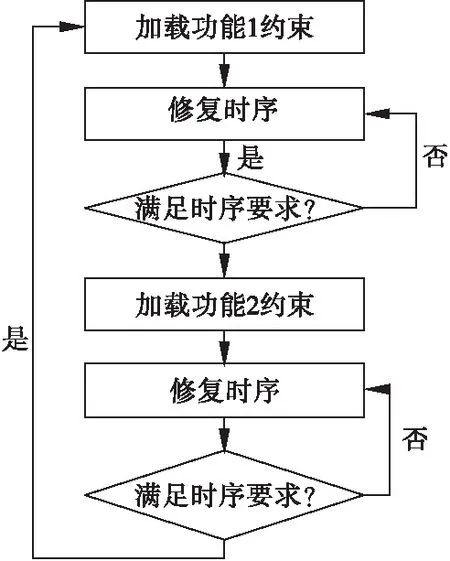

时序分析的目的是检查时序路径延时是否符合时序约束要求,根据到达时间(arrival time)、要求时间(required time)和违例值(slack)判断是否存在时序违约[6]。由于早期工具的限制,早期的时序分析方式是利用一套单元库,在单一的情况下进行时序分析。在逻辑综合、自动布局布线过程中选择最差的工艺角。在最后时序signoff时更换成其他不同的库,反复分析时序这一流程,如图1所示。这一情况只能考虑到一种时序情况进行逻辑综合和布局布线,对此,在设计过程中需要预留足够的裕量(margin)从而保证在最后时序signoff时能够在其他工艺角下满足时序。

对此EDA工具提供对建立时间和保持时间的时序分析分别设定不同的两套单元库。使用最差状况(延迟最大)的库处理建立时间,使用最佳状况(延迟最小)的库处理保持时间,该方法被称为最佳-最差(best-case worst-case,BC-WC)分析。该方法的工作模式是:建立时间对时钟频率以及最长路径总延时敏感,所以希望数据路径延迟越小越好,对此采用最大延迟情况去分析,得到的结果是最悲观的,如果该结果能够满足,则其他情况也能同时被满足;同时保持时间希望数据路径延迟越大越好,对此采用最小延迟情况去分析,以此覆盖所有情况[5]。

该方法存在的问题:保持时间希望数据路径来得越晚越好,但在最佳状况下的保持时间裕量可能比最差状况下的保持时间裕量大。这说明使用最佳状况检查,保持时间符合时序要求,但在使用最差状况进行检查时,保持时间就不符合时序要求,这种情况存在多数复杂的实际情况中。所以传统的BC-WC方法并不能保证覆盖静态时序分析结果的最差状况[7]。

从图1流程图不难看出,该方法存在的问题是EDA工具无法同时覆盖所有模式下的时序问题,只能通过串行的方式对各个模式下的时序进行修复,同时需要保证修复过程中各个模式之间没有影响。对此需要设计者反复切换到各个模式检查时序是否满足,只要对其中某一个模式进行时序修复操作,其他模式也需要进行检查。这无疑增加了各个模式之间切换迭代的次数和人工手动ECO(Engineering Change Order)的时间成本。工作量会随着芯片工艺角和模式增多而增大[8]。

图1 传统时序收敛方法

3 MCMM设计流程

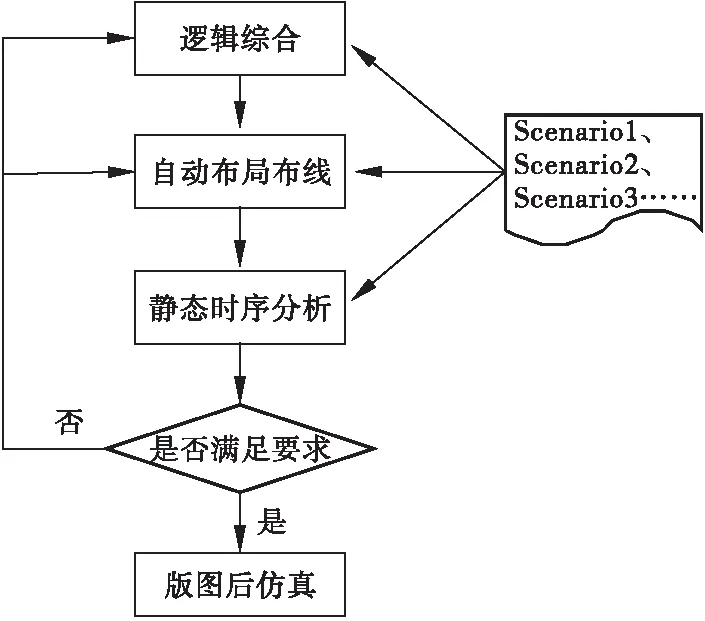

传统的静态时序分析,属于串行的,需要逐个分析,且每种工作模式都要分析。因此,需要耗费大量的时间。为了解决传统设计流程带来的不便,MCMM旨在解决这一问题。其内容主要是将工作模式和工艺角相互组合,corner分析由工艺参数(process),电源电压(voltage)和温度(temperature)组成,从而创建多个场景(Scenario),接着选择需要激活的场景让EDA工具对其进行优化[10]。在这过程中同一条时序违例的路径会在不同的场景中出现,评估这条时序为例的路径在不同场景中的时序裕量大小,例如一条路径在场景1中的裕量为-1,在场景2中的裕量为-0.2,可以认为该路径在场景1中的权重更高,选择在场景1中进行修复[9]。流程如图2所示。

图2 MCMM设计流程

传统设计流程可以理解为每次对一个场景进行时序分析和操作,但无法分析其他场景的状况,同时也无法确定当前要修复的时序路径是否在其他场景下也有影响。但倘若对所有场景进行分析评估以后便可以确定时序修复的最佳方案,并依照该方案进行时序修复,一方面提高了时序修复的效率,另一方面也保证不对其他场景的时序产生其他影响。

综上所述,与传统的时序收敛方法相比,MCMM设计通过在静态时序分析的过程中将不同的工作模式和工艺角相互组合,创建场景的方式来减少设计迭代,由“串行”变为“并行”,大大节省了人工手动ECO的工作量,提高了工作效率和减少了设计成本[11]。

4 FD_Z801模块的MCMM技术设计应用

4.1 场景定义

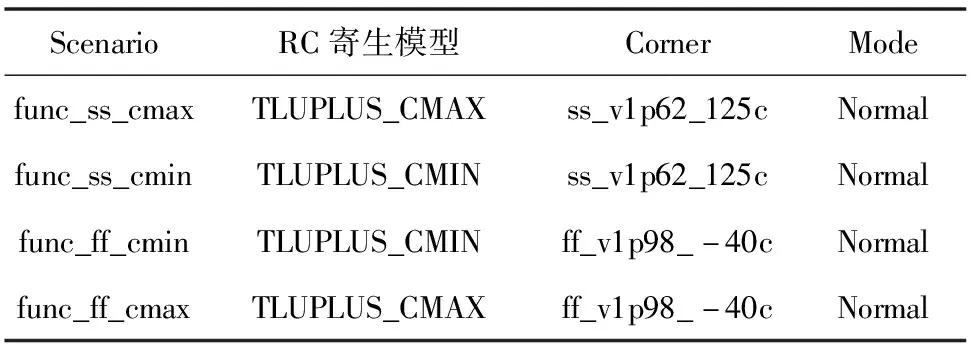

场景就是工艺角和工作模式相互组合[12]。虽然EDA工具能够对输入的多个模式进行优化,但工作模式的增加会导致计算机运算时间的增加,所以需要选出有针对性的模式。经过综合考虑选择如表1的4个场景。

表1 工艺角和模式的选择

定义场景的脚本如下:

建立名叫func_ss_cmax的Scenario:

create_scenario func_ss_cmax

读入该模式的时序约束文件:

source FD_Z801_core.sdc

场景Scenario是由工艺角Corner和工作模式Mode组合而成的,其中Corner分析由工艺参数(process),电源电压(voltage)和温度(temperature)组成,下面指定时序分析类型和对应Corner下的lib库:

set_operating_conditions-analysis_type on_chip_variation-max library scc018ug_uhd_rvt_ss_v1p62_125c_basic-max ss_v1p62_125c

同时设定相应corner的RC寄生模型:

set_tlu_plus_files-max_tluplus $TLUPLUS_CMAX-min_tluplus $TLUPLUS_CMAX-tech2itf_map $TLUPLUS_MAP

同理,根据如上脚本依次建立func_ss_cmax,func_ss_cmin,func_ff_cmin,func_ff_cmax场景。

4.2 实现时序修复和收敛

在完成时钟树综合以后,下一步需要对保持时间进行时序修复。考虑到4个场景都有保持时间违约,需要对其进行修复。对此应当同时激活func_ss_cmax,func_ss_cmin,func_ff_cmin,func_ff_cmax这4个关键scenario进行时序收敛,操作脚本具体如下:

激活关键的场景Scenario:

set_active_scenarios {func_ss_cmax func_ss_cmin func_ff_cmin func_ff_cmax}

对已经激活的场景Scenario依次设置每个场景的时序裕量:

foreach scenario[all_active_scenarios]{

current_scenario $scenario

set_clock_uncertainty-setup 0.2[all_clocks]

set_clock_uncertainty-hold 0.2[all_clocks]

set_max_transition 0.8[current_design]

set_max_transition-clock_path 0.7[all_clocks]

set_max_fanout 64[current_design]

set_app_var timing_remove_clock_reconvergence_pessimism true

set_scenario_options-setup true-hold true

set_propagated_clock[all_clocks]

set_fix_hold[all_clocks]

remove_ideal_network-all

group_path-name INPUTS-from[all_inputs]

group_path-name OUTPUTS-to[all_outputs]

group_path-name COMBO-from[all_inputs]-to[all_outputs]

}

设置完各类场景的时序裕量后更新clock延迟:

update_clock_latency

开始进行时序修复:

clock_opt-fix_hold_all_clocks

经过一轮时序修复后,再进行增量修复:

psynopt

4.3 时序修复结果

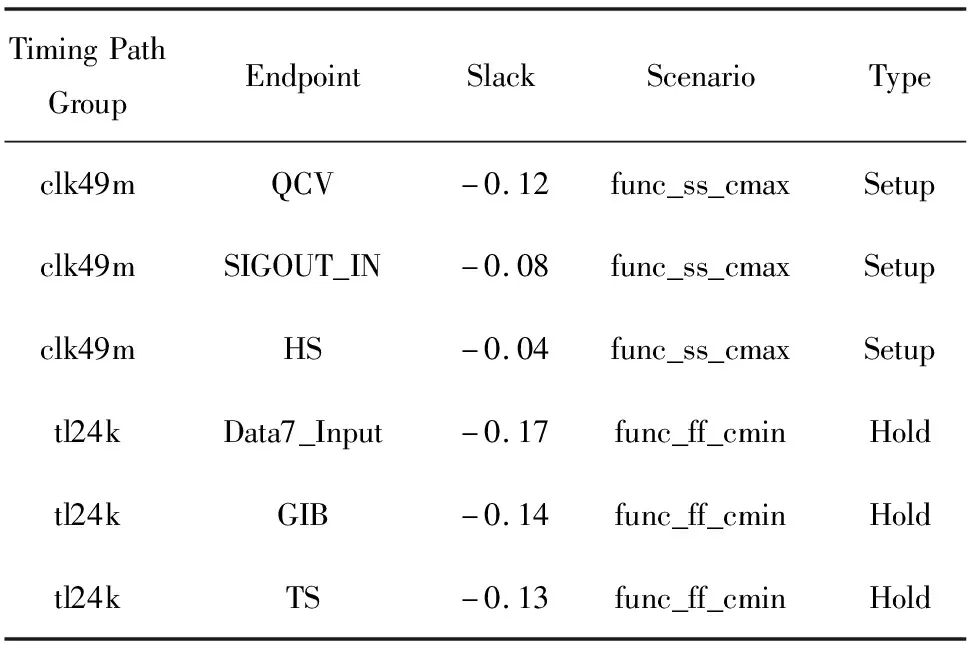

经过上述操作,4个关键场景时序路径完成优化,当前时序违约情况如表2所示。

表2 MCMM第1次优化结果

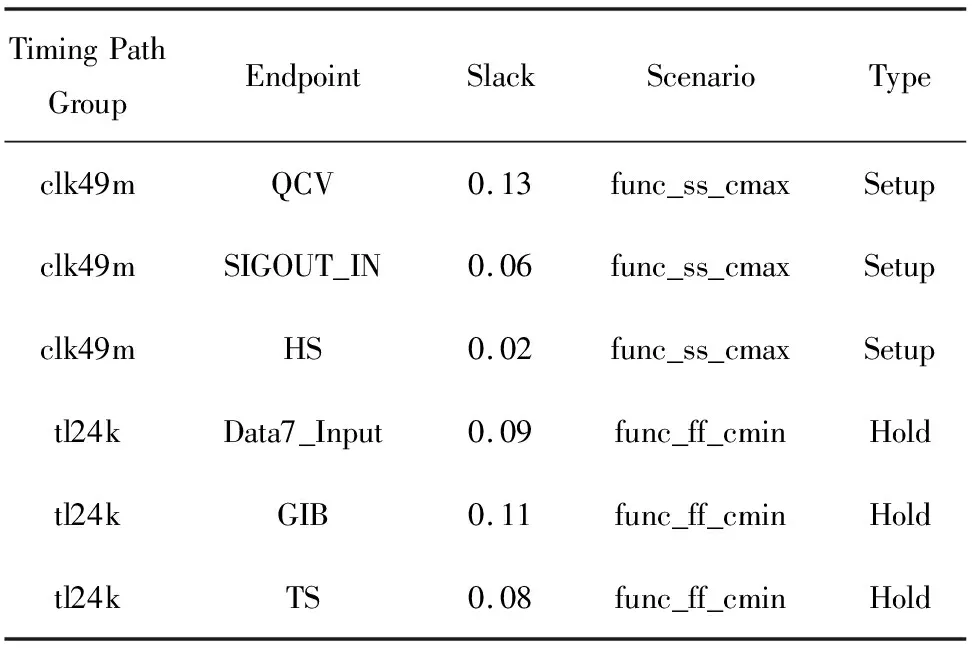

结果显示,大部分时序已经满足要求,func_ss_cmax的场景有建立时间上的时序的违例,func_ff_cmin场景有保持时间上的时序违例,只需要激活该场景然后迭代运行一次指令“psynopt”即可修复,结果如表3所示。

表3 MCMM第2次优化结果

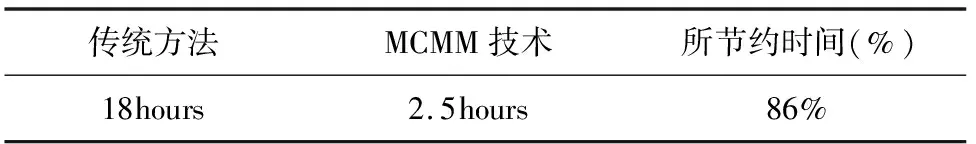

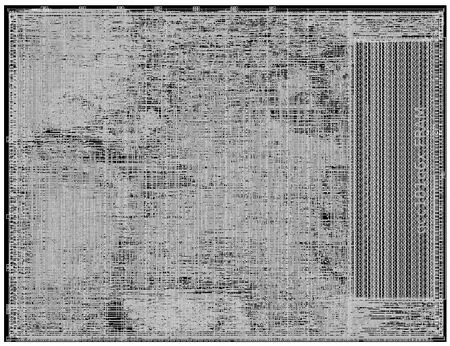

传统方式修复时序,由于不同模式和工艺角之间数量较多,需要人工来回切换模式,并且模式之间时序相互影响,导致在时序收敛方面所需要的时间多于MCMM技术所需要的时间,在本次设计中尝试利用传统方法进行时序收敛。在这一过程中因为工作模式数量多,从而导致在模式间来回切换,切换次数多于20次,由于不同模式之间的时序干扰较为严重,所以人工ECO的工作量很大,时序收敛所需要的时间远远高于MCMM技术所需要的时间,具体结果如表3所示。对此可以看出MCMM技术在时序收敛方面优势明显。MCMM流程完成后的版图如图3所示。

表3 传统方法与MCMM技术所用时间对比

图3 最终版图

5 结论

本文介绍了MCMM技术在时序收敛方面的应用,并利用FD_Z801设计实例阐述实现过程,结果表明该技术能够为版图设计工程师节省设计时间,其实际应用价值可观。CTS(Clock Tree Synthesis)阶段需要平衡时钟网络的负载,减小时钟偏差,保持时钟信号的完整性,从而建立一个合理的时钟网络[13]。所以本次设计过程中将MCMM技术从CTS阶段开始应用,并且达到芯片时序收敛的结果。在今后遇到更为复杂的设计时可以将MCMM技术应用到逻辑综合阶段和布局布线阶段,保证芯片能够一次性满足在不同工作模式和不同工艺角下的时序要求,同时避免在时序验证时反复回到布局布线阶段进行时序修复,达到缩短设计周期和节约面积的效果,从而节约设计成本。同时现阶段已有很多优秀的EDA工具,可以从更多不同的角度研究MCMM优化的设计流程以及方法。对于新的工艺和设计流程还有许多值得深入研究讨论的地方。