基于片外Flash 编程加载的无线充电SoC 系统的设计与实现*

徐圣楠 ,傅桂娥 ,2,王 维 ,张一晋

(1.南京理工大学 电子工程与光电技术学院,江苏 南京210094;2.南京睿赫电子有限公司,江苏 南京210018;3.中国船舶集团有限公司第八研究院,江苏 南京211100)

0 引言

随着生活质量的提高,人们对电子产品的便捷性和通用性要求也越来越高。 与传统接触式充电模式相比,无线充电主要有两大优点[1]:一是让电器与电源之间无任何电气连接,能够减少传统充电方式所带来的安全隐患,并且大大提高用电设备的通用性、安全性和灵活性;二是使得充电系统向袖珍型、节能环保的方向发展,便于用户随身携带使用[2]。

集成化和小型化是无线充电设备的主要发展方向。集成电路技术采用一定的工艺将更多的功能集成到单一的芯片上,给更小型化设备的实现提供了可能。 片上系统(System on Chip,SoC)集成微处理器、无线通信模块、常用接口等,能够很好地满足各种微型智能设备的设计需求。进一步,使用基于CPU 控制的SoC 架构[3-4]能够有效地增强无线充电设备的可更改性和可维护性。

目前无线充电芯片主流品牌主要包括IDT、NXP、Nuvoton 和ST 等。IDT 公司的P9242 无线充电芯片[5]采用一次性可编程(One Time Programmable,OTP)存储器件,相较于将全部程序存储于片内ROM 的方式,提供了一次修改芯片程序的机会,同时制造成本也低于片内集成Flash的方式。 但是,P9242 将主程序从OTP 拷贝到静态随机存取存储器(Static Random-Access Memory,SRAM)中运行,因而对于较大的程序需要开辟较大的SRAM, 增加了芯片制造成本。 NXP 的WCT101 无线充电芯片[6]采用片内集成Flash 存储主程序,其工艺难度大,成本相较于OTP 更高。文献[7]和文献[8]分别介绍了两种基于单片机(Microcontroller Unit,MCU)配合外围电路的无线充电方案。与集成化芯片的方案相比,这两种方案的物料成本是最高的。

针对以上缺陷,本文在现有无线充电系统[9-10]的基础上, 设计一种基于片外Flash 编程加载的无线充电SoC系统,能够有效降低芯片设计成本。 实验验证了该系统在无线充电的处理速度方面能够满足协议要求,达到与高成本芯片同等的充电效果。

1 系统架构分析与设计

1.1 系统取指方式的选择

取指方式影响CPU 读取指令的速度,对于系统运行速度至关重要。 如图1 所示,常见的SoC 芯片主要有三种获取指令的方式:基于SRAM 的取指方式、基于片内存储介质的取指方式和基于片外存储介质的取指方式。

如图1 (a)所示,基于SRAM 的取指方式将代码存储在片外介质中,运行时以片内BOOTROM 启动,使得主程序指令在此引导下从片外介质拷贝到SRAM 中,并在SRAM 中运行。 此方式虽然具有较佳性能,但SRAM 集成度低,芯片面积大且功耗较大,制造成本高。

如图1 (b)所示,基于片内存储介质的取指方式将代码存储在片内存储介质中,运行时以片内BOOTROM启动,在启动程序执行完毕后直接转入片内存储介质运行主程序。 此方式下的SRAM 主要存储临时数据变量,比基于SRAM 的取指方式消耗更小SRAM,但取指速度可达同等水平。 尽管如此,此方式采用的片内集成存储往往需要大电压工艺,因此流片费用更高。

如图1(c)所示,基于片外存储介质的取指方式将代码存储在片外介质中,运行时以BOOTROM 启动,但不从片外介质中拷贝主程序指令到SRAM,而是让CPU 直接从片外介质中读取主程序指令并在片外介质中运行。 在此方式下,SRAM 主要用于存储临时数据变量,所需容量较小,而片外存储介质一般为Flash,价格低,存储容量大。 此方式成本低,但运行速度慢。

表1 列明了上述三种SoC 系统取指方式的主要特征。

图1 SoC 系统三种取指方式

表1 三种SoC 系统取指方式特征

具体到无线充电应用场景,特别是支持QI3.0无线充电协议的情况具有以下特征:ASK 解调最快速率是4 kHz; 最短包间隔为6 ms, 重要的包如Control error pack 典 型 包 间 隔 为250 ms,Received power packet 典 型包间隔为1.5 s; 对于无线充电最重要的PID 调节算法,调节时间有20 ms,一个调节过程中的一次子迭代时间最长可达5 ms。上述特征表明无线充电应用中的协议功能实现基本以毫秒为单位,若采用基于SRAM 或基于片内存储介质的取指方式, 其运行速度超过无线充电应用需求,且价格昂贵,而使用基于片外存储介质的取指方式,可以很好地平衡速度、功耗、成本三者的关系。对于速度要求较高,CPU 处理指令较为密集的模块,如ASK 处理模块、PID 浮点迭代计算模块等,则可以考虑以外围设备方式挂在CPU 的总线上的数字硬件电路实现。 因此,本文选用基于片外存储介质的取指方式。

1.2 系统架构

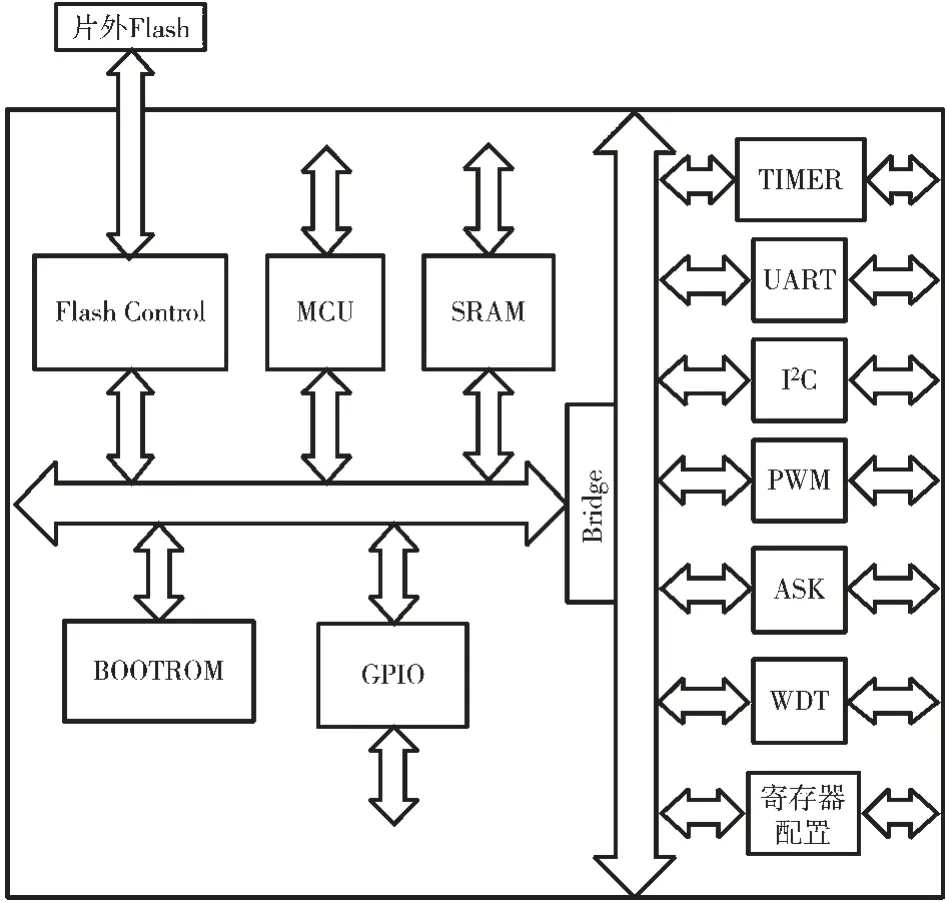

如图2 所示,本文基于SoC 片上系统实现无线充电系统芯片架构设计,使用芯片内执行技术(Execute In Plasce,XIP)即应用程序能够在片外Flash 内直接运行,无须再将主程序指令拷贝到系统SRAM 中运行,具有芯片集成面积小且成本低的优点。

图2 基于片外Flash 编程加载的SoC 系统框图

该无线充电芯片的硬件设计主要包括微处理器、存储器、外围接口控制3 个部分。 芯片处理器内核采用32位ARM Cortex-M0 处理器,核心架构为ARMv6-M,相比于其他的16 位与8 位处理器,运行速度较低且功耗低。Cortex-M0 处理器采用的片上互联总线为AMBA 总线,包括高级高性能总线(Advanced High-performance Bus,AHB)和低速总线(Advanced Pcriphcral Bus,APB)。 为了保证总线带宽的合理使用,本架构将系统要求高速运行的接口和处理器、存储器挂在AHB 上,将模块和低速接口挂在APB 上。 存储器主要由BOOTROM、SRAM 和片外Flash 组 成。 BOOTROM 存 储MCU 的Bootloader,Bootloader负责完成整个系统的加载启动任务。 SRAM 主要存储数据变量,存储容量需求低。片外Flash 存储整个系统的主应用程序,且可根据需要随时扩展存储容量。 外围接口控制包括片上总线、中断控制器、I2C 接口、UART 接口、看门狗、通用输入输出接口、定时控制器、ASK、PWM 等。

2 SoC 集成电路系统的设计

本章针对芯片实际应用中遇到的看门狗复位及低功耗问题提出了具体的解决方案。

2.1 看门狗复位实现方式

嵌入式系统一般采用看门狗机制监视系统的运行,以提高产品的可靠性。本系统采用软硬件结合的方式实现看门狗机制。在此机制下,如果在规定时间内,看门狗定时器没有收到来自系统的触发信号,则系统会强制重启,以维持正常的工作状态[11]。

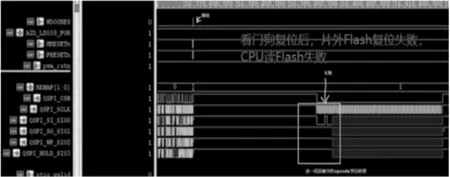

针对基于片外Flash 加载运行的SoC 系统,看门狗复位流程将变得更复杂,原因如下。在此系统中,由于存储器处于片外,通常选择Flash 进入高性能模式进一步提高SPI 读写指令的通信速度。 在此模式下,如图3 所示,片外Flash 会忽略SPI 通信中的命令部分,借此将读写速率提高。 因此,片外Flash 将不再接受正常的SPI 通信命令,而是将正常命令当作不含命令的读请求。 而芯片在看门狗启动复位后,会以正常方式而非高速方式向片外Flash 发出读命令和控制命令。 然而,此时片外Flash 由于不受芯片重启的影响,仍工作在高性能模式,无法实现对片外Flash 的正确读写。片外Flash 复位失败情况如图4 所示。

图3 QSPI 读指令时序

图4 片外Flash 复位失败

针对以上问题,本文提出以下两种解决办法。 一种是在BOOTROM 中添加对片外Flash 进行复位的SPI 指令,使其从高性能模式下恢复。若芯片已经制造完成,而BOOTROM 中没有加入相应指令,则可以选择第二种方法,即在运行主应用程序时,不让片外Flash 进入高性能模式,而是使用普通的QSPI 进行指令读取,从而使得取指令速度有一定程度的降低。 例如,假设SPI 时钟为100 MHz,则当片外Flash 工作在高性能模式时,取一条32 位指令需要20 个周期,取指速度为5 MIPS,若使用普通状态,则取一条32 位指令需要28 个周期,取指速度为3.6 MIPS,速率降低约30%。 但如果应用场景允许在这种速率下使用,则可以节省重新改版的成本和风险。 本文为节省成本,不再重新设计和升级BOOTROM,因此看门狗设计采用第二种方案,确保CPU 正常工作。

2.2 芯片低功耗实现

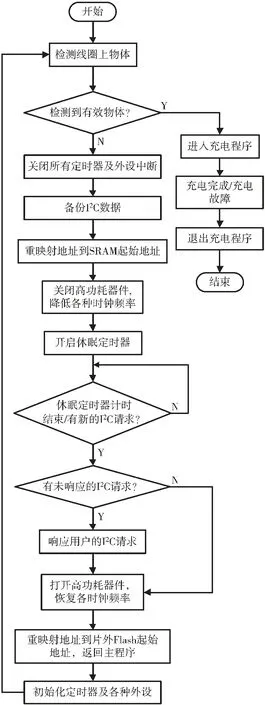

由于在片外Flash 运行休眠代码的功耗较大,因此利用有限的SRAM 资源将片外Flash 存储的休眠程序拷贝到SRAM 中运行。 另一方面,在低功耗模式下,当片外Flash 与芯片之间的通信断开,可以关闭片外Flash的供电以进一步节省功耗。 芯片低功耗实现流程如图5所示。

图5 芯片低功耗实现流程图

3 性能验证

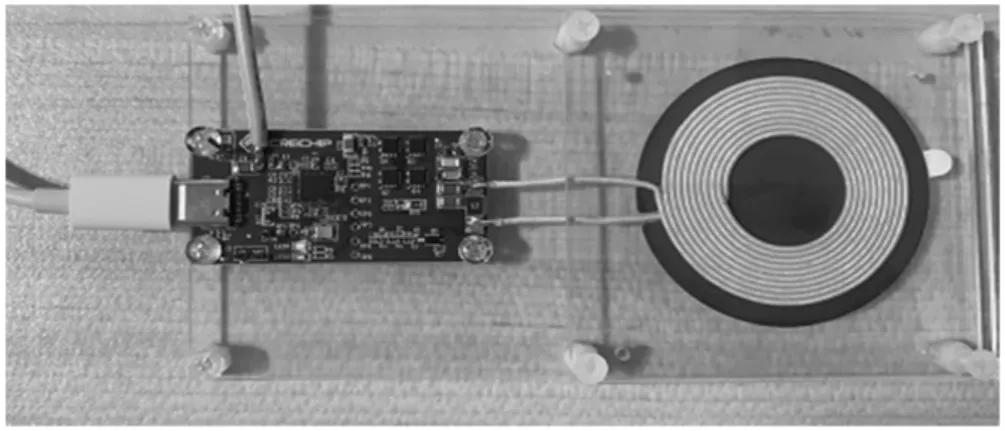

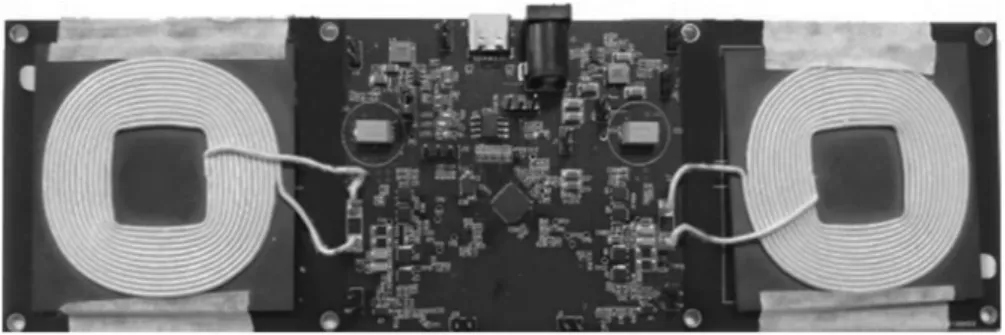

本节对提出的看门狗复位解决方案进行仿真验证,对提出的低功耗实现方案进行实验验证,并进行无线充电性能测试。 实现的芯片面积只有5 mm2,成本较低,样品如图6 和图7 所示。

图6 单线圈无线充电器样品图

图7 双线圈无线充电器样品图

3.1 看门狗复位仿真

如图8 所示,当看门狗复位后,AHB 和APB 总线都会复位,从而导致AHB 和APB 总线上的设备(包括Flash控制器)也全部复位。 如图9 所示,当Flash 控制器的偏移地址复位为0 地址后,可对片外Flash 进行正常的读操作,并重新加载运行应用程序。

图8 总线复位

图9 片外Flash 正常复位

3.2 低功耗性能验证

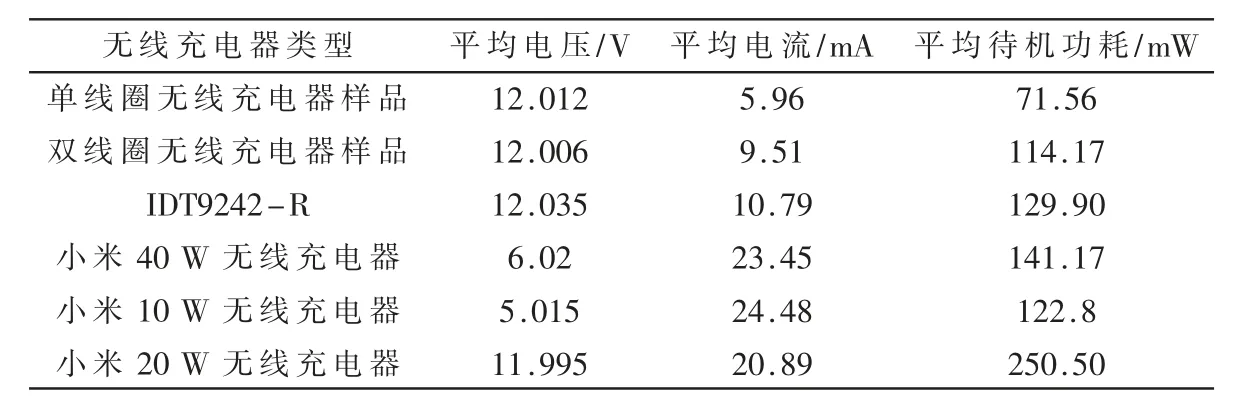

使用相同的QC3.0 充电器给不同类型的无线充电器供电,待机状态下充电5 min,计算对应的平均待机功耗,所获得的实验数据如表2 所示。 测试结果表明该无线充电系统达到了低功耗的设计要求,且与不同类型的无线充电器相比, 本方案设计的无线充电系统具有较低的待机功耗,具有一定的实用价值。

3.3 无线充电性能测试

图10 显示了单线圈无线充电器样板给iPhone8充电的电压、电流以及功率曲线表明输入功率最大可达到9.5 W 且持续时间长达30 min, 充电稳定,大约耗时4 小时充满电量。

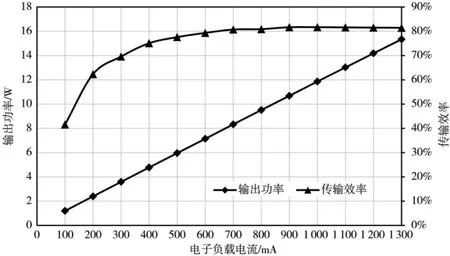

采用单线圈无线充电器样板接稳压电源,设置额定输入电压为12 V, 放置单线圈无线充电器的发射线圈与接收装置的接收线圈于水平同轴位置, 设置传输距离为2 cm。 图11 记录了接收端在不同带载能力下的系统输出功率和传输效率。 目前无线充电设备的传输效率普遍为75%左右,若低于70%,则发热效果会较明显。 图11 表明本文实现的无线充电系统传输效率可达80%,符合设计要求。

表2 不同类型无线充电器的待机功耗

图10 iPhone8 完整充电曲线

图11 负载电流传输特性

4 结论

本文设计了一款基于片外Flash 编程加载的无线充电系统,将主程序代码存储在片外Flash 上,并直接在片外Flash 中运行。进一步,本文针对芯片看门狗复位及低功耗问题提出了解决方案。实验结果表明系统设计合理且提出的若干解决方案有效,充电性能稳定,成本较低,易于批量生产,具有广阔的市场前景。

(收稿日期:2020-07-12)