一种新型的地址总线取址方法

四创电子股份有限公司 廖 芹

本文提供了一种新型的地址总线取址方法,用于一些插槽机箱的背板接口的地址映射,便于数据通信。即通过SPI总线与CPU进行通信,IO资源占用少;通过分压取地址的方式,只需改变背板的分压电阻值,细分电压档位就可以扩展插槽;且取址方法精度高,任何一个功能模块插在这个插槽里面,通过AD采集,处理器即可通过SPI总线的通信方式得知功能模块的地址。

为了实现更多的功能,很多机箱的背板上设置有很多插槽即硬件接口,通过插槽与一些可插拔的功能模块进行连接实现某些特定的功能。为了便于与这些功能模块进行通信或者对这些功能模块进行监控,通常需要为各个插入插槽的功能模块分配唯一的地址。

目前,常采用如下方法进行硬件地址分配。在背板的插槽上设置多个用于分配硬件地址的引脚,各引脚的信号输出可以为1或0。通过各引脚的数字信号1或0的组合,实现硬件地址的多样化,这样CPU通过检测各引脚的电平就能得到该插槽的地址。例如当背板上有16个插槽时,可以在每个插槽上设置四个引脚,通过0/1编码的方式,四位地址编码从0000到1111,共有2的4次方即16个地址。但是当插槽需要扩展到32个插槽时,就需要32个硬件地址,那么插槽上的引脚个数需要从4个增加到5个。在硬件电路设计中,就可能会因为CPU的I/O资源不够,需重新进行选型,增加设计开发周期,增加硬件成本,从而不利于插槽的扩展。

1 设计内容

为了方便插槽的扩展和合理使用CPU的IO资源,我们提出一种新的地址取址方法,且提出不同的电压档位,得到不同的电阻取值。其设计的主要步骤如下:

(1)硬件电路设计的基本原理(框图如图1所示)

图1 电路原理示意图

LDO电源转换芯片REF196主要提供精准的3.3V电压,LDO的精度范围-2mv~+2mv。REF196给AD转换芯片AD7910独立供电。AD7910采用10bit的采样速率进行AD采集,共有1024档位。AD7910通过SPI总线方式与ARM进行通信。

(2)将背板接口地址ADC_addr作为AD7910的输入,采用分压的方式取地址,原理图如图2所示。

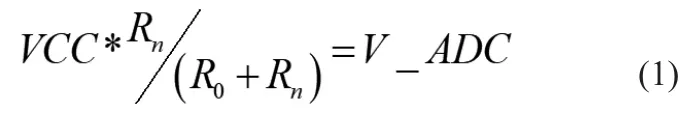

插槽第一端电压(即背板插槽分压电压)V_ADC与插槽电阻(即背板分压电阻)Rn的关系如下所示:

其中n=1,2…m,m为插槽的个数,VCC为Vout_3.3V与GND电压的差值。

取VCC=3.3V,R1=1K(精度为1%),若电压取0.1V/档,可以扩展成33个插槽,0.15V/档就是22个插槽,0.2V/档就是16个插槽,同时能够保证系统具有较高的测量精度。

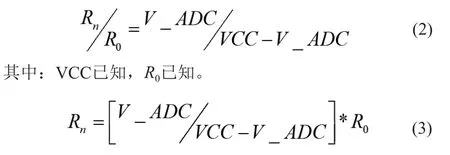

(3)AD7910通过SPI总线方式与ARM进行通信,ARM扫描得到区间信息,分段区间与相应插槽编号的对应关系如下表1所示,AD7910采用10bit的采样速率进行AD采集,共有1024档位。AD采样精度:3.3V÷1024≈3.3mV;本方案中取0.15V/档,则分段区间为:0.15V÷3.3mV≈ 45.45mV。

将上述1024个档位均匀分成22个档位区间,去掉头、尾各一个取中间的20个档位区间,这20个档位区间与插槽标号1-20一一对应。根据电压和档位的关系以及上述档位区间,将采样基准电压3.3V均匀分成20个电压区间,所述的电压和档位的关系为电压=(采样基准电压/最大档位)*档位区间端点值,即电压=(3.3V/1024)*档位区间端点值,电压区间如表1所示,所述20个电压区间亦与插槽标号1-20一一对应。根据所述插槽电阻与第一端电压V_ADC的对应关系(即式2)和上述20个电压区间得到20个电阻区间(请参照表1)。为所述插槽电阻取值时插槽编号为1的插槽电阻R1取对应的第一电阻区间内的值,依此类推,插槽编号为20的插槽电阻R20取对应的第二十个电阻区间内的值。为提高采样可靠性,在电阻选取时,选择AD分段区间中间值所对应的电阻值,即电阻区间的中间值,亦即表1所示的标称电阻值,保证采样具有最高的稳定性及可靠性。在电路设计中,AD采样的电压值,除了电阻配比外,还由供电电压的稳定性决定,在本设计方案中,采用REF196的输出电源为AD采样的参考电压,由REF196自身电气特性决定,3.3V最大压降为100mV,在设计分段区间是采用每46等份为一分段区间,对应的电压值为:46*3.3mV=151.8mV,对分段区间及AD采样获取的地址无影响,具有较高鲁棒性。

表1 AD档位、电压、电阻分区示意图

当需要扩展插槽时,可根据需求设计新的配置方案,便于插槽扩展,系统升级。同时本文中的背板和取址方法具有高灵敏度、高精度、高可靠性。

2 结束语

随着嵌入式技术的不断发展,硬件开发越来越重要,模块化板卡越来越常见,这种用于插槽机箱的背板接口的地址映射而进行的数据通信应用广泛,本文中提出的这种利于插槽扩展的硬件地址取址方法和装置在硬件开发中节约成本且减少开发周期,将CPU的IO口资源占用及插槽扩展等问题进行了有效的解决。