基于最小平方法的电表晶振补偿研究

梁 捷,梁广明,黄水莲

(1、广西电网有限责任公司计量中心,广西 南宁 530023;2、南宁百会药业集团有限公司,广西 南宁 530003)

0 引言

随着智能电网的发展和电力市场化改革的不断深化,对智能电表的技术要求从以往的单纯电能量计量,逐步发展为可实现阶梯和分时电量计费,带时标存储日月冻结数据以及需量叠加等多种高级应用。许多功能的实现都依赖于电表准确的时间同步技术〔1〕。故电表需要具备一个准确的计时单元作为实时时钟源,以作为各项与时间相关功能实现的基准。这一计时单元不仅要求常温条件下能够准确计时,在电表工作的整个温度范围内的偏差也不能超过规定范围〔2〕。如何保证该计时单元在整个温度范围内时钟的可靠性和准确度,使电能表的日计时误差能满足南方电网技术规范要求,已成为时钟芯片厂家和电能表厂家关注的问题。

本文从影响电能表晶振时钟脉冲信号精度的因素出发,结合工程应用中的性能要求,阐述了作为电能表常用时钟源的晶振的频率-温度特性和常见的时钟校正原理,探讨了实现高精度晶振时钟数字补偿的设计方案。最后通过实际案例验证了本文优化策略的有效性。

1 晶振时钟补偿原理

1.1 晶振偏差特性分析

电能表在正常工作时,需要以一定周期计时的时钟信号来确定在各时间段里系统各部件的工作安排,使得每个部件的工作能够在同一节奏下协同进行。而且,智能电表的分费率和预付费功能要求其日计时误差在±0.5 s/d以内,且在电池供电时须保证时钟正常工作〔3〕。考虑到电池的使用寿命,一般选择低频、低功耗的石英晶体振荡器(以下简称晶振)作为实时时钟(real time clock,RTC)信号源〔4〕。晶振由晶核和各种半导体组成,频率特性主要由其内部晶核决定,而晶核的晶体振动模式、频率范围和温度特性等性能主要受其切割工艺影响。晶振按切割工艺通常可分为音叉型、AT切型、声表面波型三种〔5〕,每种类型都具备特有的频率范围和温度特性。目前电表、石英手表等计时设备中普遍采用频率为32 768 Hz的低频音叉晶振提供基准计时脉冲,由于32 768=215,该晶振输出信号经过15次二分频后正好是一秒〔6〕,其频率-温度特性曲线如图1,表现为拋物线,在高温和低温时频率偏差增大,在电能表-25℃~+60℃的极限工作温度范围内很难满足仪器仪表的精度要求。

图1 音叉型晶振频率-温度特性曲线

此外,由于晶振生产工艺的差异,环境温度变化,元器件老化等原因也会对其温度等特性产生影响〔7〕,使其在使用时与基准时钟之间存在一定的偏差,该偏差会随着使用时间增长而不断累计增加,从而导致电能表出现日计时误差超差等现象,故须对电表晶振进行温度校正。

1.2 晶振校正原理

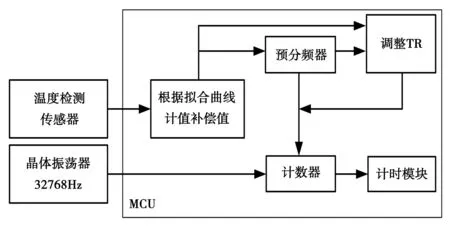

晶振的校正方式可分为模拟补偿和数字补偿。模拟补偿即硬件自校正,通过提高或调整晶振晶核本身、负载电容、电压、应力及优化硬件拓扑结构等措施,以达到理想的精度。数字补偿通过设置特定的补偿寄存器(trim-register,TR),使其在固定时间间隔内增减时钟脉冲个数进行调整,从而达到补偿的目的。具体又包括调整高频振荡时钟脉冲个数和低频 32 768 Hz时钟脉冲个数两种方法。智能电表的常见时钟芯片中,DS3231采用的是电容模拟补偿,而RX-8025则采用数字补偿。晶振低频 数字补偿原理如图2所示。

图2 晶体振荡器低频数字补偿原理

如图2,晶振低频数字补偿法通过修改预分频器和调整TR的数值,可增减计数周期内低频32 768 Hz晶振的时钟脉冲个数,从而影响计数器的秒进位频率〔8〕,例如STM32F1XX系列和STM32L1XX系列芯片正是采用此方法;SH79F642则是采用调整计数周期内高频振荡时钟个数的方法。相对高频计数,低频计数因脉冲频率较低,晶振输出脉冲周期不能成为系统工作周期的约数,故可能会在各工作周期内增减不固定的低频时钟脉冲个数,从而因整体秒信号输出不均匀而导致出现某计数周期内的短时误差。这虽对长时间的累积误差影响较小,但如需秒输出均匀,可通过高频捕捉法修正,即在固定时间周期内,使用高频计数的定时器测量并计算周期内的累计计时误差,然后平均到每秒,根据每秒误差,修改秒窗口定时器,比较寄存器数值,通过定时中断方式输出秒信号。无论是低频补偿还是高频补偿,其补偿的关键都是获取补偿值并写入数字校正模块的TR中。

2 晶振数字补偿方案研究

2.1 设计方案对比

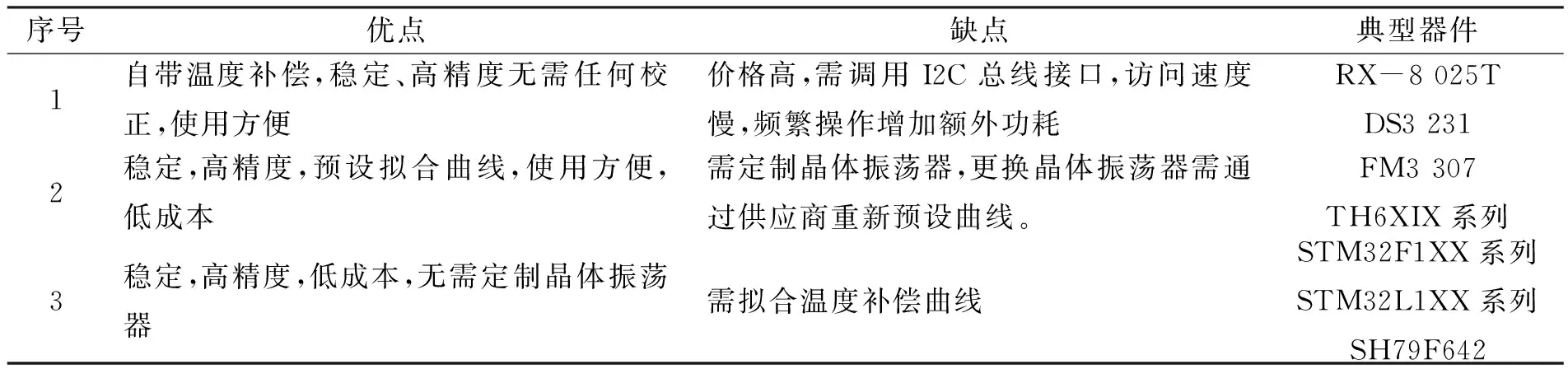

在智能电表中,常见晶振低频数字补偿设计方案包括以下三种,表1对比了这三种方案的优缺点。

表1 三种RTC补偿方案对比

方案1:采用独立时钟芯片。该芯片自带补偿模块,时钟输出精度稳定、可靠,操作与应用方便。但其不仅价格高、有悖于降本增效,而且芯片内置的补偿模块必须通过I2C总线获取日历和基准时间等相关信息,在电池供电环境下频繁读取,会增加额外功耗,减少电池使用寿命。

方案2:采用片上系统(system on a chip,SOC)+预设拟合曲线的RTC模块。SOC〔9〕以独立模块的方式集成在微处理器(Microcontroller Unit,MCU)芯片上,片内除了晶振数据交互接口模块之外,还预设供应商提供的温度补偿拟合曲线和温度补偿模块,用户只需频偏校正,操作方便。但由于该方案需要定制对应的晶体振荡器,且更换晶体振荡器须通过SOC供应商修改预置拟合曲线,故兼容性较差。

方案3:SOC模块同方案2集成在MCU芯片上,后期通过MCU校正。因SOC片内既无温度补偿机制,也无预设的温度补偿拟合曲线,所以应用时后期必须通过MCU控制时钟来源、时钟的分频系数等方式进行温度补偿等校正才能满足时钟精度要求。补偿算法对RTC精度影响较大。

综合考虑应用需求和成本,本文基于方案三采用最小平方法拟合晶振温度特征曲线,对晶振因温度影响而产生的时钟频率偏差进行补偿,以满足时钟输出稳定、高精度的要求。

2.2 基于最小平方法的电表RTC补偿模型

首先建立晶振的实时时钟误差模型。晶振在秒脉冲的输出过程中,与基准时钟存在一定的偏差。设第x(x∈N+)个晶振秒时钟相对于基准时钟的偏差为

ΔTx=R+d(x-1)

(1)

式中:R为晶振第1个秒时钟与基准时钟的偏差,即初始频偏,该偏差主要与温度有关,可根据图1按式(2)进行拟合。每个晶振秒时钟输出间隔与基准时钟间隔的偏差为d。

R=β(W)=f+gW+hW2

(2)

式中:W为晶振的环境温度,可通过单片机自带的温度传感器测量。f,g,h分别为R的二阶多项式系数。

由等差数列的前x项和公式,晶振输出的第x个秒时钟相对于基准时钟的累计偏差θ(x)为

(3)

式中:a为晶振秒时钟与基准时钟的初始偏差。令b=(d/2+R),c=d/2,则由式(3)可得多项式形式的晶振时钟误差模型

y=θ(x)=a+bx+cx2

(4)

晶振秒时钟与基准时钟的偏差y可结合补偿方案进行周期测量。

最小平方法常用于通过现有的样本值对未知模型进行参数估计,它的目标是获取一组系统参数,使得所估计的系统与实际系统的残差平方和最小化〔10〕。

对测得的一组离散输入数据{(xi,yi)}(i=0,1,2,…,m),为不失一般性,对n阶多项式,由最小平方法?待辨识的参数序列E(a0,a1,a2,…,an)满足

(5)

为使得E在可行域内达到最小值,有

k=(0,1,2,…,n)

(6)

以矩阵形式表示为

ATAa=ATY

(7)

其中,

(8)

求解式(7)可得参数α的最佳估计值

α=(ATA)-1ATY

(9)

电表厂家执行该方案的主要过程为:首先,对同类型、同批次或具有类似温度特征曲线的晶振,通过温度传感器获取一组晶振温度-频偏序列,然后采用最小平方法拟合初始频偏模型的系数,并将该模型预置到MCU芯片中。电表运行时,通过温度传感器测量晶振环境温度,然后通过预置的初始频偏模型计算初始频偏。接着,读取基准时钟计算历史秒脉冲偏差,建立历史偏差测量结果序列{(xi,yi)},然后建立晶振的时钟误差模型并通过该序列估计模型参数α`={a、b、c},接着根据该模型求得晶振在下一时段的时钟累计误差。最后,计算补偿值写入指定TR,再由计时模块对晶振时钟累计误差进行实时补偿,可获得高精度同步时钟。

3 试验与验证

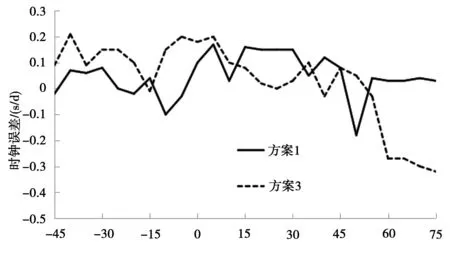

为了验证本文基于最小平方法的晶振时钟数字补偿方案的有效性,设计了时钟精度的热稳定性试验和功耗试验。首先将应用本文方案的芯片STM32F10和应用方案1的独立时钟芯片DS3231分别装入同厂家,同型号,同批次的南方电网规范的单相载波智能电表中。热稳定性试验时,电表为非通讯状态,在参比频率,额定电压以及-45 ℃~+75 ℃的温度范围内,通过电能表检测装置的日计时测试功能测量该批电表的秒脉冲输出误差,以此评估时钟精度,测试结果如图3所示。

图3 不同方案电能表时钟精度测试结果

由图3可见,在测试温度范围内,两种方法测试结果的秒脉冲输出误差数据均分布在±0.4 s/d范围内,能满足单相智能电能表技术规范中对日计时误差在-25 ℃~+60 ℃的极限工作范围内不超过±0.5 s/d的要求,两种不同的数字补偿方式对时钟精度的补偿效果差别不大。此外,高温70 ℃以上,方案1误差的绝对值开始超过0.3 s/d,75 ℃时达到-0.32 s/d。而方案3在70 ℃以上时,误差仍能保持在±0.3 s/d内,表明方案3与方案1相比,在70 ℃~75 ℃的高温环境影响下时钟精度的热稳定性较好。

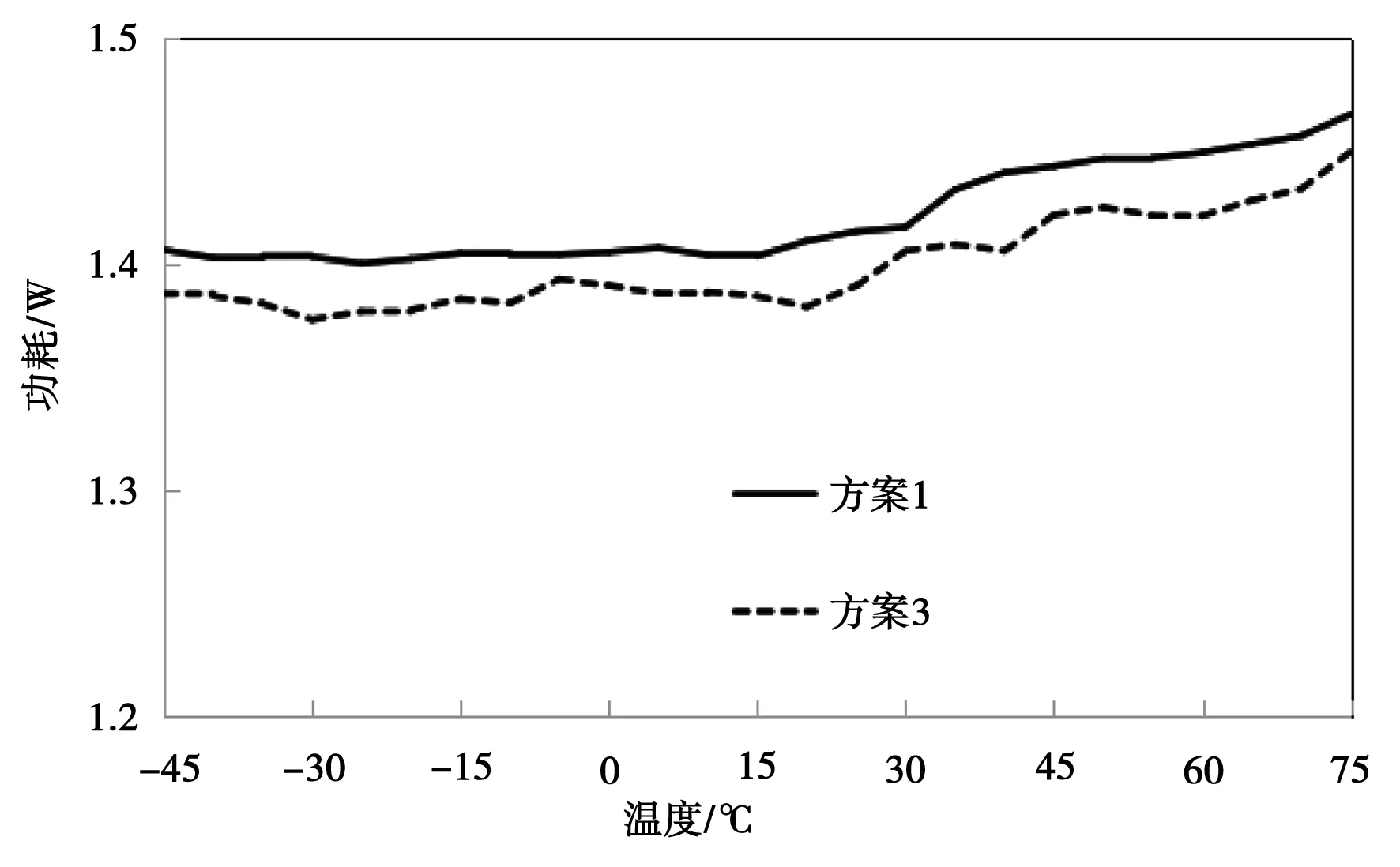

功耗试验时,在参比频率,额定电压以及-45 ℃~+75 ℃的温度范围内,通过电能表功耗测试仪测量该批电表电压线路的有功功率消耗,测试结果如图4所示。

图4 不同方案电能表功耗对比

由图4可见,温度超过35 ℃后,电能表功耗提升幅度较明显,这是由于高温时,集成电路中CMOS管的漏电流增加,会使得芯片的静态功耗上升。两种方案测试得的电表电压线路总功耗均小于1.5 W,能满足单相智能电能表技术规范中对电压线路功耗不超过1.5 W的要求。在-45 ℃~+75 ℃温度范围内,整体上看,方案3在各温度下测得的功耗均低于方案一。方案3的平均功耗比方案一低约1.5%,但差距不大。这是由于方案1外置时钟芯片的补偿模块为了进行晶振时钟频率偏差数字补偿,必须通过I2C总线获取基准时钟等数据,频繁读取总线数据会增加额外功耗,而且多次数据读取的过程也提高了受到外部干扰的信息安全风险。

4 结论

首先对电能表常用的计时单元,即晶振的频率-温度特性进行分析,建立了晶振实时时钟误差模型,然后设计了基于最小平方法曲线拟合的晶振时钟数字补偿方案。案例测试结果表明,基于本文方案的电能表在工作范围内的时钟精度可达到与独立芯片同等的技术指标,满足电能表应用的技术性能要求,验证了本文方案的有效性。同时本文方案运行功耗稍低于独立芯片,在降低智能电表线路损耗方面具有应用价值。