基于FPGA的MMC建模与实时仿真

翟鹤峰,黄冠标,赵利刚,洪 潮

(直流输电技术国家重点实验室(南方电网科学研究院有限责任公司),广州 510663)

由于模块化多电平换流器MMC(modular multi⁃level converter)具有凭借开关频率低、谐波特性好、可扩展性强等独特优势,已被广泛应用于国内外数项柔性直流工程[1-2]。MMC的接入使得电力系统的动态特性更加复杂,针对传统电网的稳态仿真分析已不能满足需求,需要借助详细的电磁暂态仿真来深入了解MMC系统的运行机理与动态特征。离线电磁暂态仿真可对较小规模MMC的复杂动静态特性进行分析,但对大规模高电平MMC详细模型的计算用时往往是难以忍受的。实时仿真能够在小于或等于仿真步长所对应的物理时间内完成每个时步的计算任务,可与物理世界同步实现对MMC暂态行为的模拟。这使得实时仿真具备硬件在环测试的能力,即通过将MMC实时仿真器与实际物理装置连接,可以对各种控制策略和保护方案开展近乎工程实际的无损化有效验证,这对于MMC系统的技术创新、算法测试、设备研发具有重要意义[3]。

在实际工程应用中,为了提升输送电压等级,MMC每个桥臂往往由数百个子模块级联而成[4],每个子模块又包含若干电力电子器件,庞大的仿真规模给实时仿真精度和计算速度带来了严峻挑战。一方面,MMC不同子模块中的开关器件往往不是同时动作的,对该类元件的精确仿真要在μs级步长下进行;另一方面,MMC中成百上千个电力电子开关器件导致节点导纳矩阵的维度大,而实时仿真要求高阶线性方程组求解必须在一个仿真步长内完成,繁杂的解算任务必然导致较长的求解时间,对MMC仿真的实时仿性提出了极大的挑战。

对桥臂进行等效化简是解决大规模MMC电磁暂态仿真困难的有效途径[5-10]。文献[6-7]提出了基于受控电压源和受控电流源的MMC电磁暂态通用模型,通过将每个桥臂置换为受控电压源,同时将桥臂中的子模块断开连接并在正端口连接受控电流源,实现了桥臂与子模块之间的电气解耦,从而降低了解算难度。加拿大曼尼托巴大学Gole教授研究团队首次提出了基于戴维南等效的MMC模型[8],以此为基础,文献[9]和[10]分别提出了基于后退欧拉法和梯形法的戴维南等效整体模型,以提升MMC电磁暂态计算的仿真效率与求解精度。上述等效化简方法虽然通过减少节点数量降低了计算复杂度,但对采用几十μs甚至几μs仿真步长的MMC实时仿真仍存在一定的挑战。这是因为MMC桥臂的等效阻抗是随桥臂中所有子模块的工作状态而实时变化的,桥臂等效阻抗的频繁变化会导致系统节点导纳矩阵的不断更新,为在线求解高阶线性方程组带来了极大的计算困难,不适用于高电平数MMC系统的实时仿真。因此,如何进一步提升MMC等效化简模型的求解速度,是大规模MMC系统实时仿真面临的瓶颈。

除了对MMC模型等效化简外,采用高性能的底层硬件也是实现大规模MMC小步长实时仿真的重要手段。相比于串行器件,现场可编程门阵列FPGA(field programmable gate array)具有并行底层结构、分布式内存单元、流水线架构等特性,这些优势使得FPGA在MMC实时仿真领域受到了广泛的关注[11-14]。文献[13]开发了一种基于FPGA的实时仿真异构计算平台,基于采用替代电路的MMC桥臂等效模型,该平台将MMC电路与电网解耦,进而实现了电网与MMC桥臂等效电路的并行计算。依托先进的实时仿真器RTDS,文献[14]提出了一种基于FPGA和RTDS的联合实时仿真平台,其中FPGA专门负责MMC阀组的戴维南等效解算,并将计算结果等效为受控戴维南支路,RTDS承担包含6个桥臂等效支路在内的交直流系统的仿真任务,并采用小步长(2.5 μs)求解以确保仿真精度。上述方案虽然完成了MMC等效模型的实时仿真任务,但实现过程较为复杂,并未从根源上解决子模块开关状态频繁切换带来的解算任务量大等问题。

本文提出了一种基于FPGA的高效MMC戴维南等效模型,并利用硬件描述语言Verilog HDL开发了MMC实时仿真平台。该模型首先假设子模块在投入和切除状态下具有相同的等效阻抗,然后在具有恒定等效阻抗的桥臂戴维南模型上加入受控电压源进行补偿,以避免开关状态切换导致的系统节点导纳矩阵频繁更新。为发挥FPGA的硬件优势,本文对MMC的控制系统和电气系统并行求解,同时以流水线的形式对MMC系统的所有桥臂与子模块进行解算,有效提升了MMC实时仿真器的硬件资源利用率和仿真效率。在实时仿真平台上对25电平双端MMC-HVDC系统进行了测试,实时仿真器与PSCAD∕EMTDC的仿真结果基本一致,验证了高效MMC戴维南等效模型的正确性和仿真精度。

1 MMC实时仿真模型

1.1 MMC拓扑结构

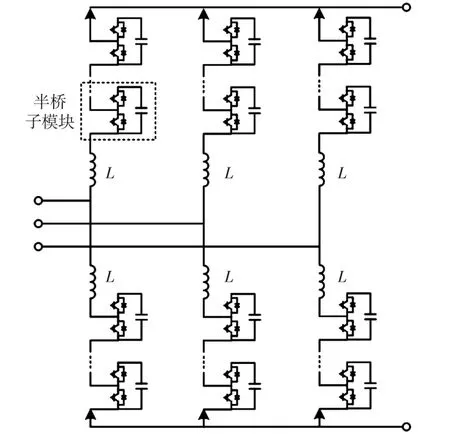

MMC的通用拓扑结构包含三相六桥臂,每个桥臂由限流电抗与若干子模块级联而成。针对子模块的拓扑,国内外学者相继提出了半桥型子模块、全桥型子模块、双箝位型子模块和自阻型子模块等结构。考虑到半桥型子模块在实际工程中的应用最为广泛[1],相关理论研究也更为成熟,因此本文选取半桥型MMC作为研究对象。

经典的半桥型MMC拓扑结构如图1所示,每个子模块由两个绝缘栅双极型晶体管IGBT(insulat⁃ed gate bipolar transistor)开关器件、两个反并联二极管和一个存储电容构成。当上侧IGBT导通且下侧IGBT关断时,子模块的输出电压为电容电压;当上侧IGBT关断且下侧IGBT导通时,子模块的输出电压为0。通过控制上下桥臂触发子模块的数量,MMC交流侧可以输出多电平波形。

图1 三相半桥型MMC拓扑结构Fig.1 Topology of three-phase half-bridge MMC

1.2 MMC实时仿真模型

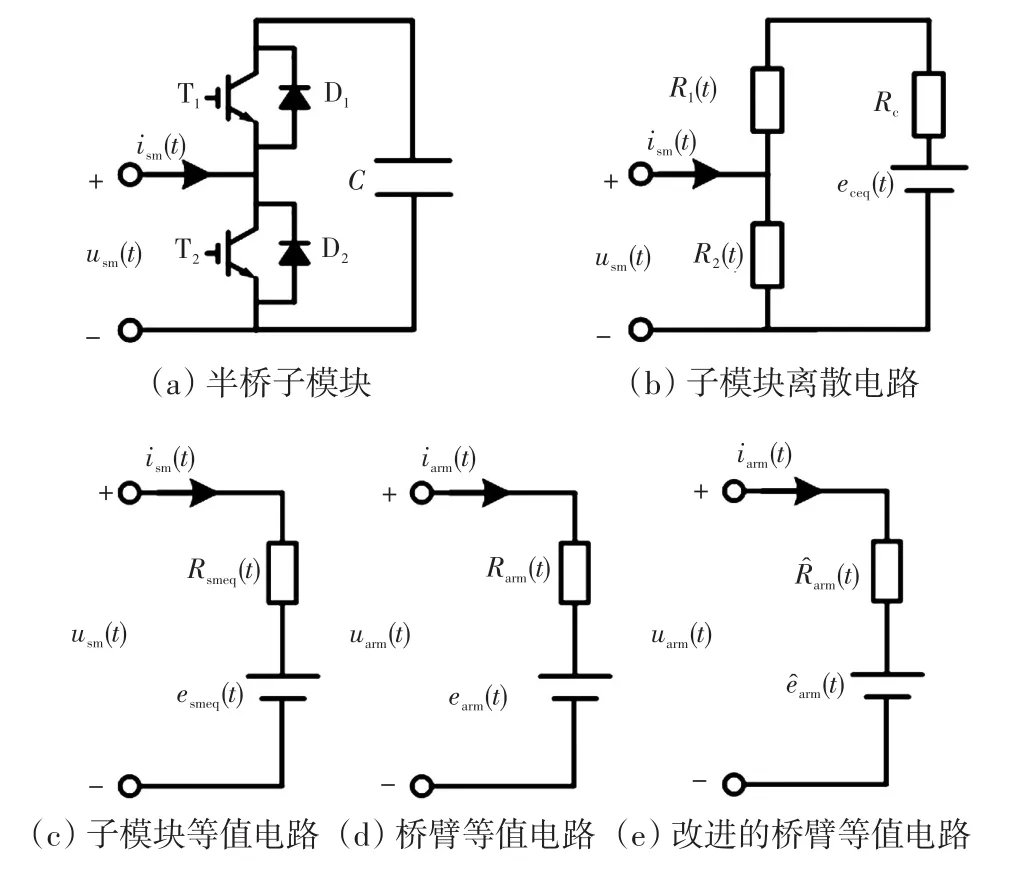

针对图1所示的三相半桥型MMC系统,对所有子模块进行详细建模将导致较大的仿真规模,不适用于大规模高电平MMC系统的实时仿真。因此,本文提出了一种高效的MMC实时仿真模型。首先,基于戴维南定理建立半桥型子模块的等效电路,通过对N个子模块的等效电路线性叠加获取桥臂的戴维南等效模型;进一步地,对子模块在不同工作状态下的戴维南等效阻抗采取近似处理,保持桥臂等效电路的戴维南等效阻抗恒定,从而避免高阶节点导纳矩阵的频繁更新。图2给出了高效MMC实时仿真模型的等效过程,其详细的等效原理如下。

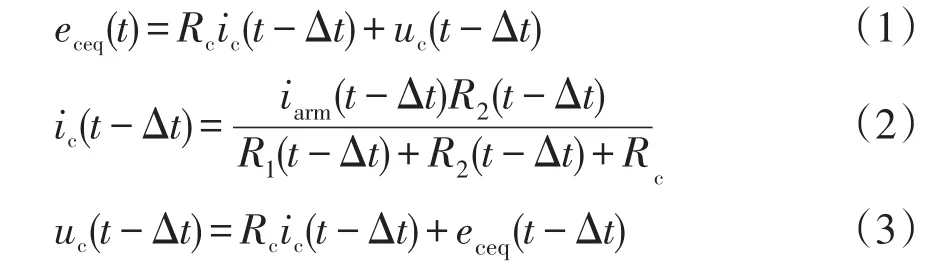

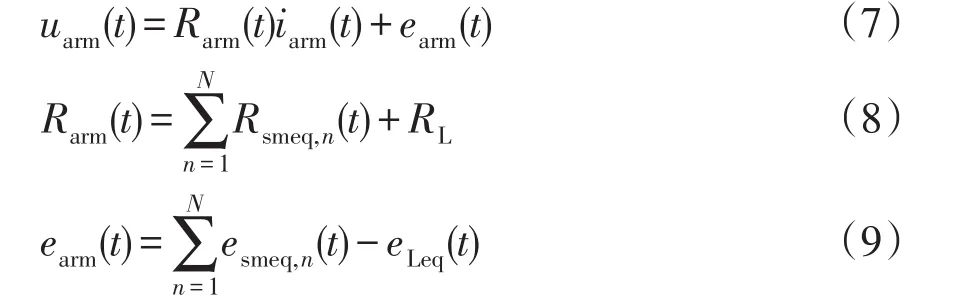

对于图2(a)所示的半桥型子模块,首先将子模块中的两个IGBT开关组(即一个IGBT和一个二极管反并联结构)分别用双值电阻R1和R2表示,当开关组导通时,取非常小的电阻值Ron(典型值10-3Ω);当开关组关断时,取非常大的电阻值Roff(典型值108Ω)。同时,将直流存储电容利用梯形法离散为电抗Rc与等效电压源eceq串联的戴维南等效电路[8],从而得到如图2(b)所示的子模块离散电路。其中,更新电容等效电压源eceq的计算公式为

式中:Δt为MMC模型的离散步长;uc为电容电压;ic为电容电流;iarm为桥臂电流。

基于戴维南等效原理,将图2(b)所示的离散电路等效为图2(c)的子模块等效电路,该电路模型的输入输出关系可用式(4)表示,子模块等效电路的戴维南等效阻抗Rsmeq和等效电压源esmeq的表达式分别如式(5)和(6)所示:

式中:usm为子模块的输出电压;ism为流经子模块的电流。

基于单个子模块的戴维南等效电路,将N个串联子模块的等效阻抗和等效电压源进行代数叠加,可获得如图2(d)所示的桥臂等效电路,该电路模型的输入、输出关系可用式(7)表示。桥臂等效电路的戴维南等效阻抗Rarm和等效电压源earm的表达式分别如式(8)和式(9)所示:

式中:RL为桥臂限流电感的电抗值;eLeq为限流电感经梯形法离散后的戴维南等效电路的等效电压源,其更新公式为

需要注意的是,桥臂等效电路的戴维南等效阻抗Rarm是随子模块中IGBT开关组的工作状态同步变化的,这将导致每个时步内均需要更新MMC的节点导纳矩阵并重新对其因子化,复杂的计算任务给小步长仿真的实时性带来了极大的挑战。根据开关状态预存所有节点导纳逆矩阵是实时仿真中的常用手段,然而对于含大量电力电子开关的MMC来说,这种方法使底层硬件的存储量过大(电平数为N+1的MMC理论上需要存储26N+1个矩阵),不适用于MMC的实时仿真。因此,本文对基于戴维南等效的桥臂模型进一步改进,以适应MMC实时仿真的需求。

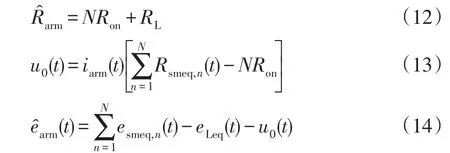

假设子模块在投入状态(T1导通,T2关断)和切除状态(T2导通,T1关断)下的等效阻抗相同且均为Ron,则桥臂等效电路的等效阻抗可以用式(12)表示。为了反映子模块状态切换对桥臂等效阻抗带来的影响,本文对桥臂的戴维南等效电压源串联一受控电压源u0,u0的表达式如式(13)所示,戴维南等效电压源可用式(14)来表示。

图2(e)给出了改进的桥臂等效电路模型,通过对投入和切除状态下子模块的等效阻抗采取近似处理,改进的桥臂等效电路具有了恒定的阻抗,有效避免了节点导纳矩阵随子模块工作状态的切换导致的频繁更新,极大地提升了MMC系统的实时仿真效率。

图2 MMC桥臂等效过程Fig.2 Equivalent process of MMC bridge arm

2 基于FPGA的MMC实时仿真设计

MMC的实时仿真不仅要对所有桥臂和子模块的等效电路进行求解,还要在同一时步内完成均压排序控制、PWM调制等控制过程的解算,尤其是均压排序控制中的排序算法,其复杂度与桥臂子模块的个数通常成线性或平方关系[15],如此大的解算规模给μs级步长下的实时仿真带来了严峻挑战。为了加速MMC的实时仿真,本文将MMC划分为电气系统和控制系统两部分,并在FPGA上分配专门的硬件资源进行并行求解[16]。其中,电气系统负责对MMC桥臂、RLC等各种电气元件进行仿真;控制系统主要负责MMC控制器的双环控制、PWM调制及均压排序等控制电路的实时仿真。

2.1 MMC电气系统仿真设计

图3 MMC系统的FPGA实现Fig.3 FPGA implementation of MMC system

针对MMC电气系统实时仿真,本文设计了基于节点分析法的并行计算与流水线技术深度融合的仿真架构,如图3的控制系统求解部分所示。在每一仿真步长内,实时仿真器首先对各电气元件的特性方程进行差分,形成等效电导和历史项电流源并联的离散电路,然后对所有元件的离散电路联立形成整个系统的节点方程,最后求解该节点方程获取系统中每个节点的电压,进而完成对所有元件支路电压和电流的更新。需要注意的是,实时仿真器对RLC、MMC桥臂元件等不同种类的电气元件采用并行计算形式,通过分配独立的FPGA计算资源,对各类元件分别设计了专门的解算单元;对于相同种类的众多电气元件,解算单元则以流水线形式进行求解[17],在提高仿真速度的同时提高硬件资源利用率。

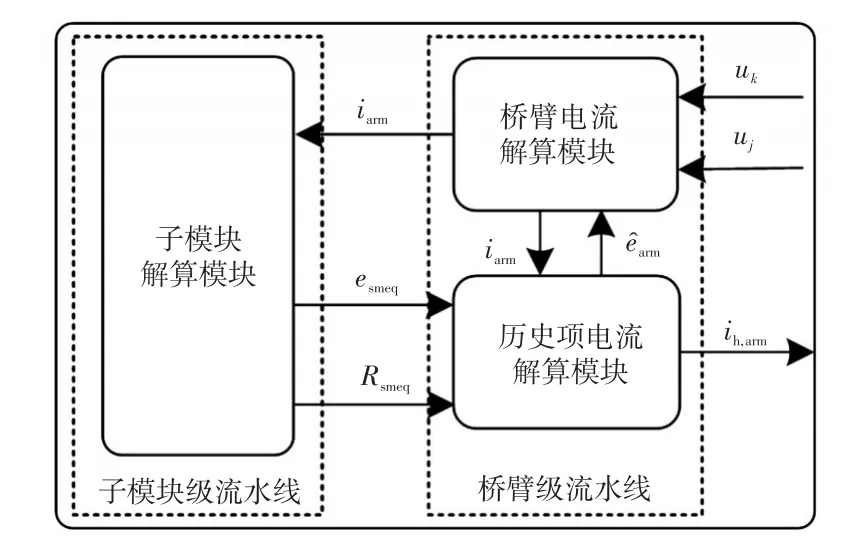

在本文设计的电气系统实时仿真框架下,MMC桥臂元件的基本解算流程是:首先求解桥臂元件的戴维南等效电阻Rˆarm和等效电压源eˆarm,生成历史项电流ih,arm;之后,通过求解系统节点方程获取桥臂元件的端电压uk和uj;最后更新桥臂电流iarm,并利用更新后的桥臂电流iarm和每个子模块中IG⁃BT开关组的等效电阻R1和R2,反向计算桥臂中所有子模块的电容电流ic、电容电压uc、等效电阻Rsmeq及等效电压源esmeq。考虑到大规模MMC系统中桥臂元件及每个桥臂中的子模块结构相同,数量众多,适合以流水线形式进行求解,本文设计了桥臂级和子模块级嵌套的双层流水线硬件解算结构。MMC桥臂解算单元的硬件设计如图4所示,主要包括桥臂历史项电流解算模块、桥臂电流解算模块和子模块解算模块三部分。其中,桥臂历史项电流解算模块和桥臂电流解算模块是桥臂级流水线结构,子模块解算模块是子模块级流水线结构。

图4 MMC桥臂解算单元的硬件设计Fig.4 Hardware design for MMC bridge arm solving unit

2.2 MMC控制系统仿真设计

对于多端MMC的控制系统仿真,由于不同MMC的控制器所采用的控制策略往往不同,难以运用流水线形式进行求解。同时,考虑到多端MMC系统中存在多个MMC控制器,且每个控制器的求解规模均较为庞大,为保证μs级实时仿真,本文采用并行方式对不同MMC的控制器进行求解。图3的控制系统求解部分给出了典型的MMC控制器的硬件设计,不同于采用节点分析法对电气系统进行求解,控制器中的比较器、坐标变换等各种控制元件都是以输入输出关系来建模的,可以根据所有控制元件的输入输出关系顺序求解得到各元件的输出。

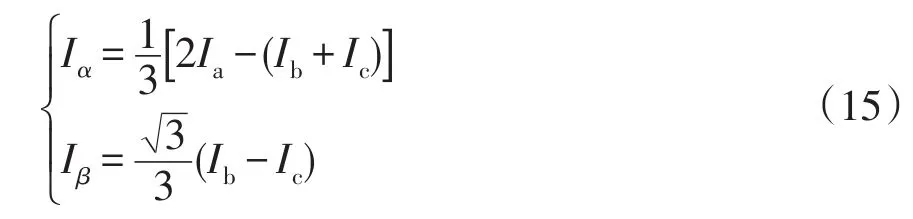

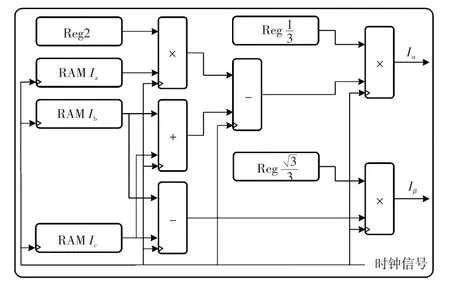

以式(15)所示的克拉克变换为例进行说明,其硬件设计如图5所示。基于运算环节间的顺序求解关系,逐步执行每个运算操作,便可实现对整个控制模块的实时解算[16]。对于控制器中的反馈环节,通过插入一个步长进行延迟处理。考虑到MMC控制器中的反馈环节数量有限,同时实时仿真步长较小,因此这种延迟处理方式是合适的。

图5 克拉克变换模块的硬件设计Fig.5 Hardware design for Clark transformation module

3 算例测试与验证

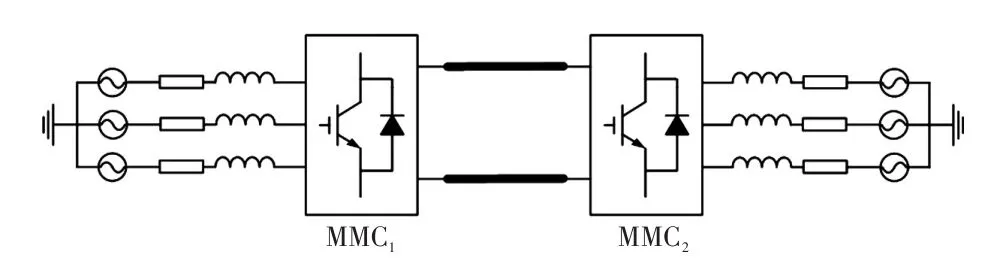

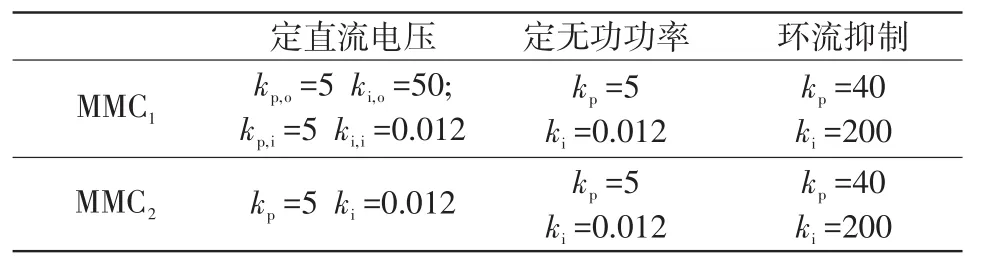

为验证所提出的MMC高效实时仿真模型的正确性和有效性,本文在开发的MMC实时仿真器和PSCAD∕EMTDC中分别搭建了如图6所示的双端25电平测试系统,其中,MMC1和MMC2均采用半桥型子模块拓扑。整个系统的运行参数如下:交流系统线电压有效值为3.3 kV,交流系统等效电阻为1 Ω,交流系统等效电感为0.03 mH,桥臂电感为30 mH,子模块电容为4.838 mF,直流电压基准值为5 kV,传输线电阻为0.5 Ω。MMC1采用定直流电压和定无功控制,MMC2采用定有功和定无功控制,环流抑制及双环控制参数见附录表A1。

图6 25电平双端MMC测试系统Fig.6 25-level two-terminal MMC test system

3.1 仿真精度

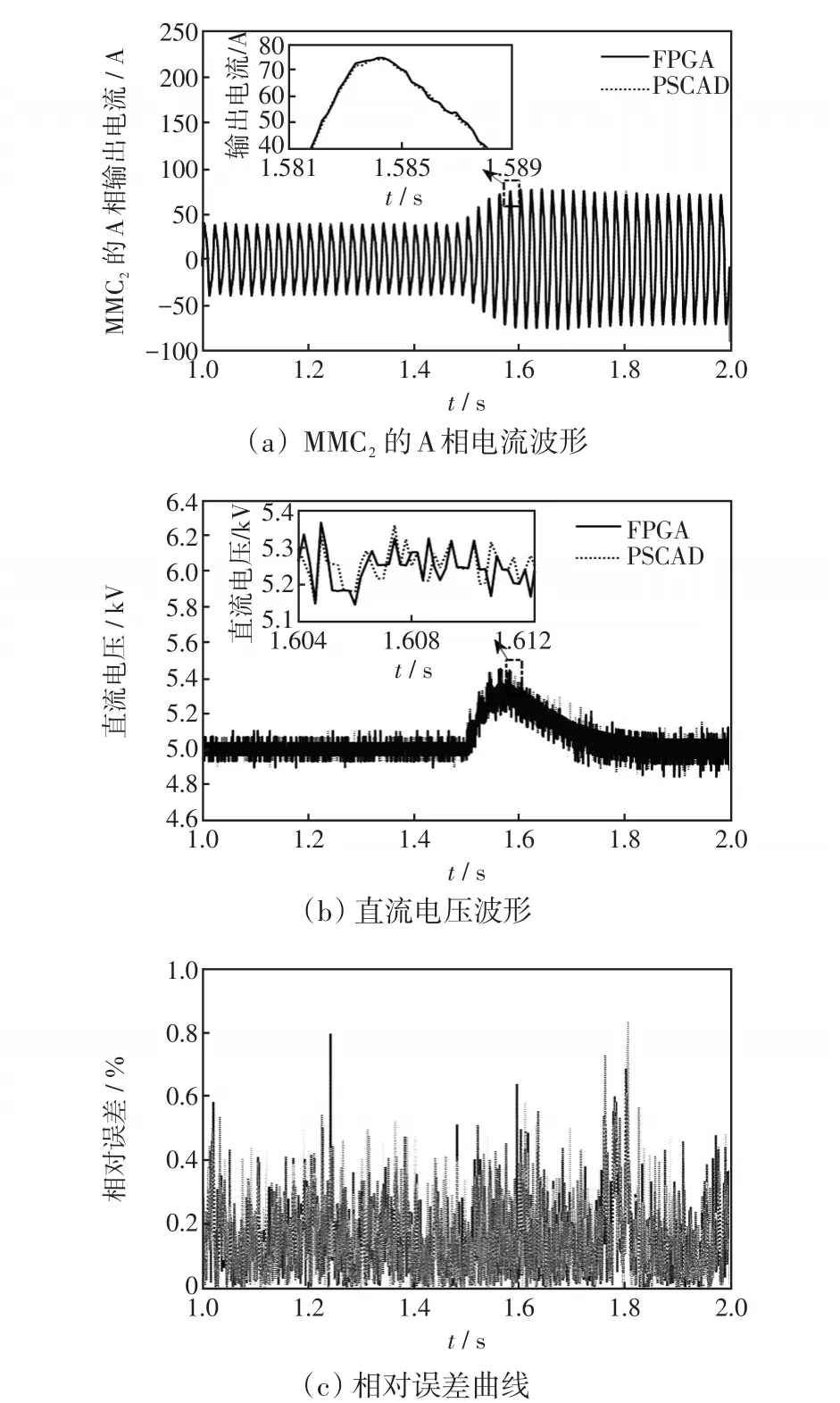

针对图6所示的双端MMC系统,设置仿真场景为:MMC1传送容量在1.5 s时由0.15 MW增大为0.3 MW。设置MMC实时仿真器的仿真步长为10 μs,并与PSCAD∕EMTDC 1 μs仿真步长下的结果进行比对。MMC2的A相输出电流与系统直流侧电压的波形如图 7(a)和图 7(b)所示,MMC2的A相输出电流的相对误差曲线如图7(c)所示。从仿真结果来看,MMC实时仿真器与PSCAD∕EM⁃TDC的仿真结果基本一致,两者相对误差在0.8%以下,验证了本文所提模型和硬件设计的正确性与有效性。

图7 MMC测试算例的仿真结果Fig.7 Simulation results of MMC test case

3.2 资源消耗

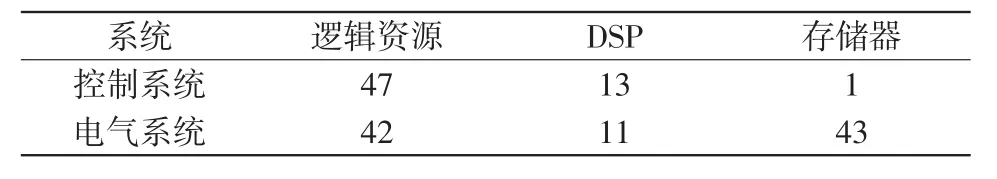

表1给出了MMC测试系统在FPGA中资源占用的情况。从表中可以看出,虽然电气元件的数量较多,但是电气系统占用的逻辑资源比控制系统更少,这是因为FPGA对各种电气元件的求解是以流水线形式实现的,而MMC换流站的控制器相对复杂,对两端换流站控制器的并行建模占用了更多资源。虽然MMC系统整体消耗了89%的逻辑资源,但由于FPGA上的部分运算任务可由DSP来完成[16],因此通过改变运算器的求解模式,可以有效扩大MMC实时仿真器的求解规模。

表1 MMC测试算例的资源占用情况Tab.1 Computational resource utilization in the MMC test case %

4 结语

本文结合MMC系统快速实时仿真的工程需求,提出了一种基于FPGA的MMC高效实时仿真模型。通过对桥臂进行戴维南等效外加电压补偿策略,有效避免了开关器件频繁切换导致的系统节点导纳矩阵更新,提高了实时仿真效率。进一步的,本文基于FPGA开发了流水线与并行计算深度融合的MMC实时仿真硬件平台,并针对25电平双端MMC系统开展了仿真测试,验证了模型的数值精度与平台设计的正确性。本文提出的基于FPGA的MMC模型具有通用性,可为大规模MMC系统的实时仿真提供解决思路。

附录A

表A1 双端MMC测试系统控制参数Tab.A1 Control parameters of two-terminal MMC test system