多核DSP软件调试环境研究与设计

王 品,于 莹,苗政民,贺红卫

(1.中国兵器科学研究院,北京 100089;2.中国航天科工集团第二研究院706所,北京 100039)

0 引 言

数字信号处理器(digital signal processor,DSP)具有灵活、稳定、重复性好、可大规模集成和易于实时实现等优点,被广泛应用于语音、通信、图像处理、声纳、生物医学仪器等诸多领域,在防空反导、机动突击、火力打击、光电侦察、指挥控制等各类武器装备中也发挥着重要作用[1]。

多核技术是提升处理器计算能力的重要途径, 随

着武器装备嵌入式系统向自主化、智能化、小型化、低功耗方向发展,对高精度、高性能和安全可控计算需求不断提高,自主多核处理器在装备研制中得到越来越广泛的应用。

目前,国内在核心电子器件领域的技术水平有了长足进步,已经研制出多款多核处理器,对相应的软件开发调试环境提出了迫切需求。提供包括仿真器在内的、与处理器相配套的软件调试环境,是自主多核处理器能够推广应用与深入发展的前提[2]。

1 远程调试原理与远程串行协议

1.1 嵌入式系统远程调试原理

相对于通用计算机,嵌入式系统的软硬件资源有限,通常无法完成本地自主调试,需要借助软硬件资源丰富的通用计算机,使用远程调试的方式进行软件调试[3]。

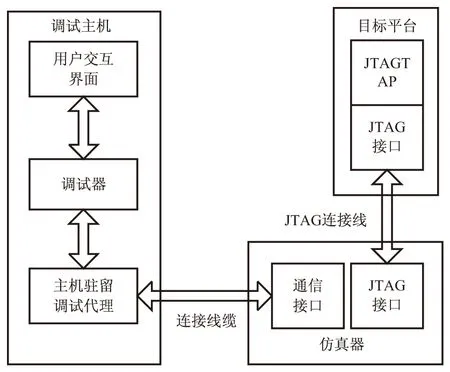

一个典型的嵌入式软件远程调试系统包括三个部分:调试主机、仿真器(调试协议转换器)和目标平台。调试主机一般为通用计算机,通过某种接口(如USB接口、网口、并口)与仿真器相连,仿真器通过JTAG接口连接目标平台,以此达到调试主机与目标平台进行调试信息交互的目的。调试主机运行调试器(如GDB)和调试代理软件,并为开发调试人员提供图形化操作和观察界面[4]。

远程调试系统组成如图1所示。

图1 远程调试系统组成

与本地调试相比,远程调试具有以下特点[5]:

(1)调试环境和被调试程序运行在不同的计算机上,通过某种通信方式将调试主机和目标平台相连,避开了目标平台上软硬件资源不足的限制,为用户提供强大的调试功能。

(2)目标平台无需操作系统支持。目标平台上即使运行操作系统,也主要是用于嵌入式应用的支撑,而不是用于目标平台的软件开发调试环境。

(3)本地调试只能调试相同指令集的程序,而远程调试可以调试与主机不同指令集的程序,这一特点也被称为交叉调试。

(4)由于调试环境和被调试程序的分离,不可避免地引入通信开销,对调试效率产生一定影响。

1.2 GDB远程串行协议

GDB是GNU开源组织发布的源码级调试器,支持多种处理器架构和编程语言,在调试代理的配合下,实现断点、单步执行、查看变量、查看寄存器、查看内存、查看堆栈等远程调试功能[6]。

GDB与调试代理通过远程串行协议(remote serial protocol,RSP)实现调试信息交互。RSP是一种基于ASCII码字符的通信协议,包括客户端(RSP client)和服务器端(RSP server),通常以GDB作为客户端,以调试代理作为服务器端,两者可以位于相同或不同的计算机上,通过网络Socket或RS232串口等方式通信。

RSP以数据包的形式传输数据,一个数据包包含数据信息和校验码两个部分。数据信息是一串ASCII码字符,以“$”字符作为起始标志,以“#”字符作为结束标志;数据信息后面跟随长度为16位的校验码,该校验码的值是数据信息中所有字符的ASCII码数值相加后除以256的余数,用2个十六进制字符表示。

接收方接收到完整的数据包后,使用校验码对数据信息进行校验,如果接收到的数据信息校验计算无误,返回“+”字符通知发送方数据包接收完成;如果校验出错,则返回“-”字符,通知发送方重新发送。发送方通过接收方返回的响应字符判断数据包发送是否成功。

如果调试代理暂不支持某个RSP调试指令,可以返回字符串“$#00”通知GDB,GDB会尝试使用其他RSP调试指令来代替不支持的调试指令完成同样的功能。然而,要实现GDB的调试功能,调试代理必须支持读寄存器的值(g)、修改寄存器的值(G)、读内存的值(m)、修改内存的值(M)、恢复运行(c)、单步执行(s)等RSP调试指令[7]。

2 JTAG标准

IEEE 1149.1标准由联合测试行动组(joint test action group,JTAG)提出,因此也被称为JTAG标准。JTAG标准最初用于芯片测试,现在也常用于对芯片上的软件进行调试。

JTAG标准中提出了边界扫描(boundary-scan)概念,其基本思想是在芯片的输入输出管脚上放置一个移位寄存器,称为边界扫描寄存器单元(boundary-scan register cell)。芯片正常运行时,这些边界扫描寄存器单元对芯片来说是透明的,不产生任何影响;当芯片处于测试状态时,边界扫描寄存器单元将芯片和外围的输入输出隔离,芯片的输入管脚可以通过与之相连的边界扫描寄存器单元把数据加载到该管脚中去,输出管脚可以通过与之相连的边界扫描寄存器单元“捕获(capture)”该管脚上的输出信号。

此外,通过边界扫描寄存器单元的相互连接,在芯片的周围形成一条边界扫描链(boundary-scan chain),在适当的时钟信号和控制信号驱动下,测试数据可以在边界扫描链上串行输入和输出。通过边界扫描寄存器单元和边界扫描链,能够对芯片的输入输出信号进行观察和控制,实现芯片测试和软件调试功能。一种芯片可以同时提供几条独立的边界扫描链,以满足不同的测试要求。

在JTAG标准中,定义了两类寄存器:数据寄存器(data register,DR)和指令寄存器(instruction register,IR)。边界扫描链即是一种重要的数据寄存器,用于控制和观察芯片的输入输出;IR用来实现对DR的控制,例如在芯片可供选择的全部边界扫描链中,通过IR指定一条边界扫描链作为访问对象[8]。

JTAG设备内部定义了一个状态机,称为TAP控制器。TAP控制器的状态通过TCK和TMS两个输入引脚进行控制,通过TAP控制器的状态变化,完成JTAG指令寄存器的输入和数据寄存器的输入输出,从而对芯片内部的处理器和外设进行控制和状态获取,在调试主机和仿真器软件的配合下,实现调试功能。标准的JTAG接口必须至少具有TCK、TDI、TDO和TMS四个引脚,其中TCK为TAP控制器提供时钟信号驱动,TMS控制TAP控制器的状态转换,TDI为数据输入引脚,TDO为数据输出引脚。此外,还有一个可选引脚RST,用于JTAG设备的状态复位[9]。

3 多核DSP调试环境设计方案

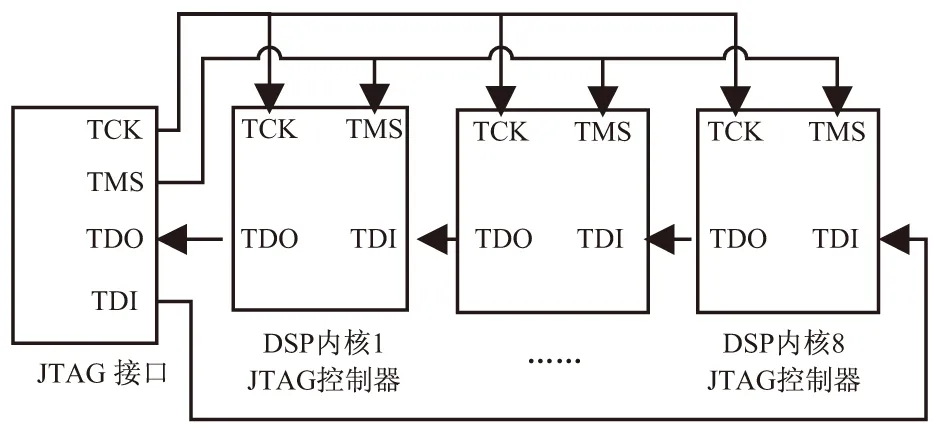

调试环境的目标平台为“核高基”国家科技重大专项支持的自主同构8核DSP。为了节约片上资源,将8个DSP内核中的JTAG控制器用菊花链(daisy chain)的方式连接起来,通过一个JTAG接口进行控制,如图2所示。

图2 目标平台JTAG连接

为了对这一设计进行支持,每个DSP内核的JTAG控制器都支持bypass指令。当某个DSP内核不是要调试的目标内核时,通过bypass指令,将位数为1的bypass寄存器连接在数据移入接口TDI和数据移出接口TDO之间,为数据移入移出提供一条长度最短的通过路径,以便调试数据快速地通过该DSP内核,到达目标DSP内核或调试主机[10]。

目标平台设计了自主的调试协议,无法使用现有的任何一种软件开发环境进行软件调试。该文针对目标平台的特点和调试协议,提出了一种调试环境设计方案。调试环境交互界面选择安装CDT插件的ECLIPSE平台,主要功能是提供友好的开发调试界面,接收用户调试命令输入,并显示调试结果,如目标机寄存器内容、内存内容、堆栈内容及断点信息等;采用GDB作为调试器,ECLIPSE平台集成针对DSP编译形成的GDB,ECLIPSE平台与GDB通过标准的Machine Interface(MI)协议通讯[11];调试主机驻留唯一的调试代理软件,调试代理通过8个线程使用8个端口分别与8个调试器建立连接,利用信号量解决通过单一JTAG接口访问8核DSP的互斥问题;调试代理利用调试主机的USB接口和仿真器进行通信。仿真器驻留8核DSP调试协议解析程序,该程序作为宿主机调试代理和被调试程序之间的媒介存在[12]。

用户通过ECLIPSE平台输入调试命令,ECLIPSE平台根据当前处于活动状态的工程,区分输入命令的目标平台,将命令转换为若干MI协议指令,发送给相应GDB,GDB将MI协议指令转换为若干RSP指令,通过Socket连接发送给调试代理,调试代理根据接收到指令的线程区分指令的目标内核,将目标内核信息添加到指令中,封装成为多核调试协议指令,通过USB接口发送给仿真器软件;仿真器软件接收多核调试指令,根据指令中的目标内核信息,区分指令对应的内核,将指令解析为指定DSP内核的调试指令+其余7个DSP内核的bypass指令,按照JTAG状态机的时序要求,通过GPIO端口将解析后的指令数据扫描到目标平台中,同时以移位方式获取返回结果;最后仿真器将调试结果通过USB接口发送给调试主机,经ECLIPSE解析后以图形化方式呈现给用户[13]。整个远程调试系统结构如图3所示。

图3 多核DSP远程调试系统结构

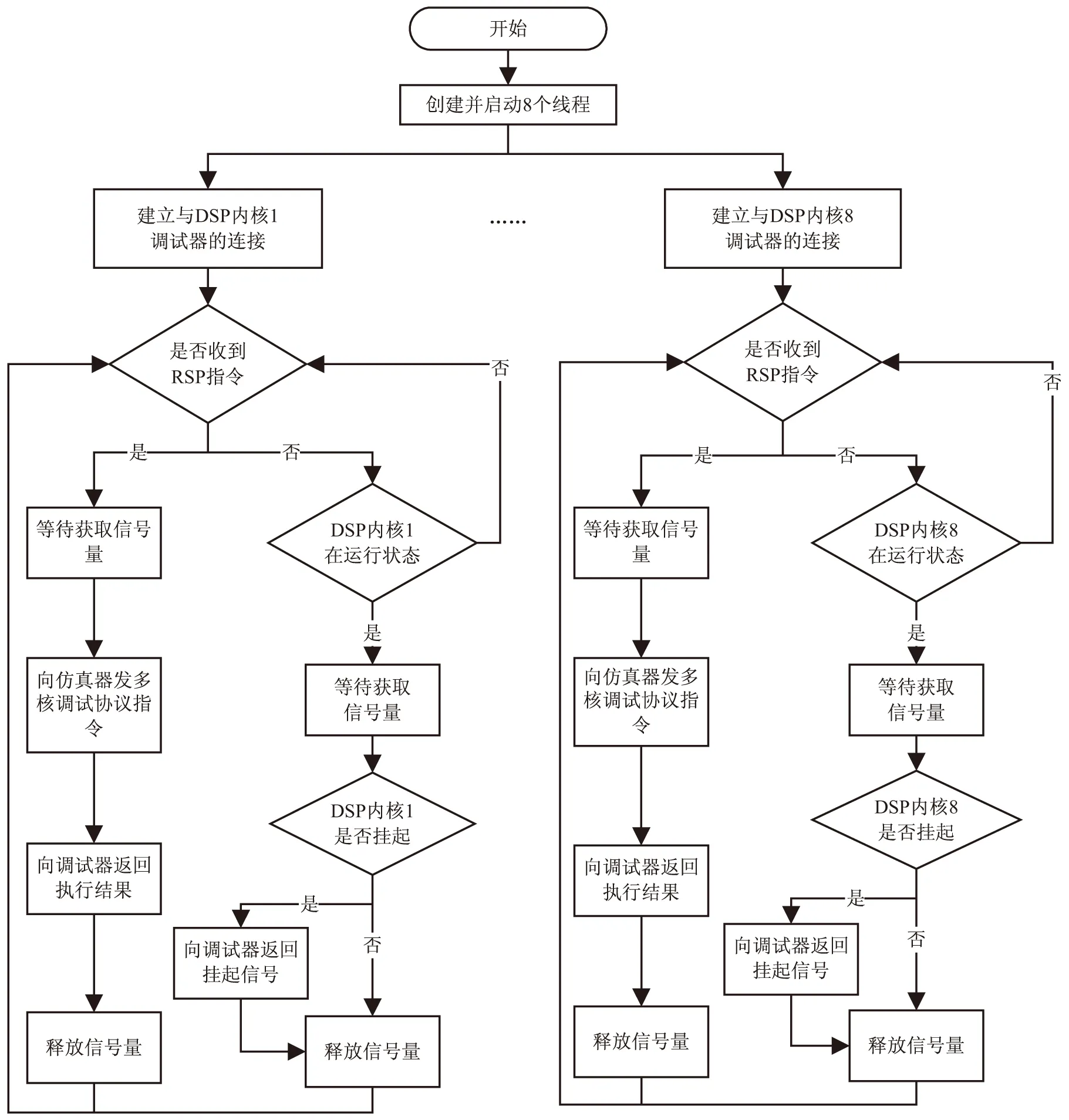

4 调试代理软件设计

根据多核DSP调试环境设计方案,调试代理创建并启动8个线程,使用8个端口分别与面向每个DSP内核的GDB建立Socket连接。其中一个连接接收到完整的RSP调试指令后,将其转换为相应的多核调试协议指令。为避免与其余内核的调试相冲突,需申请全局信号量,获取到全局信号量后,通过USB接口向仿真器发送多核调试协议指令,等待仿真器软件返回执行结果;接收到执行结果后,将结果封装为RSP数据包,通过Socket连接返回给相应的GDB;最后释放全局信号量,一条RSP指令执行完毕,等待接收下一条GDB发送的RSP指令。

DSP内核可能由于断点、异常等原因,由运行状态转变为挂起状态。调试代理软件通过内部变量记录每个内核的状态,如果一个连接没有接收到RSP指令,还应判断相应内核是否处于运行状态,如果内核处于运行状态,则需获取全局信号量,通过USB接口向仿真器发送内核状态查询指令,如果该内核已经转变为挂起状态,调试代理主动向GDB发送内核已挂起信号,最后释放全局信号量。

其执行流程如图4所示。

图4 调试代理执行流程

5 仿真器设计

5.1 硬件设计

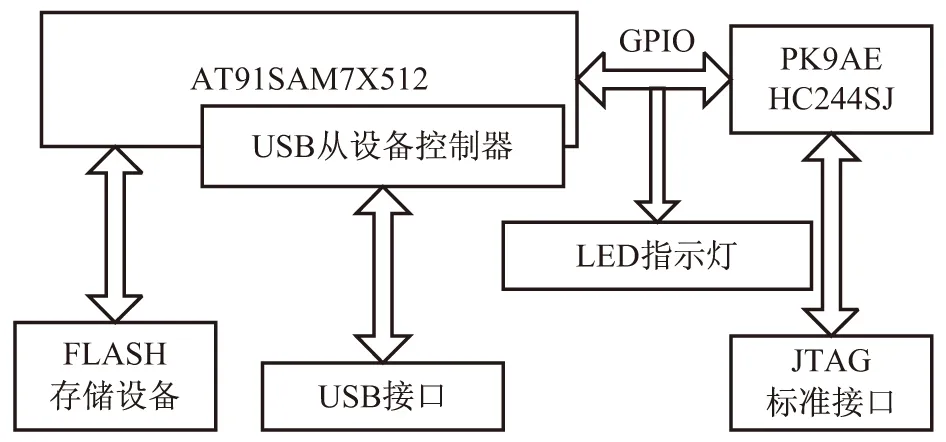

选用ARM架构AT91SAM7X512处理器作为仿真器的主控芯片,利用其内部集成的USB 2.0全速设备端口作为与调试主机连接的USB接口。主控芯片引出5个GPIO引脚,与IEEE1149.1标准中的TDI、TDO、TMS、TCK、RST五个接口信号相对应,通过缓冲处理芯片HC244SJ与目标平台对外引出的标准JTAG接口连接。控制芯片外接3个LED指示灯,分别与TDI、TDO及RST接口对应的GPIO引脚串联,当JTAG接口有信号传输时,相应的LED灯就会闪烁,起到指示作用,以便实时观察调试过程中仿真器与目标平台之间的通信过程。仿真器硬件设计如图5所示。

图5 仿真器的硬件设计

仿真器软件经烧写后存储在FLASH中。为了提高仿真器的调试速度,将仿真器软件搬移到SRAM中运行,设计了单独的启动引导程序(BootLoader)。BootLoader同样烧写在FLASH中,是仿真器加电后执行的第一段代码,在完成CPU和相关硬件的初始化之后,再将仿真器软件所在的FLASH地址的内容,复制到SRAM中,然后跳转到仿真器软件程序的入口点地址,将仿真器控制权交给仿真器软件[14]。

5.2 软件设计

仿真器软件主要包括USB端点中断处理和调试协议解析处理两个功能模块。

USB端点中断处理模块通过对端点中断的处理,将发送缓冲区的数据发送到调试主机,将从调试主机收到的数据写入接收缓冲区;调试协议解析处理模块完成多核调试指令的接收、解析和处理,JTAG状态机的驱动,以及DSP调试协议的实现等仿真器的核心功能。

5.2.1 USB端点中断处理

仿真器作为USB设备端,与调试主机通过USB接口连接,遵循USB主从通信协议。每一个USB设备在正常工作前必须完成主机对它的配置过程,即总线枚举。USB设备在总线上共有六种状态:接入态、加电态、默认态、地址态、配置态和挂起态。当调试主机与仿真器连接后,开始通过端点中断进行设备的总线枚举过程,仿真器完成总线枚举后,从配置态进入挂起态,等待来自调试主机的多核调试协议指令。

在USB设备端存在以下几类中断:帧起始中断、设备恢复中断、设备挂起中断和端点中断,来自调试主机的指令引起的中断是端点中断。端点是USB主机和设备的数据流终点,每个端点仅支持单一方向的数据流,按照数据流方向分为输入端点和输出端点,来自主机的数据流止于设备上的输出端点,发往主机的数据流则始于设备上的输入端点[15-16]。

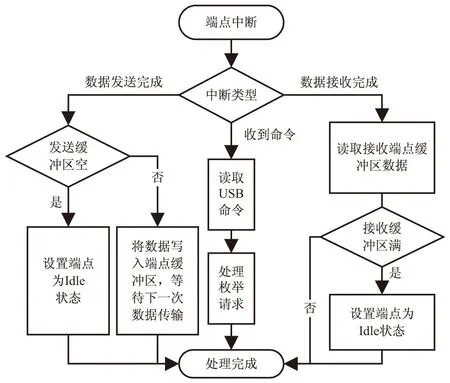

图6为端点中断处理流程。

图6 仿真器端点中断处理流程

根据引起中断的原因,端点中断又分为数据包接收中断、数据包发送完成中断和SETUP命令包接收中断,通过USB设备控制器的控制状态寄存器来区分中断类型。如果中断类型为数据包接收中断,说明从调试主机收到了一个数据包,此时应将数据包放入接收缓冲区,判断是否还有要接收的数据,如果已接收数据的数量不小于预期接收数据数量,说明本次数据接收任务已完成,将输出端点中断禁用,设置数据接收完成标识变量,通知主程序数据接收完成。如果中断类型为数据包发送中断,说明上一个数据包发送已完成,此时应判断发送缓冲区中是否还有数据需要发送,如果有,则将数据加入到发送队列;如果没有数据要发送,说明本次数据发送任务已完成,将输入端点中断禁用,设置数据发送完成标识变量,通知主程序数据发送完成。如果中断类型为SETUP命令包接收中断,说明接收到主机的SETUP命令,SETUP命令主要用于USB主机对设备进行配置和控制,例如总线枚举等,不涉及仿真器核心功能的实现。

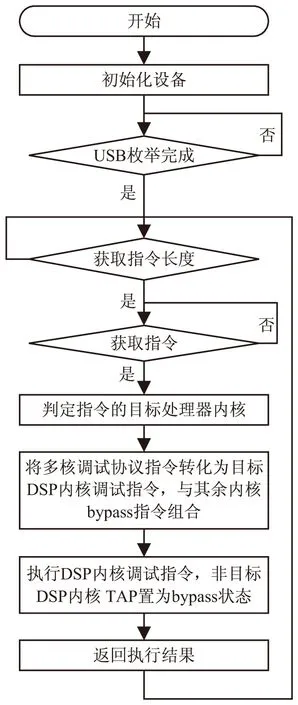

5.2.2 调试协议解析处理

调试协议解析处理模块是仿真器软件的主程序,其处理流程如图7所示。在完成USB和GPIO等设备初始化与总线枚举后,仿真器与调试代理进行通信,等待接收并执行多核调试协议指令。调试代理先发送2个字节的指令长度,然后发送指令的内容。仿真器通过端点中断接收到指令长度后开始等待接收此长度的指令内容。接收完毕后对指令进行解析,识别指令的目标内核,将多核调试协议指令转化为目标DSP内核调试指令,与其余内核的bypass指令进行组合,通过TDI引脚按照TAP状态机的时序要求移入内核执行。DSP内核调试指令执行完成后,仿真器将从TDO引脚移出的处理结果返回给调试代理,一条多核调试协议指令执行完毕,等待接收下一条调试代理发送的指令。

图7 仿真器软件流程

6 结束语

该文提出的面向自主8核DSP调试环境的设计方案,解决了目标平台缺乏配套软件调试手段的实际问题。方案采用自主研发的软硬件和开源软件,具有功能完备、性能良好、安全可控、灵活易扩展等优点。该方案能够集成GCC等编译链接工具,结合ECLIPSE平台自身的功能,即可构成一个图形化的软件集成开发环境,实现一体化的工程管理、编译链接和远程调试功能,对其他自主同构或异构多核处理器软件开发环境的设计具有一定的参考价值。