一种用于安全芯片的无线自毁电路*

范伟力,胡杨川,朱 翔

(1.成都三零嘉微电子有限公司,四川 成都 610041;2.保密通信重点实验室,四川 成都 610041)

0 引言

当前,信息技术已经逐渐被应用于社会各个领域,深刻影响着人类的各项活动,也给信息安全带来了严峻挑战。安全芯片作为信息系统安全性的基础保障手段,是确保信息系统安全性的基础元器件和构建安全环境的重要支撑。正因为如此,安全芯片自身的安全对整个信息系统至关重要,也一直是相关研究人员关注的焦点。目前,针对安全芯片的各种攻击方法和手段在研究中不断被提出和深入发展,对安全芯片的威胁越来越大,因此对安全芯片防护技术的研究任重道远[1]。

根据对安全芯片攻击侵入程度的不同,攻击手段可以分为侵入式攻击(Invasive Attacks)、非侵入式攻击(Non-invasive Attacks)和半侵入式攻击(Semi-Invasive Attacks)3 种[2]。

针对以上3 种攻击,常见安全芯片中均设计有相应的防护电路,尽可能提高攻击者的攻击难度和时间成本。为提升高安全领域中安全芯片的防护能力,可在安全芯片中加入自毁电路设计,在安全芯片离开安全环境处于失控状态一定时间后启用自毁电路,以物理方式彻底破坏芯片中的关键电路和敏感数据,从而实现更高的安全性。

本文提出了一种用于安全芯片的无线自毁电路,可在安全芯片离开安全可控的工作环境后,自动启动安全芯片的物理自毁操作。

1 无线自毁原理

图1 是安全芯片的无线自毁原理示意图。安全芯片上集成有无线自毁电路和片上炸药。无线自毁电路的天线集成在芯片封装管壳上。安全芯片无线管控端部署在芯片所在的主机壳内或可通过电磁波覆盖芯片的邻近区域。

正常情况下,安全芯片处于无线管控端电磁波覆盖范围内,其无线自毁电路周期性地自动和无线管控端进行认证。当安全芯片离开管控区域后,无线管控电路因无法完成认证,判定安全芯片已失控并输出自毁信号引爆片上炸药,从而完成安全芯片物理自毁操作。

图1 安全芯片的无线自毁原理

2 总体设计

安全芯片上的无线自毁电路和安全芯片无线管控端之间采用800/900 MHz 射频信号通信,无线信道的物理层和访问控制层参考国标《信息技术射频识别800/900 MHz 空中接口协议》(GB/T 29768—2013),命令格式为自定义[3]。

图2 是无线自毁电路的总体架构,由控制子电路、调制/解调子电路、存储器、认证子电路、随机数子电路、使能状态熔丝、时钟子电路、上电复位子电路以及天线等部分组成。控制子电路负责控制、调度其他子电路;调制/解调子电路接收射频信号完成解调以及发送射频信号的调制;存储器存储工作需要的配置数据;认证子电路负责认证数据包的解析和封包;随机数子电路在认证流程和自毁信号产生过程中使用;使能状态熔丝用于使能无线自毁电路;时钟子电路和上电复位子电路产生无线自毁电路的工作时钟和复位信号。

图2 无线自毁电路总体架构

无线自毁电路的工作流程如图3 所示。当芯片上电后,无线自毁电路的上电复位子电路完成全电路的复位。无线自毁电路检查使能状态位是否有效,若有效进入下一工作流程,且计时器开始计时,否则电路停止工作。计时器计满一定时间后,无线自毁电路主动发起和无线管控端之间的认证。若认证通过,认证失败计数器清零并返回等待计时状态,等待下一次认证;若认证失败,认证失败计数器加1,并判断认证失败次数是否超过设定阈值。当失败次数未超过设定阈值,无线自毁电路返回等待计时状态;否则,输出自毁信号。

图3 无线自毁电路工作流程

为防止攻击方关闭无线自毁电路使能,使能状态位由熔丝实现。在安全芯片完成密码资源初装并放置在正常工作区域后,再熔断熔丝激活无线自毁功能。

3 电路设计实现

3.1 解调/调制子电路设计

按照总体设计要求,解调/调制子电路应支持国标《信息技术射频识别800/900 MHz 空中接口协议》(GB/T 29768—2013)中规定的ASK 调制方式。

解调/调制子电路结构如图4 所示。无线自毁电路采用反向散射调制原理返回数据到无线管控端,M1和C1完成调制功能。MODIN 信号通过控制M1的通断来控制电容C1是否并联至芯片的输入端。解调/调制子电路通过这种方式改变了芯片的输入阻抗,达到反向散射调制的目的[4]。

C2、C3、C4、C5和D1、D2、D3、D4构成的二级迪克逊电荷泵完成包络检测功能,R1为电荷泵负载电阻,检测出的包络信号再通过R2和C6组成的低通滤波器过滤掉高频信号。包络信号经过由C7和M2构成的微分器,在包络上升时,微分器产生一个正的阶跃,在包络下降时产生负阶跃。经过微分器后的信号幅度较为稳定。这种设计不仅使比较器对信号强度的变化有很强的适应性,而且会对不同调制深度的信号表现出更好的灵敏度和可靠性。

图4 调制/解调子电路

C0和R0用于调整天线端口上的阻抗,便于匹配天线。

3.2 时钟子电路设计

为满足国标《信息技术射频识别800/900 MHz空中接口协议》的物理层定义要求,时钟子电路的频率典型值设计为1.28 MHz,且要求频率偏差小于±10%。

时钟子电路结构如图5 所示。基于功耗和精度的折中考虑,时钟子电路采用电流源控制的环形振荡器结构,通过调整电流源的电流大小和温度系数,达到降低时钟子电路功耗,并提升时钟精度的目的。

3.3 上电复位子电路

上电复位子电路结构如图6 所示。上电过程中,随着电源的升高,节点A 与节点B 的电压随之升高。节点B 的电压VB经过反相器的延迟输出后,产生节点D 的电压VD。VD与电源之间存在压差,且该压差也是晶体管MP10的Vgs。当该Vgs足够大时,晶体管MP10导通。电源通过导通的晶体管MP10为电容C2充电。当电容C2上的电压VE不断增大时,晶体管MN6开始导通,使得输出电压VF降低。由反相器反向后,电路的输出端产生了上电复位信号的上升沿。充电结束后,电容C2通过MN5放电,调节MN5的尺寸,使电容C2放电的速度比充电慢。当电容C2上的电压逐渐降低时,晶体管MN6进入截止状态,输出电压VF升高,此时电路的输出端得到了上电复位信号的下降沿。

图5 时钟子电路

图6 上电复位子电路

掉电过程中,随着VDD 电压的降低,A 点和B点电压被拉低,B点较A点之前变低。经过反相器后,C 点较D 点之前变高。当D 点变高时,E 点上的电容C2被放电。当VDD 达到地电位时,C 点和D 点被PMOS 钳位到Vthp电平,E 点电压被PMOS 钳位到2Vthp电平。由于MOS 器件的亚阈值导电特性,E 点电压还将进一步降低,直至达到地电位。

3.4 随机数子电路

随机数子电路结构如图7 所示。随机数产生采用振荡器采样原理,高频时钟使用已有的1.28 MHz时钟,在低频振荡器中引入电阻热噪声生成带噪声的低频时钟[5]。使用低频时钟对高频时钟进行采样产生随机数,低频时钟频率约30 kb/s,高/低频时钟比约40。

3.5 认证子电路

认证子电路的认证流程如图8 所示。当无线自毁电路上电复位完成后,由认证子电路发起认证,发送自身ID和随机数RN给管控设备。管控设备用根密钥RK和无线自毁电路ID产生对应认证密钥AK,管控设备使用AK加密RN,并将加密结果EAK(RN)发送给无线自毁电路。无线自毁电路收到管控设备发来的密文后,使用内置的认证密钥AK进行解密,得到RN’。无线自毁电路比较RN和RN’,若二者一致则认证通过,否则认证失败。认证过程采用SM7 轻量级分组算法。

图7 随机数子电路

图8 认证子电路认证流程

3.6 控制电路

图9 为控制电路结构图,由有限状态机、命令处理、命令返回、认证计数和自毁信号输出组成。有限状态机实现电路工作状态控制;命令处理模块完成空中接口命令的解析;命令返回模块完成空中接口返回数据的发送;认证计数模块完成认证失败计数,其溢出阈值可由用户根据安全策略进行配置;自毁信号输出模块用于产生触发芯片自毁的控制信号。

图9 控制电路

为防止攻击者切断自毁信号线破坏安全芯片的自毁功能,自毁信号采用9 bit 总线。产生原理如下:由随机数子电路产生8 bit 随机数RNG[7:0]对其进行按位异或运算得到结果^RNG[7:0];当未检测到安全芯片失控时,输出9 bit 自毁控制信号EN_SD[8:0]={^RNG[7:0],RNG[7:0]};当检测到安全芯片失控时,输出9 bit 自毁控制信号EN_SD[8:0]={~(^RNG[7:0]),RNG[7:0]}。自毁引爆电路接收到EN_SD[8:0]后,对其进行按位异或得到结果SD_RESULT。当SD_RESULT=1 时,自毁引爆电路启动。在后端设计时,使用底层金属走线连接EN_SD[8:0]信号,并进行乱序处理。

3.7 功能仿真

无线自毁电路采用SMIC 130 nm CMOS 工艺实现,使用华大九天的ALPS 仿真器对全电路网表进行晶体管级仿真。图10 是空中接口调制/解调数据波形,可见一次认证流程耗时约1 ms。

图11 是自毁信号输出波形,波形从上到下依次为自毁信号总线值和9 根输出线的波形。当连续认证失败次数超过设定阈值时,自毁信号输出值变为15C 和0B9,其按位异或结果均为1,代表自毁信号有效。

图10 空中接口调制/解调数据波形

图11 自毁信号输出波形

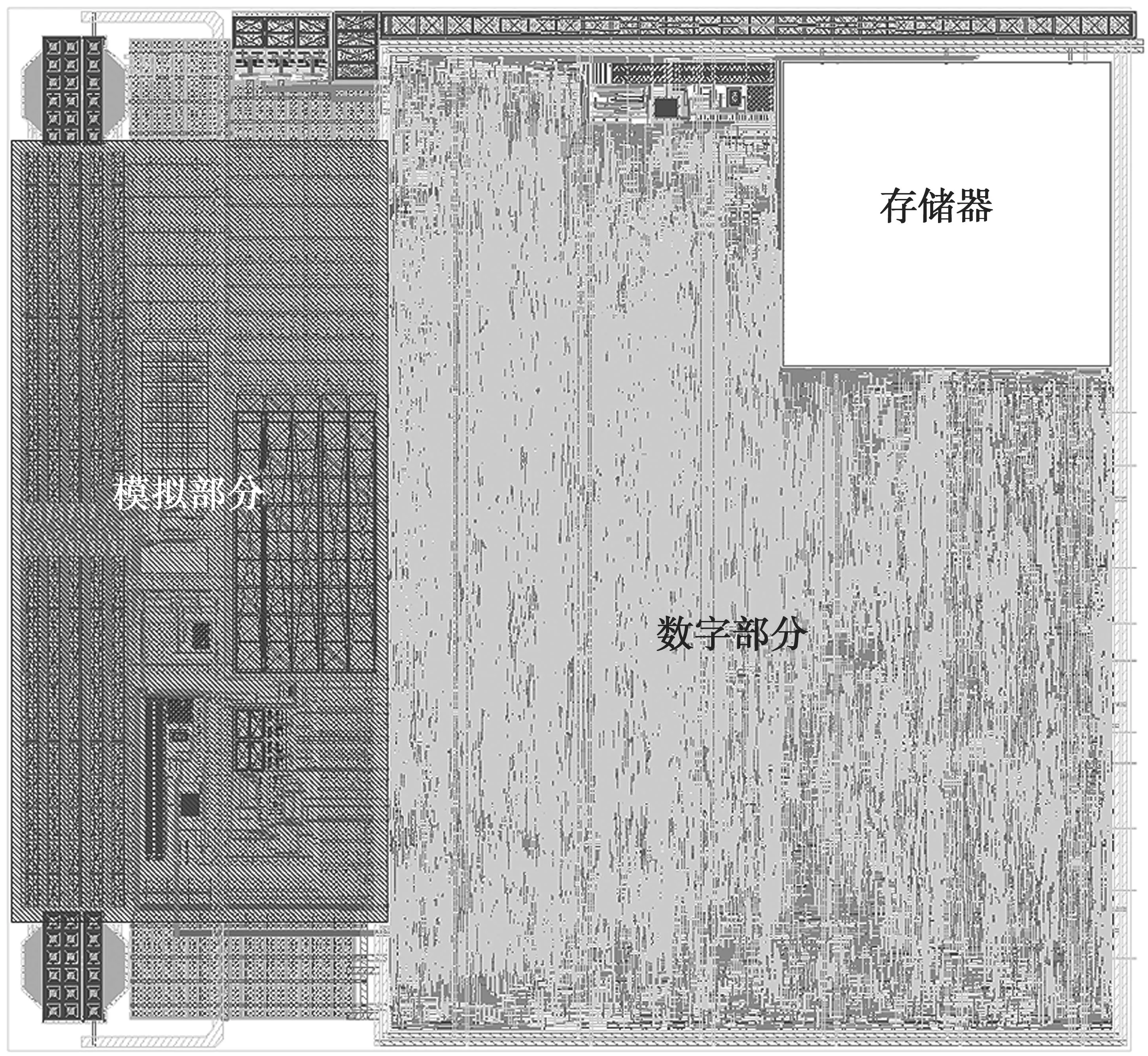

3.8 版图实现

无线自毁电路的版图采用SMIC 130 nm CMOS工艺实现,版图面积约为840 μm×900 μm,如图12 所示。版图中,模拟部分位于左侧位置,数字部分位于右侧位置,存储器位于右上角。左上角和左下角为两个天线PAD,右侧从上到下为电源、地、自毁信号输出和使能信号,其中自毁信号采用乱序排布,并使用最底层金属M1输出。无线自毁电路采用四层金属布线,建议安全芯片在集成无线自毁电路时,在其上部覆盖顶层金属进行保护。

图12 无线自毁电路版图

4 结语

本文提出的无线自毁电路,采用800/900 MHz射频信号实现和无线管控端之间的通信,无线信道的物理层和访问控制层参考国标《信息技术射频识别800/900 MHz 空中接口协议》(GB/T 29768—2013)。无线自毁电路可在安全芯片离开无线管控端覆盖的电磁环境后,自动启动安全芯片的物理自毁操作。无线自毁电路已采用SMIC 130 nm CMOS工艺实现,并可根据安全芯片的工艺需要进行工艺迁移。该电路在安全芯片处于失控情况下可引爆片上炸药,以物理方式彻底破坏安全芯片中的关键电路和敏感数据,大大提升了安全芯片的安全性。