用于流水线ADC的无采样保持运放前端电路

陈迪平 张仁梓 曹伦武 陈卓俊 曾健平

摘 要:为了降低流水线模数转换器功耗与提升输入信号范围,设计了一种无采样保持运放前端电路. 移除采样保持运放降低了功耗,并改进开关时序进一步降低电路功耗;同时改进传统开关电容比较器输入,使得模数转换器可达到0 ~ 3.3 V满电源电压的量化范围. 将设计的无采样保持运放前端电路应用在一款低功耗12位50 MS/s流水线模数转换器进行验证,采用0.18 μm 1P6M工艺进行流片,芯片面积为1.95 mm2. 测试结果表明:3.3 V电压下,采样率为50 MS/s、输入信号频率为5.03 MHz时,信噪失真比(SNDR)为64.67 dB,无杂散动态范围(SFDR)为72.9 dB,功耗为65 mW.

关键词:流水线模数转换器;无采样保持运放;孔径误差;开关电容比较器

中图分类号:TN495 文献标志码:A

Front-end Circuit without Sample-and-hold

Amplifier for Pipelined ADC

CHEN Diping1,ZHANG Renzi1?,CAO Lunwu2,CHEN Zhuojun1,ZENG Jianping1

(1. College of Physics and Microelectronics Science,Hunan University,Changsha 410082,China;

2. Hunan Advancechip Electronic Technology Company,Changsha 410205,China)

Abstract:A front-end circuit without Sample-and-Hold Amplifier(SHA) is presented for reducing power consumption and increasing input range of pipelined ADC. Removing Sample-and-Hold Amplifier and improving switching timing reduce the circuit power consumption,while improving the traditional switched-capacitor comparator inputs to make ADC achieve a 0-3.3V full supply voltage quantization range. The front-end circuit without Sample-and Hold Amplifier is verified in a low power 12 bit 50 MS/s pipelined ADC. The circuit is implemented in a 0.18 μm 1P6M process,and occupies a chip area of 1.95 mm2. The test results with a 5.03 MHz input wave under a sampling rate of 50 MS/s show that the ADC achieves a 64.67 dB signal-to-noise and distortion ratio(SNDR) as well as a 72.9 dB spurious-free dynamic range(SFDR),while it consumes the power consumption of 65 mW.

Key words:pipelined Analog to Digital Converter(ADC);Sample-and-Hold Amplifier(SHA)-less;aperture error;switched-capacitor comparator

高速高精度模數转换器(Analog to Digital Converter,ADC)是如今众多高性能数模混合电路系统中不可或缺的部分[1-4].随着工艺水平的提高以及便携式电子设备的兴起,高速低功耗ADC[5-6]也正成为研究热点. 常见的ADC有流水线型(Pipelined)[7-8]、逐次比较型(Successive Approximation Register,SAR)[9]、混合型(Pipelined-SAR)[10]、过采样型(Sigma Delta,Δ-Σ)[11]等,而Pipelined ADC因其较快的速度、较高的精度以及适中的功耗而被广泛应用.

为达到低功耗Pipelined ADC设计要求,研究者们提出了许多降低功耗方法,如运放共享技术[12]、无前端采样保持运放技术(Sample-and-Hold Amplifier-less,SHA-less)[13-14]等. 传统Pipelined ADC设计中,为使子ADC和余量增益电路(Multiplying Digital-to-Analog Converter,MDAC)两条路径传输信号一致,信号通过采样保持电路(Sample-and-Hold Amplifier,SHA)后才开始逐级量化. 由于SHA电路位于ADC最前端,为达到高速高精度目的,系统对SHA中运放的增益与带宽具有很高要求,从而消耗巨大功耗. 因此,降低Pipelined ADC功耗的一种有效方法是移除采样保持运放. SHA电路具有稳定两条信号路径一致性和电平转移功能,移除采样保持运放会带来孔径误差[14]及输入信号范围变小等问题. 因此,采用SHA-less电路,需要进一步优化设计.

本文设计了一种适用于低功耗高精度SHA-less Pipelined ADC的前端电路,改进开关时序减小首级ADC比较器导通时间来降低功耗和消除孔径误差,同时改进传统开关电容比较器输入,使得ADC可量化输入信号电平达到0~3.3 V满电源电压. 所设计的电路应用在一款中低端DSP芯片中的低功耗12位50MS_s_Pipelined ADC进行验证,采用0.18 μm 1P6M工艺进行电路设计仿真及流片,测试结果良好.

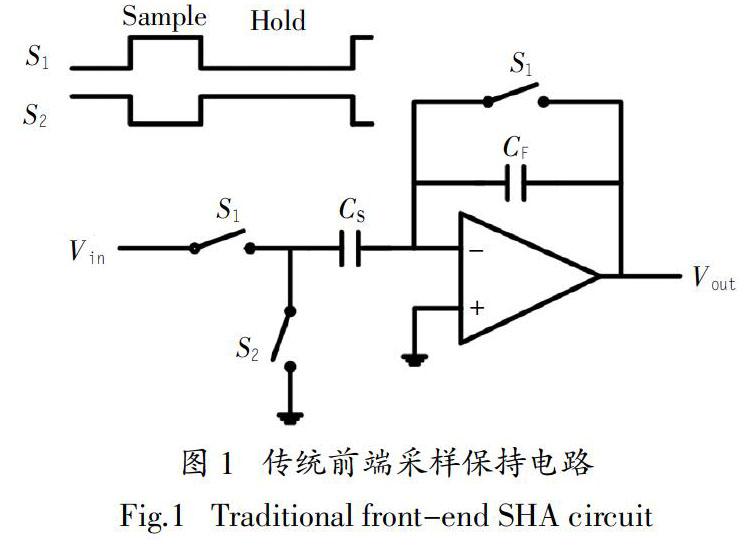

1 传统前端SHA电路

图1所示为传统前端SHA电路原理图. 采样相时,开关S1闭合,S2断开,采样电容CS对输入信号进行采样;保持相时,开关S1断开,S2闭合,电容CS上的电荷往反馈电容CF上进行转移,最终得到输出Vout = Vin CS /CF. 在下一次采样时刻到来前,输出将保持不变. 因此,在保持相,信号往首级子ADC与MDAC传输时,两条路径不会存在偏差. 同时,若输入信号电平超出首级ADC量化范围时,可以通过设置合理的CS /CF比值,将输入信号进行电平变换后再进行量化.

由于SHA电路位于Pipelined ADC最前端,因此系统对SHA电路中运放的增益与带宽具有很高要求,导致SHA电路消耗巨大功耗,通常占据整个系统功耗的30%[15]以上. 因此,在低功耗Pipelined ADC设计中,移除前端SHA电路中的运放显得很有必要. SHA-less的前端电路信号传输路径如图2所示,输入信号传输存在两条路径,一条为信号直接送入首级ADC进行量化,另一条为送入采样电路. 若两条通道时间常数不匹配,将会产生孔径误差,从而降低整个系统量化精度.

由式(1)和图3可知,ADC可量化的最大信号输入电平为ΔVREF = VREFP - VREFN. 增大ADC可量化的输入信号电平,只能增大基准电压VREFP、VREFN差值,但不能达到满电源电压输入. 考虑到Pipelined ADC由多级子ADC组成,若保持图3中电阻串阻值不变,增大基准电压VREFP - VREFN差值将会明显增加功耗,同时对基准电压VREFP、VREFN产生电路的电流驱动能力要求也增高,从而导致基准电压产生电路面积大幅增加;若增大电阻串阻值以降低功耗和基准电压产生电路的电流驱动能力,由图4所示保持相比较器等效输入可知,时间常数τ = Rep·VREFP、Co将会大幅增加,比较器工作速度降低,从而降低ADC量化速度. 因此,图3所示比较器电路不适合高输入信号电平的SHA-less Pipelined ADC.

2 SHA-less Pipelined ADC前端电路

图5为本文设计的SHA-less前端电路结构图,电路为全差分结构,为简化这里只给出单端电路图. 电路共有16个比较器,可实现4 bit首级子ADC功能. 图中给出了部分开关时序,ADC采样开关φ1在采样电容CS开关φs后导通,降低了比较器导通工作时间,进一步减小部分电路功耗. 因为采样时刻不一致产生的误差,可以通过两条采样路径阻抗不匹配误差进行抵消以达到数字逻辑可校准范围. 比较器改进输入可实现满电源电压输入,具体工作原理后面将做详细讨论.

2.1 孔径误差的消除

根据校正原理,总误差需满足式(2):

其中,总误差包括比较器输入失调、孔径误差、基准源误差等;VFS是ADC满输入量程;AV是MDAC增益. 本文设计中,ADC输入为满电源电压量程,即0~3.3 V;首级MDAC增益为8. 假设因为两条信号路径不匹配带来的孔径误差Verror_mismatch占总误差的一半,则可得:

Verror_mismatch < 51.56 mV (3)

图5给出的部分开关时序图,与传统开关时序不同,为了减少比较器导通时间以降低ADC功耗,比较器采样开关φ1在采样电容开关φS后导通. 此处引起的误差可以通过采样路径不匹配进行抵消. 假设输入信号为一正弦波:

Vin = A0 sin ωt (4)

采样电容CS和ADC分别在t1、t2时刻对输入信号进行采样,两条路径产生的延迟分别为τ1、τ2 . 因此产生的误差为:

Verror_mismatch ≌ A0 [sin ω(t1+τ1)-sin ω(t2+τ2)] (5)

输入正弦波信号在过零处,式(5)所示的误差将会呈现最大值:

Verror_mismatch_max ≌ A0 [sin ω(t1-t2)+sin ω(τ1-τ2)] (6)

通过合理设置开关φS和φ1尺寸,使得Δτ = τ1-τ2 = Rons CS - Ron1 CO与Δt = t1 - t2相抵消,以使误差最小. 其中,Rons、Ron1分别为开关φS和φ1的导通阻抗. 本设计通过不断提取参数进行后仿真来优化电路设计与版图匹配,使得在50 MS/s采样率下,输入正弦波频率达10 MHz时,孔径误差为11 mV,满足式(3)要求且有较大余量.

2.2 首级子ADC可量化输入信号电平的提升

由第1节的分析可知,采用SHA-less结构后,首级ADC能量化的最大输入信号电平将会变小. 如图5所示,本设计对传统电容开关比较器输入进行改进,通过设置合理的VREFP、VREFN值,可以使得ADC达到0 ~ 3.3 V的滿电源电压输入.

比较器输出如式(7)所示.

由式(7)可知,输入信号ΔVin = Vinp - Vinn,减去一个固定直流量ΔVREF = VREFP - VREFN后再与参考电压做比较,实现了输入信号电平变换的功能. 因此,合理设置VREFP、VREFN的值,可以实现ADC满电源电压的输入. 本设计中,Vrefp - Vrefn的取值为:

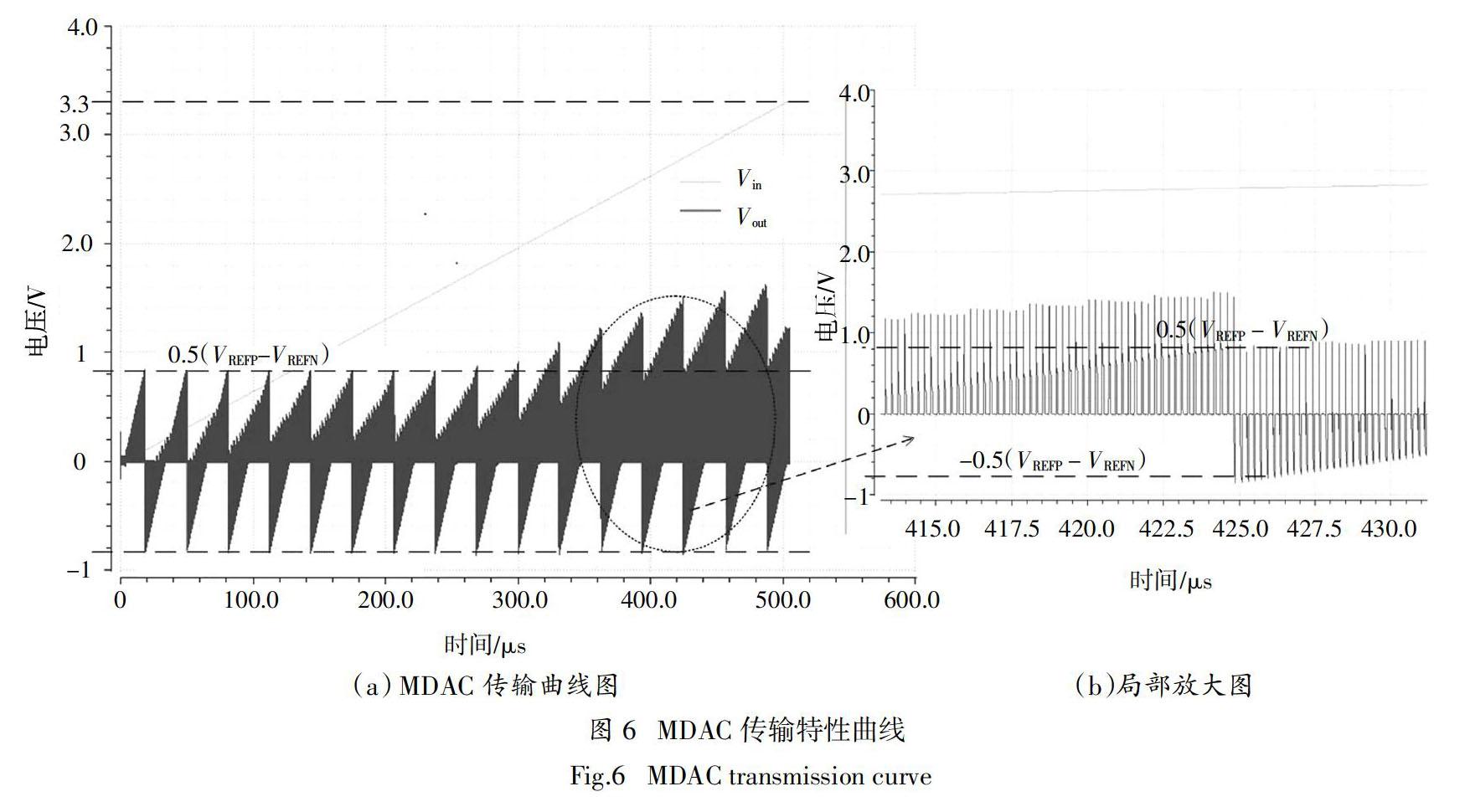

因此可得VREFP - VREFN = 1.65 V,结合电路设计的VREFP + VREFN共模值,便可确定VREFP、VREFN的值. 图6为0 ~ 3.3 V满幅输入时,运放输出的曲线图. 由图可以看出,ADC可以实现0 ~ 3.3 V满电源电压量化范围.

3 SHA-less前端电路应用及测试结果

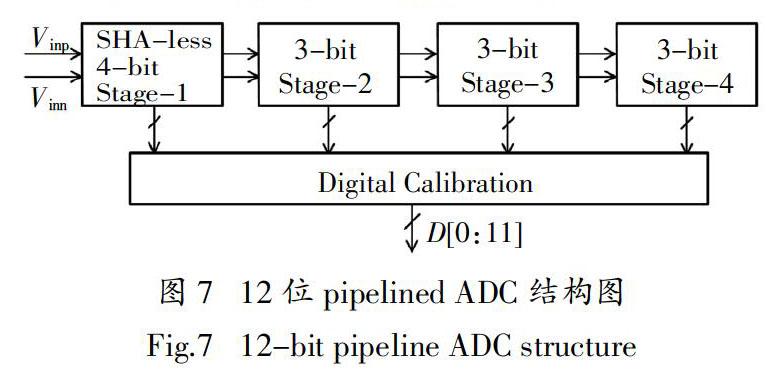

本文设计的SHA-less前端电路已成功应用于一款12位50 MS/s的pipelined ADC芯片中,结构图如图7所示. 12位50 MS/s的pipelined ADC采用4+3+3+3的四级流水结构,为降低ADC整体功耗,首级采用了本文设计的4bit SHA-less结构,电路0.18 μm 1P6M工艺进行设计及流片.

图8为芯片照片图,面积为1.95 mm2.

图9为ADC测试的线性度曲线,微分非线性(Differential NonLinearity,DNL)误差为-0.61/+0.61LSB,积分非线性(Integral NonLinearity INL)误差为-0.82/+0.7LSB.

图10显示了在3.3 V电源电压下,采样率为50 MS/s、输入信号为5.03 MHz时的测试FFT频谱图,信噪比(Signal to Noise Ratio,SNR)为65.03 dB,信噪失真比(Signal to Noise and Distoration Ratio,SNDR)为64.67 dB,无杂散动态范围(Spurious Free Dynamic Range,SFDR)为72.9 dB,整体功耗为65 mW. 功耗与具有采样保持运放的相似架构流水线ADC相比[3],降低了40%.

表1给出了文中所设计ADC与部分参考文献提出的ADC性能对比,可以看出本文设计具有较小的功耗与精度、面积以及最大的输入范围.

4 结 论

本文提供了一种适用于低功耗Pipelined ADC设计的无采样保持运放的前端电路. 改进采样开关时序减小了电路功耗,同时改进传统开关电容比较器输入,使得ADC可量化0~3.3 V满电源电压输入信号电平. 将所设计的SHA-less前端电路应用在一款12位50MS/s Pipelined ADC进行验证,采用0.18 μm 1P6M工艺进行流片,整体ADC面积为1.95 mm2,测试结果良好.

参考文献

[1] MOHAMED M Y,HEGAZI E,EI-NOZAHI M. A 0.35 mW 8-bit 140MS/s asynchronous hybrid ADC for low energy radio applications[C]// 2019 36th National Radio Science Conference. Piscataway: IEEE,2019:315—323.

[2] JEON B K,HONG S K,KWON O K. A low-power 12-Bit extended counting ADC without calibration for CMOS image sensors[J]. IEEE Transactions on Circuits and Systems II:Express Briefs,2018,65(7):824—828.

[3] MATHUR S,DAS M,TADEPARTHY,et al. A 115mW 12-bit 50 MSPS pipelined ADC[C]// 2002 IEEE International Symposium on Circuits and Systems. Piscataway:IEEE,2002:913—916.

[4] CHEN T,PENG L L,LI H B,et al. A 2-V 40-MS/s 14-bit pipelined ADC for CMOS image sensor[C]// 2015 IEEE 11th International Conference on ASIC. Piscataway:IEEE,2015:1—4.

[5] OHHATA K,HAYAKAWA D,SEWAKI K,et al. A 900-MHz,3.5-mW,8-bit pipelined subranging ADC combining flash ADC and TDC[J]. IEEE Transactions on Very Large Scale Integration(VLSI) Systems,2018,26(9):1777—1787.

[6] ZHOU Y,XU B W,CHIU Y. A 12-b 1-GS/s 31.5-mW time-interleaved SAR ADC with analog HPF-Assisted skew calibration and randomly sampling reference ADC[J]. IEEE Journal of Solid-State Circuits,2019,54(8):2207—2218.

[7] 陽辉,何怡刚,黄姣英. 0.25μm CMOS工艺10位150MHz流水线型ADC设计[J]. 湖南大学学报(自然科学版),2010,37(8):45—48.

YANG H,HE Y G,HUANG J Y.A 10-b 150MHz pipeline ADC in 0.25μm CMOS[J]. Journal of Hunan University(Natural Sciences),2010,37(8):45—48.(In Chinese)

[8] WU H J,CHEN Z H,YU Z G,et al. A 12-bit 250MSPS pipeline ADC with 4Gbps serial output interface[C]//2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology. Piscataway:IEEE,2016:1464—1466.

[9] OKUNO K,OBATA K,KATO T,et al. An 800-MHz 8-bit high speed SAR ADC in 16nm FinFET process[C]//2017 IEEE International Meeting for Future of Electron Devices,Kansai. Piscataway:IEEE,2017:24—25.

[10] LIU H Z,LIU M L,ZHU Z M. A 12-bit 200MS/s pipelined-SAR ADC in 65-nm CMOS with 61.9 dB SNDR[C]//2019 IEEE International Conference on Electron Devices and Solid-State Circuits. Piscataway:IEEE,2019:1—2.

[11] 于健海,尹亮. 用于微機械加速度计的亚微米工艺ADC设计[J]. 西安电子科技大学学报,2019,46(3):140—147.

YU J H,YIN L. Design of an ADC with the submicron process for micromechanical accelerometers[J]. Journal of Xidian University,2019,46(3):140—147. (In Chinese)

[12] CHO J K. A 2.24-mW,61.8-dB SNDR,20-MS/s pipelined ADC with charge-pump-based dynamic biasing for power reduction in Op AMP sharing[J]. IEEE Transactions on Circuits and Systems I:Regular Papers,2017,64(6):1368—1379.

[13] XU W G,GAO Y F,LIU X D,et al. A 18 mW 12 bit 50MS/s SHA-less pipelined ADC[C]//2017 IEEE 12th International Conference on ASIC. Piscataway:IEEE,2017:776—779.

[14] WANG C W,WANG X,DING Y,et al. A 14-bit 250MS/s low-power pipelined ADC with aperture error eliminating technique[C]//2018 IEEE International Symposium on Circuits and Systems. Piscataway:IEEE,2018:1—5.

[15] 张凌东,魏敬和,陈珍海,等. 用于16位125MS_s ADC的无采样保持运放前端电路[J]. 中国电子科学研究院学报,2018,13(3):331—334.

ZHANG L D,WEI J H,CHEN Z H,et al. Front-end circuit without sample-and-hold amplifier for 16bit 125MS/s ADC[J]. Journal of CAEIT,2018,13(3):331—334. (In Chinese)