超声相控阵系统提高延时分辨率的研究进展

徐皓胜,曾 伟,杨绍辉,曾德平,2

(1. 超声医学工程国家重点实验室,重庆医科大学 生物医学工程学院,重庆市生物医学工程学重点实验室,重庆 400016;2. 超声医疗国家工程研究中心,重庆 401121)

0 引言

超声相控阵技术基于可编程逻辑设备和多阵元阵列换能器,控制每个阵列元件发射超声波的延迟时间实现在声场中聚焦、偏转或对接收到的回波信号进行延迟补偿,加权叠加求和来超声成像,是超声技术发展的热点之一[1]。相控阵技术最初是在相控阵雷达领域中应用,近年来已应用于工业无损检测领域。它比传统无损检测更具优势,通过改变到达物体的超声波相位关系,使声束聚焦和偏转,从而实现对工件的波束扫描并获得内部成像。与传统的超声检测相比,超声相控阵技术可提高覆盖范围、检测灵敏度和准确性,且可获得高分辨率的裂纹、焊缝等缺陷图像。因此,它已成为超声无损检测领域发展最快的技术,并广泛应用于航空、铁路、建筑和石油管道等工业领域[2-3]。此外,超声相控阵还具有低功率、瞬时、动态聚焦和无创等特点,除在工业领域中的应用外,它在医学治疗和成像的研究和应用也越来越多,尤其是在脑部多种疾病的治疗取得积极的进展[4]。尽管超声相控阵技术的应用领域不同,但基本原理一致。超声相控阵仪器开发的核心与难点是精确延时发射技术,国内外学者在超声相控阵发射精确延时聚焦方面开展很多有益研究。

1 超声相控阵发射和接收基本原理

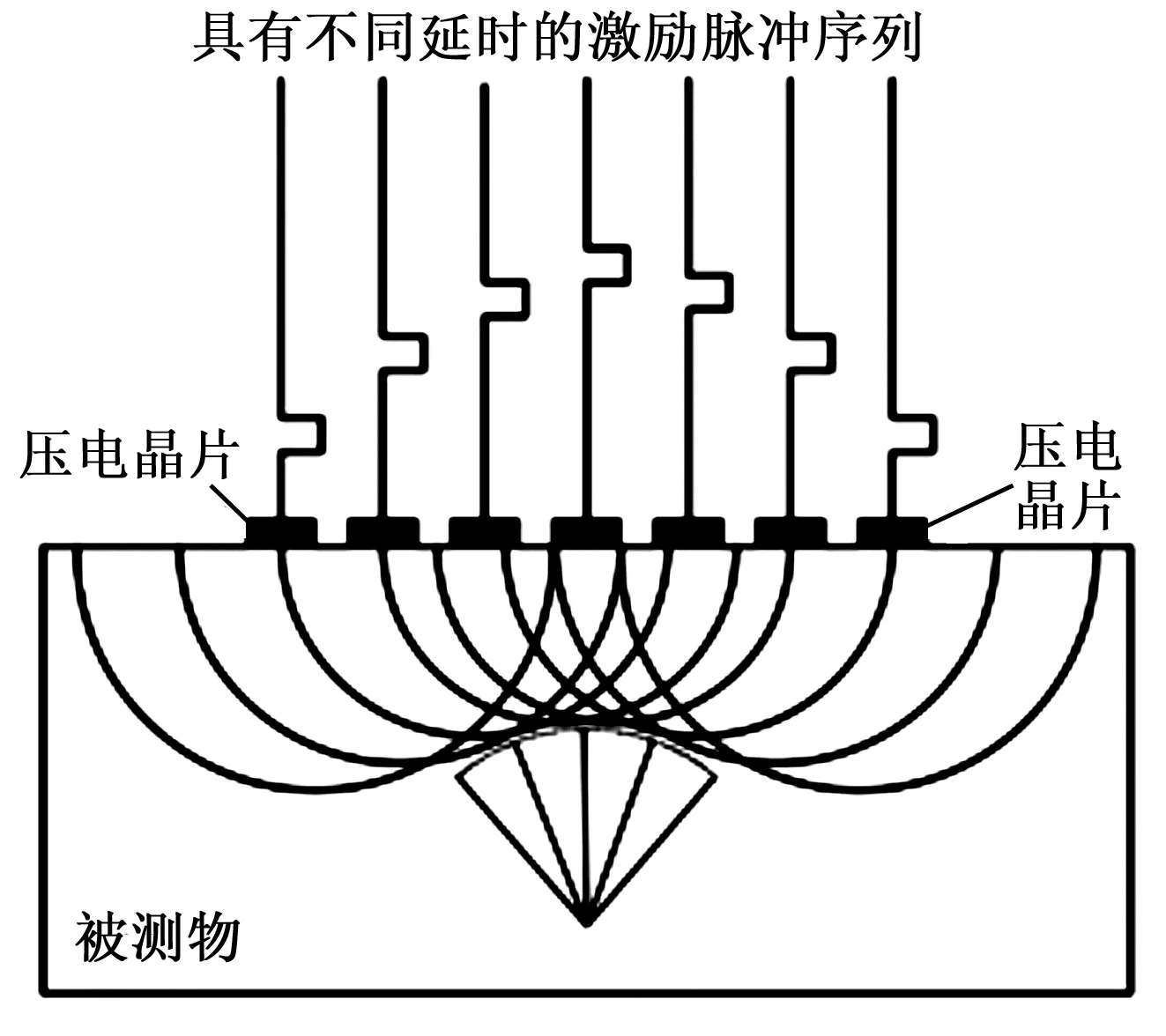

阵列换能器的每个阵元激励由软件控制,通过改变各个阵元的发射延时时间,形成相位不同的超声相干波束,在声场中叠加干涉,使声束发生聚焦和偏转。超声相控阵发射原理如图1所示。

图1 超声相控阵发射聚焦原理图

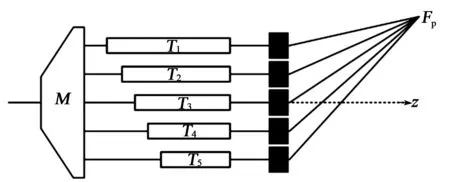

接收回波过程相当于发射的逆过程。聚焦点相对各个阵元的距离不同,每个阵元接收到目标点反射的回波时间也不同,且存在相位偏移,所以在接收时要对回波信号进行延时补偿处理和加权求和。在延时叠加过程中,可控制合成方式(如阵列元素的相位和幅度)来实现普通聚焦、动态聚焦、合成孔径、多声束形成等控制效果。相控阵接收回波原理如图2所示,T1~T5为延时补偿时间,M为加权求和,Fp为焦点位置,z为中轴线。

图2 超声相控阵接收回波原理图

2 延时分辨率对相控阵系统的影响

延时分辨率是相控阵技术最重要的参数,它决定了系统的成像分辨率和误差旁瓣[5],而误差旁瓣是衡量超声相控阵系统的最主要指标。高分辨率延时可减小到达焦点的每个阵列信号的相位误差,从而减少误差旁瓣。在实际使用中,延时分辨率不可能无限小,且过高的延时分辨率会增加系统复杂度,对硬件系统有较高要求。所以要根据需求选择合适的延时分辨率[6]。

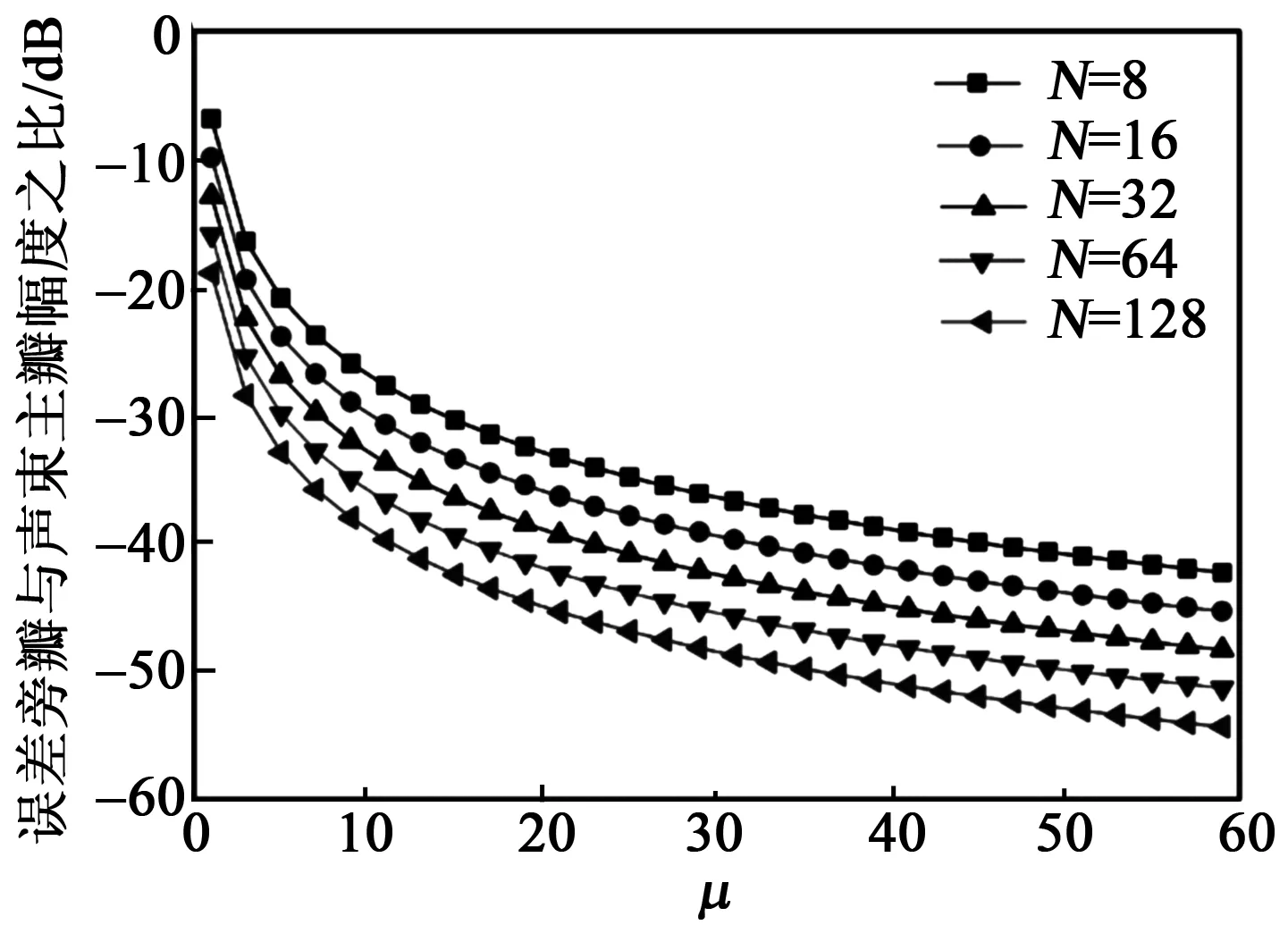

相控延时误差旁瓣与声束主瓣幅度比为

(1)

图3为延时分辨率与误差旁瓣的关系。由式(1)和图3可知,在延时分辨率不变的情况下,N越多,误差旁瓣越小;在换能器阵列元件数相同的情况下,延迟分辨率越高,误差旁瓣越小。延时分辨率高可增大主瓣抑制旁瓣,有效提高成像分辨率。此外,延时分辨率对空间分辨率和波束偏转[7]也有一定影响。由此可见,延时分辨率对相控阵系统有重要影响,是相控阵系统的核心。

图3 延时分辨率与误差旁瓣的关系

3 硬件延时技术

硬件延时技术是早期使用的延时方法,主要采用模拟延迟线(如LC网络)来实现相位延时,使用电子开关来分段切换以获得不同的延时量,延时分辨率一般在几十纳秒。最早的相控阵波束形成器在20世纪60年代末开发用于大脑成像[8]中。这些早期的系统涉及波束形成器功能实现相对简单[9]。聚焦时采用集总的L-C延迟线作为延迟元件。实时扇区扫描(在特定方向上控制波束)要求在大量延迟配置间进行快速切换,这需复杂的控制系统,并在模拟延迟线上产生不良的切换噪声。对于动态聚焦和转向,作为延迟元件的L-C延迟线很庞大,因为对于每个元件和每个转向而言,沿径向深度的焦点的延迟模式都不同,因此需复杂的开关电路。之后出现了专用的延时芯片(数字可编程延时器)替代了模拟延迟线,提高了延时精确度和稳定性,延时分辨率甚至低于1 ns[10]。

4 数字延时技术

一般数字延时可分为专用和通用延时单元两大类。如AD9501等专用延时单元基于模拟器件,最大延时范围为2.5 ns~10 ms,最小延时时间为10 ps,但动态范围较小。通用的延迟单元一般由可编程逻辑器件(如现场可编程门阵列(FPGA),复杂可编程逻辑器件(CPLD)等)来实现,具有设计简单可靠、动态范围大等优点。但其延迟分辨率受器件最大系统时钟频率的限制,延时分辨率一般在纳米级。与硬件线路延时相比,数字延时技术具有分辨率高,稳定性好,调控方便等特点,可提高超声相控阵系统的性能。所以,现在数字延时技术逐渐代替了硬件线路延时技术。

4.1 专用芯片延时

专用的延时芯片也叫数字可编程延时器,是一种时间延时器,且输入、输出信号具有可编程功能。Dusa C等[11]采用专用集成芯片在40 MHz采样频率下实现3.125 ns接收延时分辨率,同时提出了完整波束形成过程的模块化架构,可使每个通道的最小延时分辨率达1.25 ns。Chang-Hong Hu等[12]用可编程延迟芯片(PDU13F-2)进行发射聚焦延时,通过软件来实现10 ns的整数倍粗延时,控制PDU13F-2来实现小于10 ns的细延时。杨斌等[13]基于CPLD及时钟主频率的粗延时基础上采用AD9501实现相控发射细延时, 延时分辨率可达1 ns。专用延时芯片大多应用场合都会结合逻辑器件来提高系统的动态延时范围。虽然专用的延时芯片稳定好,但其缺陷也很明显,如果相控阵系统的通道数量过多,则成本较高,同时系统的集成度较低,无法与其他功能集成,通用性差,修改控制难。

4.2 采样时间延时

基于FPGA芯片的系统时钟频率延时法结构简单,易实现。祁小凤等[14]提出了一种基于CPLD和高压数字脉冲发射器的128通道超声相控阵发射电路系统,具有5 ns的脉冲延时分辨率。此外,还可采用系统时钟频率高的高端FPGA设计高速计数器来提高延时分辨率。孔超等[15]用最高工作频率(达550 MHz)的高端FPGA芯片来设计高速计数器,延时分辨率可达2 ns。但仅基于逻辑器件的系统时钟频率来控制延时会受器件工作频率上限的限制。所以在此基础上会采用其他精细的延时法与此相结合来提高整体的延时分辨率。邓鹰飞等[16]设计了一种高压发射电路的精确延时电路,在200 MHz时钟频率基础上,通过双数据速率输入输出DDRIO作为时钟倍增器实现了波束2.5 ns延时。同时脉冲发射电压强度是需考虑的一个重要因素,它将直接影响回波信号的强弱和检测深度,而回波信号和检测深度也直接影响超声相控阵系统的性能。

4.3 软件延时

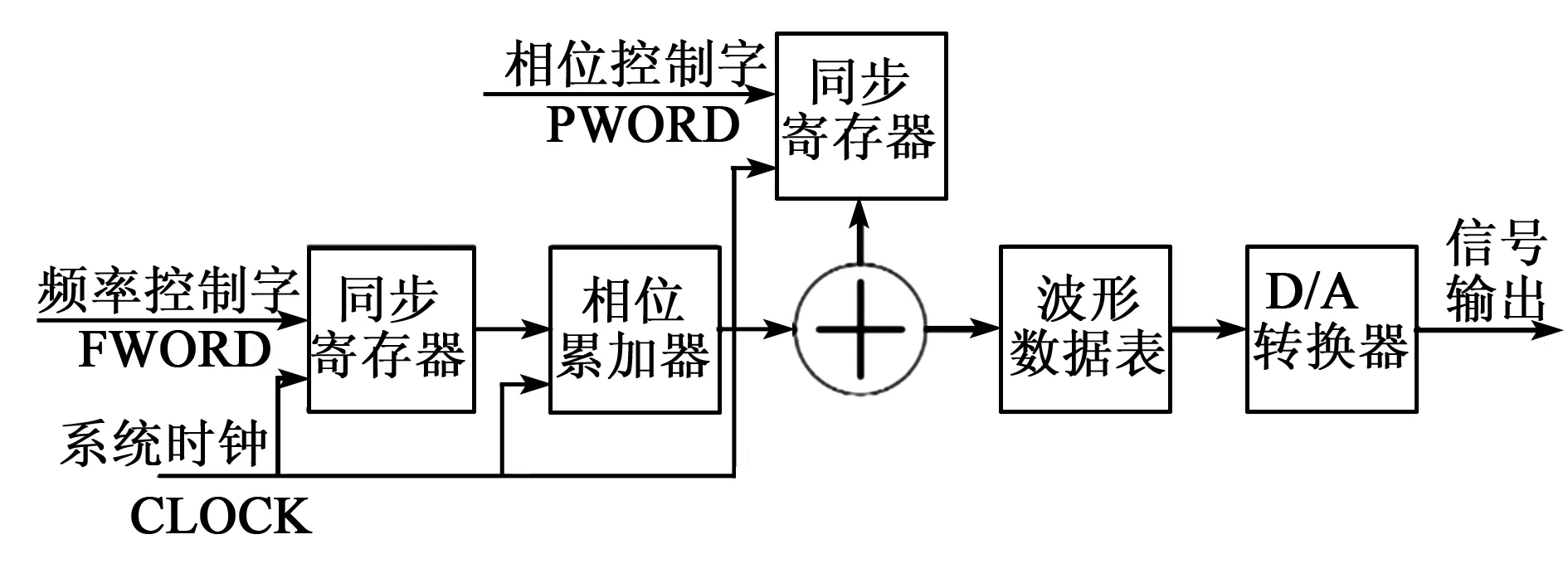

4.3.1 基于直接数字频率合成器(DDS)的延时法

DDS技术是近年来广泛应用的一种数字技术, 可从相位角度合成信号,并具有高的频率和相位分辨率、低相位噪声和快速的频率转换等优点,一般DDS结构如图4所示。鲍晓宇等[17]提出了采用D/A输出时钟和DDS技术相结合的方法实现了1 ns的发射相控延时分辨率。骆英等[18]将计算出的激励波形量化数据导入片上ROM,并在FPGA片内部构建了地址发生器依次读出ROM中的数据,实现了4.78 ns的延时分辨率。波形的相位分辨率只与周期波形数据存储表的长度有关,如果FPGA片上存储空间允许,延时分辨率还可进一步提高。理论上波形相位分辨率在可无限细分,但FPGA片上存储数据的能力有限,所以,J. M. Huang等[19]使用坐标旋转数字计算(CORDIC)算法模块代替ROM查找表模块的新型DDS,应用CORDIC算法模块可减少存储量,提高数据精度。

图4 DDS结构框图

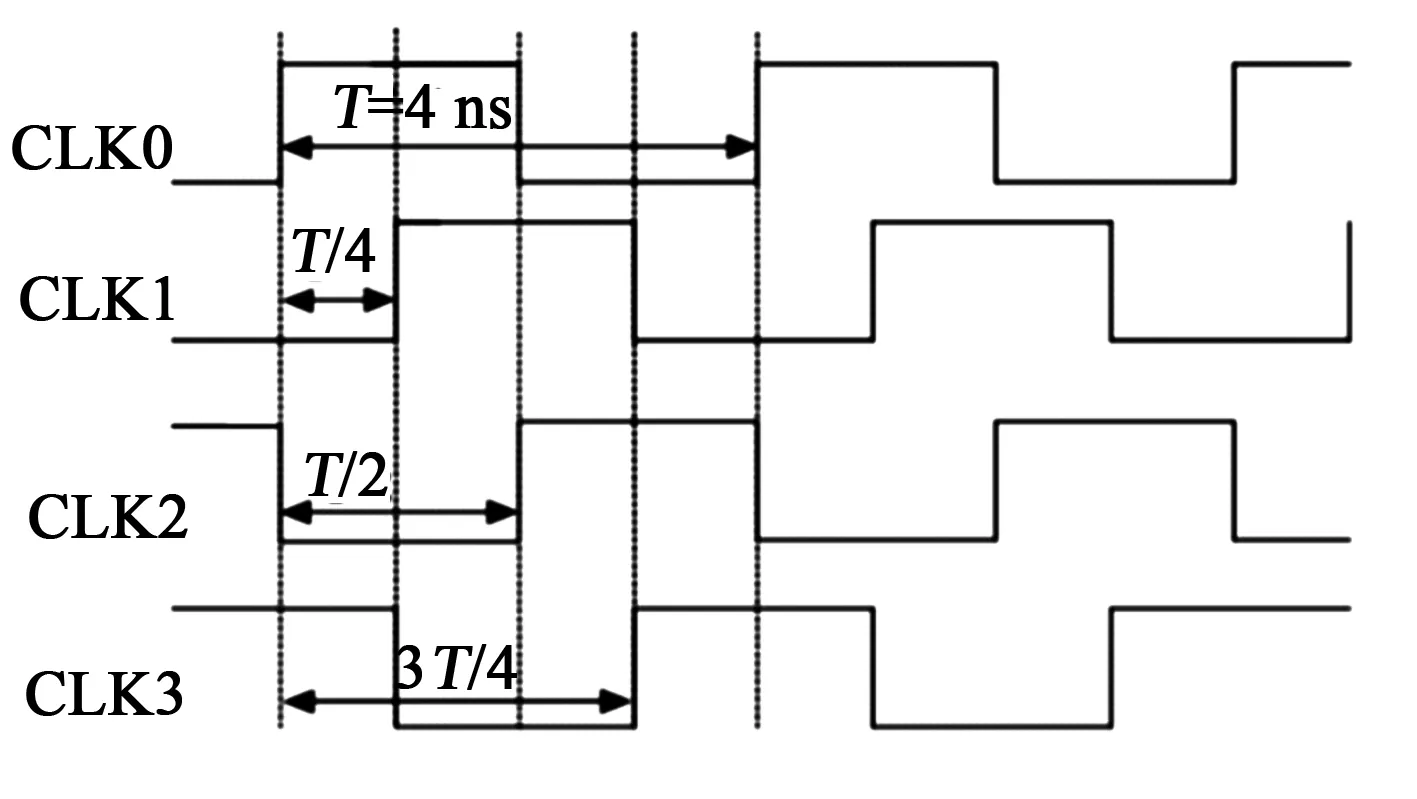

4.3.2 基于锁相环(PLL)的延时法

最常用方法是基于锁相环延时法,一般FPGA芯片内部都会集成锁相环模块,可在工程中直接调用,通过倍频移相获得高频率、稳定可靠、相位可调的系统时钟,如图5所示。系统时钟控制整个系统,在实际应用过程中起决定性作用,延时分辨率再高,系统时钟不可靠稳定,也会造成误差旁瓣的激增。G. D’Amato等[20]设计与实现了基于FPGA合成延迟线和锁相环的高性能、可重构的有源相控阵天线四通道波束控制单元。该单元允许每个通道可编程的时间延迟相当于约1.4°的相移调谐步骤。杨先明等[21]基于FPGA芯片利用锁相环的倍频和移相技术,采用同步和等延时设计,实现了1 ns的阵元发射延时分辨率。如果想获得更高的延时分辨率,可用多个锁相环级联产生多个存在一定相位差的时钟信号。Fan Yuhang等[22]用FPGA的2个PLL资源。将50 MHz的时钟信号加倍并移位生成8个相位差为45°的250 MHz方波信号通道,延时分辨率达0.5 ns。过高的延时分辨率会对硬件电路造成很大的压力。Peter R. Smith等[23]用时钟周期的整数倍和周期相位差引入粗略和精细的延迟,这些粗略和细微的延迟用于生成激励波形,其延迟轮廓接近理想值,减少了相位量化误差和误差旁瓣。於炜力等[24]提出了一种多通道超声相控阵发射系统,通过FPGA主控模块、千兆以太网通信模块和高压脉冲发射电路的设计,实现了高速实时的数据传输和超声波信号的高频高压的相控阵聚焦发射,相控延时分辨率达到1.25 ns。PLL能产生相位可调的稳定高频时钟信号,并且能在FPGA等逻辑器件中直接调用,节约了开发时间,成为了现在主流的延时方法之一。

图5 锁相环移相示意图

4.3.3 基于滤波器的延时法

基于滤波器的延时法适用于实时性强、精度高的聚焦延时算法的实现。同时在计算速度、性价比和分辨率方面具有较大优势。Volder J.E首次提出坐标旋转数字计算方法(CORDIC)算法,通过相位旋转来实现采样序列延时。MA Jieming等[25]采用多核数字信号处理器(DSP)芯片完成聚焦算法,用 40 MHz采样时钟,使用4个核对2亿个采样点相位旋转查表,减小了相位误差影响。由于相位旋转算法复杂,需要高性能的硬件支持,很多学者转向数字重采样实现高精度延时研究,获得高倍密集输出序列来减小量化延时误差,从而基于多速率数字信号处理技术的多相滤波法开始应用到超声延时聚焦,如典型普通非递归型(FIR)滤波器多相内插滤波法[26],延时分辨率可达几纳秒。刘桂雄等[27]采用内插滤波法,设计了半带滤波器作为内插滤波器,通过对超声回波信号进行8倍内插滤波与多相分解,实现了1.25 ns的信号延时,与等效的普通非递归型(FIR)滤波器相比,减少了运算量,提高了延时精度。焦志海等[28]通过高速模数转换器(ADC)采样,再结合抽取、内插滤波法实现超声信号延时,精度可达1.4 ns。但因受资源、速度和系统时钟频率等限制,精度小于1.25 ns 较难。提高系统的时钟频率及采用高端的FPGA芯片是提高延时分辨率的一个主要途径。所以Peilu Liu等[29]在系统时钟为125 MHz时,用插值级联积分梳状(CIC)滤波器经过8倍插值滤波和分解后,实现了1 ns的延时分辨率。Wenming Tang等[30]提出了一种新型的多相CIC内插滤波器设计,用改进的10倍多相内插CIC滤波器在100 MHz采样频率下实现了1 ns的延时分辨率。

研究基于 FPGA 的多相内插滤波法来实现高精度延时已受广泛关注,普通 FIR 滤波内插技术方法在算法、资源复杂度与精度均有局限性,故研究内插滤波器与内插方案具有现实意义。

4.4 数字延时技术小结

经过多年的发展,数字延时技术越来越来成熟,逐渐成为相控阵系统延时的主流方法。数字延时法特性如表1所示。

表1 数字延时法特性比较

采样延时和延时芯片可以实现较高的延时分辨率,但是成本高,可移植性差,灵活性低。另外,使用FPGA的锁相环乘法和相移,也可以实现很高的时延精度,但对系统时钟的频率要求较高。理论上,延时分辨率越高越好,但是硬件电路造成的误差延时与延时分辨率的比值也会越来越大,使得实际输出的激励延时产生不确定性,影响聚焦效果。

基于普通滤波器(如多级半带滤波器、FIR滤波器等)可实现较高的时延分辨率,但在硬件实现中算法复杂。与普通滤波器相比,CIC滤波器无乘法器,结构简单,运行速度快,占用资源少、易于在FPGA等逻辑器件上实现等优点,但内插倍数越大,最大相对时间误差越大。同时脉冲发射,电压强度将直接影响回波信号的强弱和检测深度,进而影响成像质量,还有系统同步设计也是需考虑的一个重要因素。

5 发展趋势

超声相控阵已广泛应用在工业无损检测、医疗诊断设备、水下探测和疾病治疗等领域。随着应用范围越来越广,尤其在疾病治疗领域,对相控阵系统的延时分辨率提出了更高要求。同时也催生了多种延时技术。而现有的硬件线路延迟、采样延迟和专用芯片延时具有通用性差、成本高及难以修改等缺陷。软件延时具有易实现、可修改、稳定性和重复性好等优势,在实现准确的时间延迟上具有很大的潜力。然而,软件延时在很大程度上取决于算法的质量,因此,研究人员进行了许多尝试来改善软件延时法的性能。

在理论仿真方面,利用多种算法相结合来提高延时分辨率,如将DDS技术与CORDIC算法结合减少存储量,提高延时分辨率;将DDS技术与锁相环技术结合产生相移精度高且稳定的移相信号; 将内插滤波器与多相分解法结合来减轻硬件实现负荷。对于软件延时,很多方法已较成熟,随着能达到的延时分辨率越来越高。然而,在工程应用方面,除考虑延时分辨率外,还需考虑硬件处理能力和实时计算能力。如采用CIC滤波器替代普通的FIR滤波器来减少硬件电路负担,提高运行速度;采用千兆以太网传输技术来提高实时的数据传输能力;利用二极管高压钳位来提高发射电压,进一步改善发射信号的准确性、准确度。

目前各种延时法的延时分辨率基本都做到10 ns内。在实际应用过程中,算法优化和硬件电路误差都要考虑,所以,现在研究人员都在改善硬件电路延时误差和处理能力的基础上来探究提高延时分辨率的方案。

6 结束语

高分辨率聚焦延时是超声相控阵系统的核心,出现了一系列精准延时法,总体上可分为硬件延时和数字延时两类。硬件延时作为早期的一种延时法已被数字延时取代,而数字延时技术中的采样延时和专用芯片延时等方法存在成本高、修改控制难、不易于集成等缺点;软件延时凭借灵活的数字信号处理算法来实现聚焦延时,具有通用性强、移植性好等优点,所以软件延时逐渐成为延时控制的主要方法。超声相控阵系统的性能是随着延时分辨率的提高而提高,但是,超声相控阵系统不仅要考虑延时分辨率还需要考虑延时方法实现的难易、硬件的复杂程度和整体成本等多种因素,因此,应该根据系统性能指标要求选择合适的延时方法。