基于40nm CMOS工艺的25Gb/s光接收机模拟前端电路设计

谢 生,闵 闯,魏 恒,毛陆虹,杜永超

基于40nm CMOS工艺的25Gb/s光接收机模拟前端电路设计

谢 生1,闵 闯1,魏 恒2,毛陆虹3,杜永超1

(1. 天津大学微电子学院,天津 300072;2. 中国电子科技集团第五十四研究所,石家庄 050000;3.天津大学电气自动化与信息工程学院,天津 300072)

为更好地屏蔽探测器结电容、适配先进工艺节点的低电源电压,对共栅级放大器进行改进,提出一种带有源反馈结构的共栅级跨阻放大器,降低了电压余度消耗并有效提升带宽.在此基础上,采用TSMC 40nm CMOS工艺,设计一款速率为25Gb/s的伪差分光接收机模拟前端电路.该电路包括跨阻放大器、限幅放大器、直流偏移消除电路和输出缓冲级.其中,跨阻放大器采用带有源反馈结构的共栅级放大器,限幅放大器利用交错式有源反馈结构来提高电路带宽内的幅频响应平坦度,T倍频器作为阻抗匹配的输出缓冲级.仿真结果表明,在电源电压0.9V,探测器结电容等效值为150fF的情况下,光接收机模拟前端电路的跨阻增益为59.6dBΩ,-3dB带宽为20.8GHz,功耗为46.6mW,芯片核心面积为600µm×440µm.

跨阻放大器;共栅级跨阻放大器;光接收机;CMOS工艺

光互连相对于电互连具有高速率、高带宽、低损耗、抗干扰等优势,在短距离通信领域受到越来越多的关注,并逐渐取代电互连成为通信系统的主要传输方式.光接收机作为光互连系统中的核心模块,其主要功能是将线路传输的光信号转换成电信号,经放大、判决等处理后,提取原始信号[1-3].

光接收机模拟前端电路作为接收电路的重要组成部分,其参数指标通常是提高光互连系统整体性能的瓶颈[4].较低的制造成本以及在同一芯片上实现模拟和数字电路集成使得CMOS技术更具有吸引力[5].因此,许多研究机构针对基于标准CMOS工艺的光接收机设计进行了深入的研究并取得了一定成果.其中一些还实现了光探测器和光接收机电路的单片集成[6-9].上述研究成果普遍基于电感峰化技术来实现数据的高速传输,然而大量使用电感会使芯片抗电磁干扰能力减弱,并占用较多的版图面积,降低芯片集成度.此后,为削弱电感对接收机电路稳定性的消极影响,一些研究机构基于BiCMOS工艺设计出能够实现数据高速传输、无电感结构的光接收机以及光电混合集成接收机[10-11].最近,武汉大学也基于BiCMOS工艺研制出带有自动增益控制、无电感结构的光接收机模拟前端电路[12].虽然BiCMOS工艺中晶体管较高的截止频率能够进一步提高接收机的传输速率,但其相较于CMOS工艺仍存在着造价高、集成度低、功耗高等缺点,短时间内还无法取代后者成为集成电路设计与制备的主流工艺手段.

针对上述问题,本文对共栅级放大器进行改进,提出一种带有源反馈结构的共栅级跨阻放大器,在此基础上结合TSMC 40nm CMOS标准工艺,设计出一款光接收机模拟前端电路.该电路采用有源反馈结构共栅级放大器作为跨阻放大器,采用交错反馈结构差分放大器作为限幅放大器,采用T倍频器作为输出缓冲级,从而在保证带宽的同时尽可能地优化增益.另外,增加直流偏移消除电路也能在一定程度上提高电路性能.

1 带有源反馈结构共栅级放大器设计

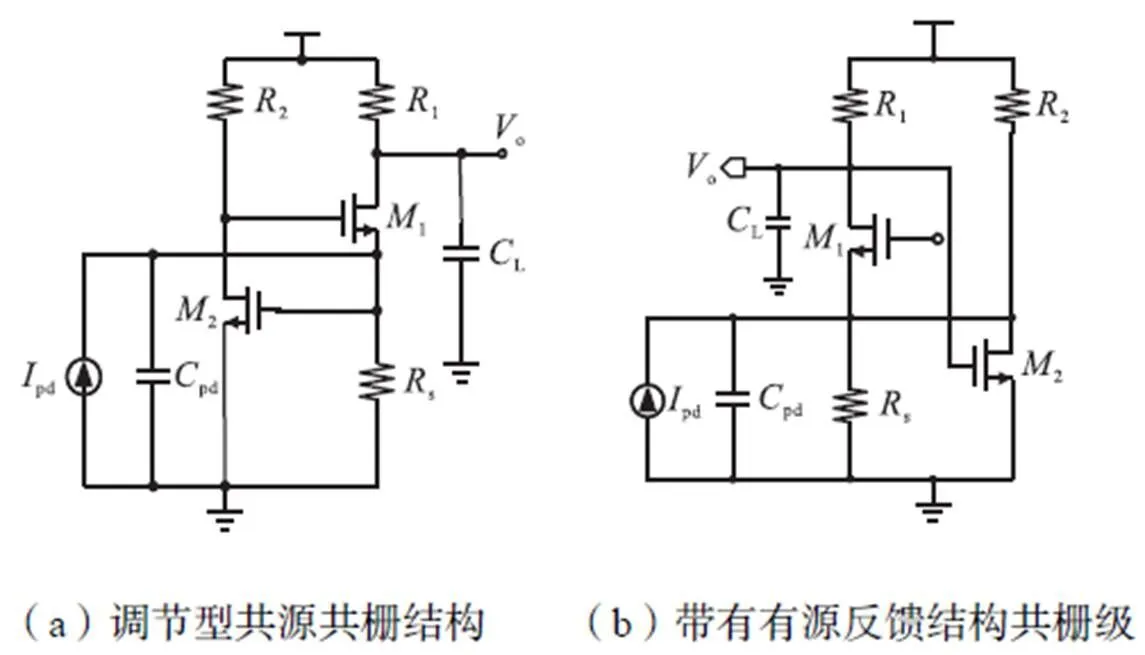

由于探测器较大的结电容会使跨阻放大器(transimpedance amplifier,TIA)的极点前移,从而减小带宽,故能否有效地隔离探测器结电容的影响成为了跨阻放大器设计过程中的重点之一.调节型共源共栅结构(regulated cascode,RGC)跨阻放大器因具有较低的输入阻抗,可以有效减弱探测器结电容对接收机带宽的恶化而被广泛应用[13],其结构如图1(a)所示.1和1组成共栅级放大器,2和2组成共源级放大器提供局部反馈,由于局部反馈的作用使RGC相比于共栅级放大器具有更小的输入阻抗.

图1 跨阻放大器

RGC结构跨阻放大器的低频输入阻抗为

低频跨阻增益

其传输函数为

式中:pd为探测器结电容;L为负载电容;i≈sb1+gs2;o≈gd1+db1.由式(3)可见,i,RGC=m1(1+m22)/(pd+i)和o,RGC=1/1(L+o)分别为RGC跨阻放大器的两个极点.由于RGC输入阻抗较小,故o,RGC<i,RGC,o,RGC为主极点,决定跨阻放大器的带宽,其-3dB带宽

由RGC原理图可知,共源级局部反馈放大器输出端对地要消耗两个MOS管阈值电压,在低电源电压的先进工艺中可能会出现电压不足的情况,从而影响电路稳定性.因此,本文提出一种带有有源反馈结构的共栅级放大器,电路结构如图1(b)所示,其与RGC相比同样具有很低的输入阻抗.1和1组成基础共栅级放大器,2和2组成共源级放大器提供有源反馈.其小信号模型如图2所示.其中,1≈gs1+sb1+db2,2≈gd1+db1+gs2.由电路结构可见,在输出结点和地之间只消耗一个阈值电压,因此相较于RGC结构电压余度降低约110mV.通过小信号模型分析,可推导出其低频输入阻抗

低频跨阻增益

其传输函数为

对比式(1)和式(5)可见,带有有源反馈结构共栅级跨阻放大器与RGC跨阻放大器具有相近的输入阻抗,都能很好地屏蔽探测器结电容.同时,为实现带有有源反馈结构共栅级跨阻放大器输入阻抗减小,并保证一定的转化增益,需调整电路参数来达到一个较大的1和较小的m2,这样就需要严格控制2的 尺寸.

考虑到s和2较大,可以将式(7)简化成式(8).由式(8)可知,带有有源反馈结构共栅级跨阻放大器的固有频率

且

故带宽扩展比为

如果调整电路设计使得并且gm2R1=1,就能得到最佳平坦度,且相较于RGC跨阻放大器得到约41%的带宽扩展.上述设计电路幅频特性曲线的MATLAB计算结果如图3所示.由图3可见,本文所提出的跨阻放大器结构带宽扩展倍数符合理论推导结果.

2 光接收机模拟前端电路分析

为验证带有源反馈结构共栅级跨阻放大器的合理性,基于此结构设计了一种伪差分光接收机模拟前端电路,其电路结构如图4所示,包括跨阻放大器、限幅放大器(limiting amplifier,LA)、直流偏移消除(DC offset cancellation,DCOC)电路和输出缓冲级(output buffer,OB).其中,光电二极管通过光电转化将来自光纤线路的微弱光信号转化成光电流并传输至跨阻放大器[15].光电流经过跨阻放大器转化为电压信号,并放大使之具有一定的输出摆幅.限幅放大器继续放大电压信号,同时进行整形,直至可用于数据恢复电路.输出缓冲级是为了实现接收机系统中各部分电路间的阻抗匹配,同时保证电路输出摆幅满足设计要求.直流偏移消除电路由低通滤波器和共源级放大器组成,其主要作用是削弱信号变化引起的电路直流工作点偏移.在限幅放大器和输出缓冲级之间增加电感以形成P型网络,进一步提高电路 带宽.

图4 模拟前端电路结构

因跨阻放大器已在前文分析,故下面分析限幅放大器、直流偏移消除电路、输出缓冲级.

2.1 限幅放大器及直流偏移消除电路

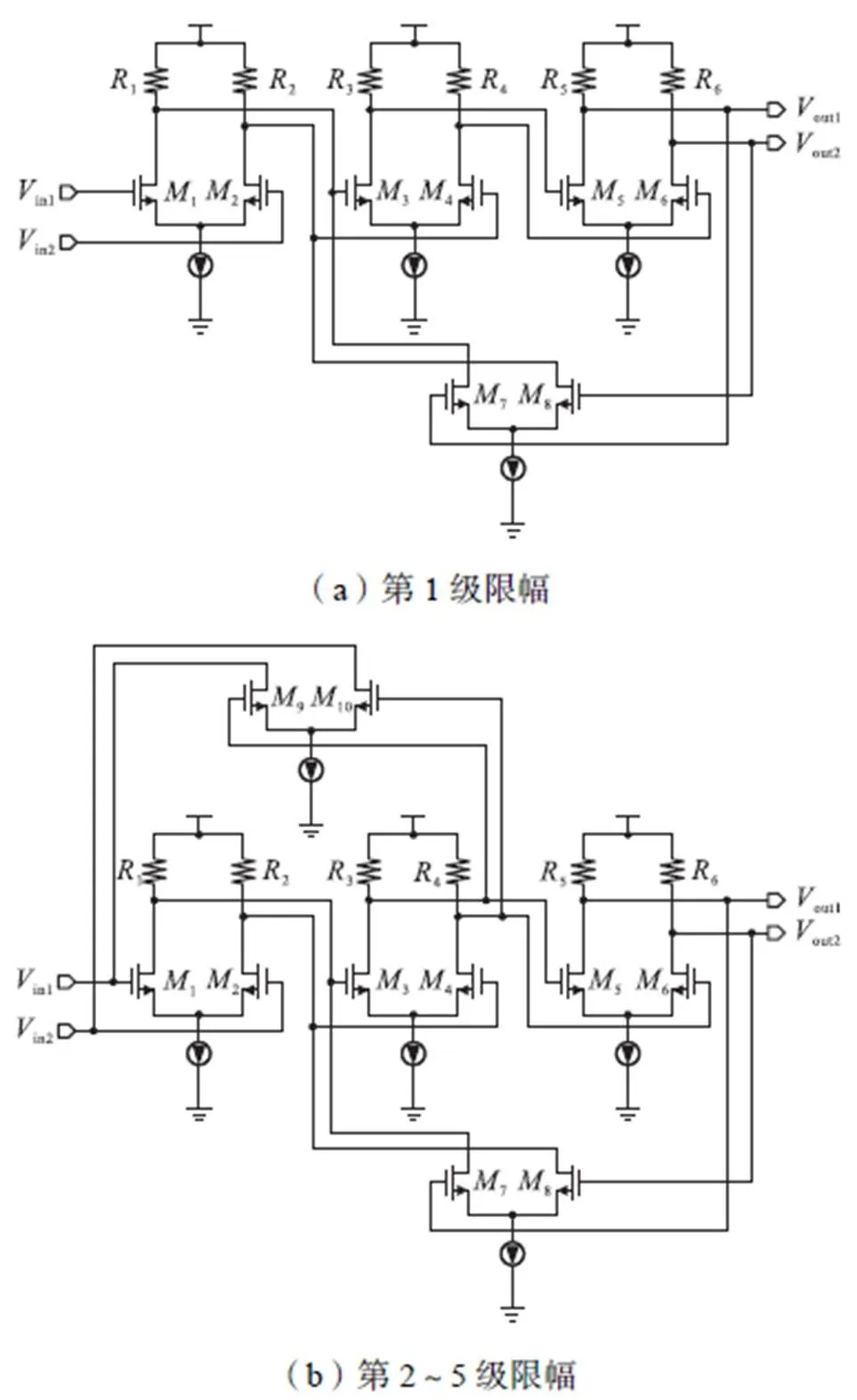

传统三阶有源反馈限幅放大器在级联时会产生峰化增益,从而恶化频率响应曲线的平坦度,并且随着级联个数的增加,这种峰化增益会越来越大,最终使其性能不能满足实际需求.为了克服这种三阶增益级严重的峰化现象,本文采用交错式有源反馈结构限幅放大器,共5级,具体结构如图5所示.

图5 限幅放大器结构

2个级联的三阶共源反馈放大器传输函数为

交错反馈式有源反馈放大器传输函数为

其中

由式(16)~(18)可见,交错式有源反馈放大器的传输函数可拆解为2个三阶有源反馈放大器传输函数的乘积.此时,这两个三阶放大器的3个极点不再重合,限幅放大器整体频率响应的峰化增益变小,有效提高了带宽范围内幅频响应的平坦度.

DCOC电路如图6所示.可以看出,电路输入端由1、1和2、2组成低频截止低通滤波器,将LA输出交流部分过滤,为1、2栅极提供直流偏置.当LA两个输出端直流工作点出现不同时,1、2漏极电流产生差异,反馈至TIA输出端进而调整其输出结点直流电平,弱化差分电路共模信号失配带来的影响,使光接收机整体电路重新恢复稳态.

图6 直流偏移消除电路

2.2 输出缓冲级

在高频信号的传输过程中,为避免信号反射造成的传输功率损耗,需要所设计电路的输入和输出端必须满足阻抗匹配,且特征阻抗为50Ω[16].由于光接收机电路传输信号通常为高频信号,故要求接收机系统各模块在带宽内必须实现阻抗匹配.

图7 fT倍频器电路原理

3 仿真结果

为了实现上述模块的单片集成,本文基于TSMC 40nm CMOS工艺对整体电路进行了优化,并完成版图绘制.

图8给出了接收机模拟前端电路的幅频特性曲线.由图8可知,模拟前端电路的跨阻增益为59.6dBΩ,-3dB带宽为20.8GHz.

图8 模拟前端电路跨阻增益曲线

图9给出了电路版图后仿的参数结果.由图9可见,参数21在-3dB带宽内极为平坦,其值约为5.3dB;参数22在10GHz带宽范围内小于-10dB,在20GHz带宽范围内小于-7dB.

图9 模拟前端电路S参数曲线

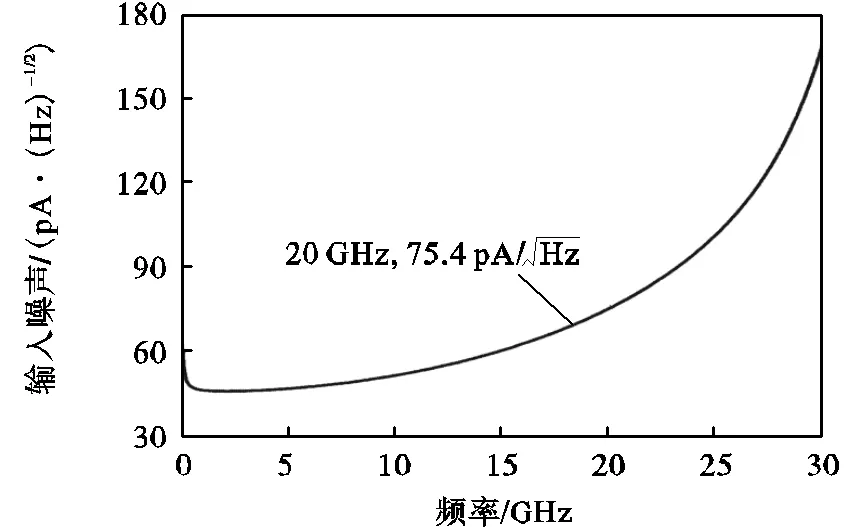

图10 模拟前端等效输入噪声曲线

图11和图12分别给出了传输速率为10Gb/s和25Gb/s时的眼图,以表征本文所设计光接收机模拟前端电路对信号的传输效果.

由图11和图12可见,眼图抖动极小,增益尖峰存在但影响有限,对称完整,垂直张开程度明显,能够满足高质量、高速率的信号传输要求.

表1总结了本文所设计模拟前端电路的性能参数,并与其他文献报道做了对比.由于低电源电压以及仅使用一次电感峰化技术,本文所设计的模拟前端电路在功耗和集成度方面更具优势.

图11 10Gb/s眼图

图12 25Gb/s眼图

表1 性能对比

Tab.1 Performance comparison

4 结 语

[1] Fang Q,Liow T Y,Song J F,et al. WDM multi-channel silicon photonic receiver with 320Gbps data transmission capability[J]. Optics Express,2010,18(5):5106-5113.

[2] Alduino A. Demonstration of a high speed 4-channel integrated silicon photonics WDM link with hybrid silicon lasers[C]// Hot Chips Symposium(HCS). Califor-nia,USA,2010:1-29.

[3] Oh W S,Park K. A 12-Channel 60-Gb/s transimpedance amplifier and limiting amplifier array for OPCB applications[C]// International Conference on Electronics Circuits and Systems. Marrakech,Morocco,2008:22-25.

[4] 谢 生,谷由之,毛陆虹,等. 基于SiGe BiCMOS工艺的高速光接收机模拟前端电路[J]. 天津大学学报:自然科学与工程技术版,2018,50(1):57-63.

Xie Sheng,Gu Youzhi,Mao Luhong,et al. Analog front-end circuit for high-speed optical receiver based on SiGe BiCMOS technology[J]. Journal of Tianjin University:Science and Technology,2018,50(1):57-63(in Chinese).

[5] Razavi B. Design of Analog CMOS Integrated Circuits[M]. New York:McGraw Hill Education,2000.

[6] Assefa S,Green W,Rylyakov A,et al. CMOS integrated nanophotonics-enabling technology for exascale computing systems[C]//Optical Fiber Communication Conference and Exposition. California,USA,2011:1-3.

[7] Chou S T,Huang S H,Hong Z H,et al. A 40Gbps optical receiver analog front-end in 65nm CMOS[C]//

International Symposium on Circuits & Systems. Seoul,South Korea,2012:1736-1739.

[8] Takemoto T,Yamashita H,Yazaki T,et al. A 25-to-28Gb/s high-sensitivity(-9.7dBm)65nm CMOS optical receiver for board-to-board interconnects[J]. Journal of Solid-State Circuits,2014,49(10):2259-2276.

[9] Chiang P C,Jiang J Y,Hung H W,et al. 4×25Gb/s transceiver with optical front-end for 100GbE system in 65nm CMOS technology[J]. Journal of Solid-State Circuits,2015,50(2):573-585.

[10] Wang Jingqiu,Lin Fujiang,Chen Liang,et al. Inductorless SiGe BiCMOS optical receiver front end for 25Gb/s optical links[J]. Lecture Notes in Electrical Engineering,2018,423:553-560.

[11] Xuan Zhe,Ding Ran,Liu Yang,et al. A low-power hybrid-integrated 40-Gb/s optical receiver in silicon[J]. Transactions on Microwave Theory and Techniques,2018,66(1):589-595.

[12] Xue Zhe,He Jin,Fang Ya,et al. A 10-Gb/s inductorless optical receiver in 018 μm SiGe BiCMOS[J]. Microelectronics Journal,2019,86:34-39.

[13] Park S M,Yoo H J. 1.25-Gb/s regulated cascode CMOS transimpedance amplifier for gigabit ethernet applications[J]. Journal of Solid-State Circuits,2004,39(1):112-121.

[14] Chen W. Theory and Design of Broadband Matching Networks[M]. London:Institution of Engineering and Technology,1976.

[15] Kang Yuzhuo,Mao Luhong,Zhang Shilin,et al. A 13GHz 38mW differential front-end amplifier based on 0.18mm SiGe BiCMOS for 15Gb/s optical receiver[C]// International Conference on Solid-State and Integrated Circuit Technology. Xi’an,China,2012:1-3.

[16] Maxim A. A 54dBΩ 42dB 10Gb/s SiGe transimpedance-limiting amplifier using bootstrap photodiode capacitance neutralization and vertical threshold adjustment[J]. Journal of Solid-State Circuits,2007,42(9):1851-1864.

Design of an Analog Front-End Circuit for a 25Gb/s Optical Receiver in 40nm CMOS

Xie Sheng1,Min Chuang1,Wei Heng2,Mao Luhong3,Du Yongchao1

(1. School of Microelectronics,Tianjin University,Tianjin 300072,China;2. The 54th Research Institute of China Electronics Technology Group Corporation,Shijiazhuang 050000,China;3. School of Electrical and Information Engineering,Tianjin University,Tianjin 300072,China)

In this paper,a common-gate transimpedance amplifier(TIA)with an active feedback structure is proposed to effectively reduce voltage redundancy and increase bandwidth,shield the junction capacitance of a photodiode(PD),and adapt to a low supply voltage under an advanced process node. On the basis of the proposed structure,a pseudo-difference optical receiver analog front-end circuit with a rate of 25Gb/s is designed using the TSMC 40nm CMOS process. The optical receiver circuit includes a TIA,a limiting amplifier,a DC offset cancellation circuit,and an output buffer stage. The TIA adopts the common-gate amplifier with an active feedback structure. The limiting amplifier adopts an interleaved active feedback structure to improve the amplitude-frequency response flatness within the interested bandwidth,and theTfrequency multiplier serves as an output buffer stage to match the output impedance. Post-layout simulation results show that the designed analog front-end circuit has a −3dB bandwidth of 20.8GHz with a transimpedance gain of 59.6dBΩ while using a supply of 0.9V and a PD capacitance of 150fF. The power consumption is 46.6mW,and the core size of the chip is 600µm×440µm.

transimpedance amplifier;common-gate transimpedance amplifier;optical receiver;CMOStechnology

TN432

A

0493-2137(2020)12-1295-06

10.11784/tdxbz201909029

2019-09-11;

2019-11-27.

谢 生(1978— ),男,博士,副教授,xie_sheng06@tju.edu.cn.

谢 生,xie_sheng06@tju.edu.cn.

国家自然科学基金资助项目(61774113).

Supported by the National Natural Science Foundation of China(No. 61774113).

(责任编辑:王晓燕)