跨时钟域传递位数据的同步方法

高焕琦,岳亚杰,高俊锋

(哈尔滨理工大学软件与微电子学院,哈尔滨150080)

0 引言

随着微电子制造工艺技术的不断发展,数字集成电路(Integrated Circuit,IC)的集成度也越来越高。为了提高电子产品的竞争力,降低产品的开发成本,数字集成电路芯片集成的功能也越来越多,逐渐向着系统级芯片(System on Chip,SoC)的趋势发展[1]。系统级芯片也被称为片上系统,它是将各种不同功能的模块集成到一块芯片上。从设计角度上来说,片上系统的内部结构非常复杂。为了满足不同功能模块的工作需求,片上系统中的时钟信号源通常被划分为若干个时钟域(Clock Domain,CD)。通常情况下,功能模块不同,它们工作的时钟信号也不相同[2]。截至目前,采用单时钟域的片上系统已经非常少见,通常它的内部都集成了多种时钟域[3]。不同时钟域之间,时钟信号既可能是相关的,也可能是互不关联的。如果两种时钟信号之间存在数据传递通道,那么就会存在跨时钟域(Clock Domain Crossing,CDC)问题[4]。

如果数字信号在跨越不同时钟信号传递的时候,它就会被对方时钟域视为异步信号。如果不能很好地对这种异步信号进行处理,那么它就会产生亚稳态现象,严重影响电路系统的可靠性和稳定性。随着大规模集成电路的设计越来越复杂,跨时钟域传递数据信号的现象也越来越常见。因此,研究数据信号在不同时钟域之间的传递问题,已经成为数字集成电路系统设计者普遍关注的热点问题之一[5]。根据国内外的研究文献和工程实践经验,保持数据同步能够在很大程度上保证数据接收的准确性,这也是保障系统可靠性和稳定性的必要条件。

在片上系统设计中,跨时钟域传递位数据的情况最普遍,这也是处理多数据信号跨时钟域传递的技术基础。因此,本文以位信号为研究对象,探讨跨时钟域传递位数据问题的根源。在此基础上,根据实际应用的不同情况,探索各种可行的解决方案。

1 跨时钟域传递数据的电路模型

在数字集成电路系统中,无论在片上系统内部模块之间,还是在片上系统与外部设备之间,往往都需要进行通讯[6]。模块A 向模块B 传送数字信号A,同时接收来自模块B 的数字信号B,如图1 所示。在大多数情况下,模块A 和模块B 属于不同功能的模块,且工作在不同的时钟域。

众所周知,数字信号的存储和传递都是由触发器来完成。无论数字信号在两个模块之间的传递过程有多么复杂,它最终都是通过两个触发器来完成数据交接。因此,跨时钟域传递数据的问题可以通过两个触发器的电路模型来描述,如图2 所示。在本质上,研究解决跨时钟域传递数据的问题就转化为解决两个触发器在不同时钟信号下传递数据的问题。

图2 跨时钟域数据传递的电路模型

显而易见,如果触发器A 和触发器B 的时钟都来自相同的时钟源或同一个时钟域,那么就不存在跨时钟域传递数据的问题。因此,跨时钟域传递数据的问题根源是时钟信号之间存在显著差异。根据时钟差异的不同特点,跨时钟域的问题又可近一步划分为同步跨时钟域(Synchronous Clock Domain Crossings,SCDC)和异步跨时钟域(Asynchronous Clock Domain Crossings,ACDC)两种情况。

所谓同步跨时钟域,它是指触发器的时钟信号之间存在某种同步关系,即两者时钟信号之间是相关的,存在着固定的频率和相位关系。例如,一个时钟与它自身的分频时钟就具有固定的相位关系,在它们之间传递数据就属于同步跨时钟域的情况。与之对应,如果触发器的时钟信号之间没有必然的联系,那么就无法预知两者之间的关系,在它们之间传递数据就属于异步跨时钟域的情况。对于绝大多数集成电路系统设计而言,异步跨时钟域的情况非常普遍。因此,异步跨时钟域数据传递的处理方法是本文的重点研究内容。

2 跨时钟域传递数据问题的提出

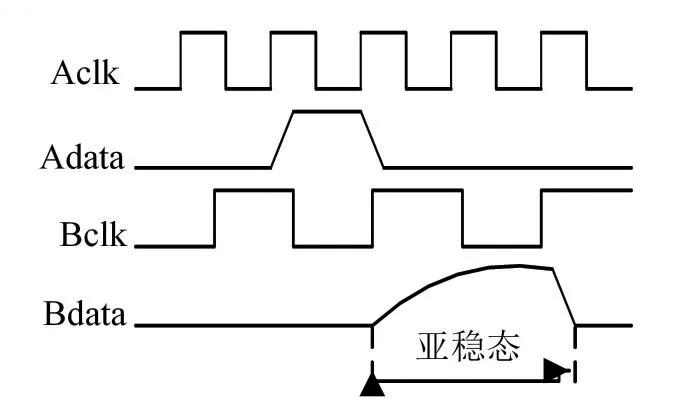

在图2 的电路模型中,假定Aclk 与Bclk 来自不同时钟域,如果触发器A 输出的信号data 到达触发器B的时间没有满足触发器B 的时序要求,例如建立时间(Setup Time,Tsu)或保持时间 Hold Time,Th),那么输出信号Bdata 就会出现一种界于逻辑1 和逻辑0 之间的状态[7]。这种状态就被称为亚稳态,亚稳态现象如图3 所示。导致亚稳态现象发生的根本原因是触发器B不能对输入数据data 进行有效采样。换句话说,当数据data 尚未保持稳定时,触发器B 采样的值是无效的。

图3 亚稳态现象

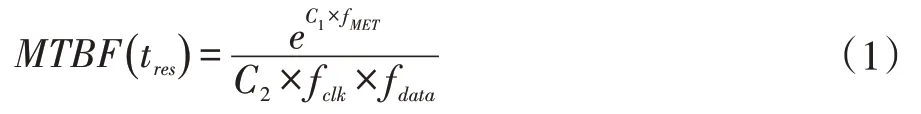

亚稳态现象发生的几率决定了数字集成电路系统的可靠性,它可以通过平均无故障时间(Mean Time Between Failures,MTBF)来评估。MTBF 表示触发器采样失败的时间间隔,它与系统频率和器件速度密切相关,它的计算方法如公式(1)所示。

其中,fMET是触发器能够在亚稳态输出而不会引起故障的最长时间,即有效的亚稳态最大分辨时间;fclk是触发器的时钟频率;fdata是输入数据的变化频率;C1和C2是与触发器相关的具体参数,它们通常是由触发器电气特性决定的常数,用于表征触发器翻转速度的快慢。

由此可见,亚稳态现象是在数字集成电路系统设计中无法避免的问题,它是由于触发器的固有属性造成的结果。如果设计方案的MTBF 值很大,那么该方案就被认为是可行的,设计的电路系统在实际工作中能够正常运行。否则,设计方案就会因为存在严重的亚稳态问题,而导致系统工作不稳定,甚至可能无法正常工作。

3 跨时钟域传递数据的处理方法

为了尽可能减少发生亚稳态的可能性,研究跨时钟域数据传递问题的解决方法就显得尤为重要。对某一个时钟域来说,它在操作输入的异步数据信号之前,必须首先对异步信号进行同步处理,使异步信号变成本时钟域的同步信号,然后再对数据进行后续的功能处理。这种处理方法是集成电路设计中经常采用的一种同步处理技术,它能够在很大程度上减少亚稳态的传播,增强数字集成电路系统的可靠性[8-10]。跨时钟域传递数据信号的问题非常复杂,因此数据信号同步处理的方法也不尽相同。根据跨时钟域传递数据的方向,同步处理方法大致分为单向同步和双向同步[11]。

3.1 单向同步的处理方法

在某个时钟域电路中,如果该电路仅仅对外部输入的异步数据信号进行同步处理,那么这种情况就属于单向同步。单向同步的处理方法是一种最基本的同步处理技术,它主要包含了电平同步法、边沿同步法和脉冲同步法三种方法。

(1)电平同步法

电平同步法也被称为双锁存器法,它的电路原理如图4 所示。在时钟域A 中,数据信号Adata 经过最后一级触发器输出数据信号data。数据信号data 直接进入时钟域B,中间不能存在任何组合逻辑电路。接着,在时钟域B 中连续使用两个触发器来锁存data 信号,并将同步后的数据信号Bdata 传递给时钟域B 中的后续电路。

图4 电平同步法

使用Verilog 硬件描述语言来实现电平同步法的关键代码如下所示:

当某个数据信号从慢时钟域电路向快时钟域电路传递时,它的电路时序仿真如图5 所示。从本质上看,电平同步法并不能完全消除亚稳态,而是减少了亚稳态的传播。理论研究表明:这种同步方法可以将亚稳态的出现几率降低到很小,使得MTBF 尽可能大,从而提高了系统的可靠性。

图5 电路时序仿真图

当从快时钟域电路传递数据信号到慢时钟域电路时,由于快时钟域中信号Adata 的宽度可能小于慢时钟域电路的一个采样周期,从而导致数据信号Adata不能被来自慢时钟域电路的时钟有效采样。如果快时钟域电路的时钟频率是慢时钟域电路的时钟频率N 倍时,那么快时钟域电路输出信号的宽度至少在快时钟域中保持N 个时钟周期。

(2)边沿同步法

在某些实际应用中,同步输出信号Bdata 并不一定与输入信号Adata 在波形上保持一致,而是一个与数据信号Adata 变化保持同步的脉冲信号。在这种情况下,同步处理方法通常采用边沿同步法,其中上升沿同步的电路原理如图6 所示。

图6 边沿同步法

从图中可以看出,边沿同步法是在电平同步法基础上,对后续时钟域电路增加了一部分边沿处理电路。每当Adata 出现上升沿的时候,Bdata 就输出一个同步脉冲信号。使用Verilog 硬件描述语言来实现边沿同步法的关键代码如下所示:

上升沿同步电路的时序仿真如图7 所示,从仿真波形上可以看出,边沿同步法也通常适用于从慢时钟域电路向快时钟域电路传递数据信号的情况。在输出信号上,边沿同步法输出的是同步脉冲信号,而电平同步法出的是同步电平信号。

图7 电路时序仿真图

(3)脉冲同步法

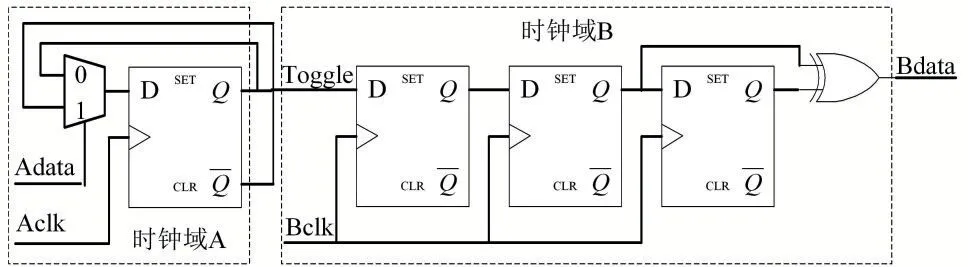

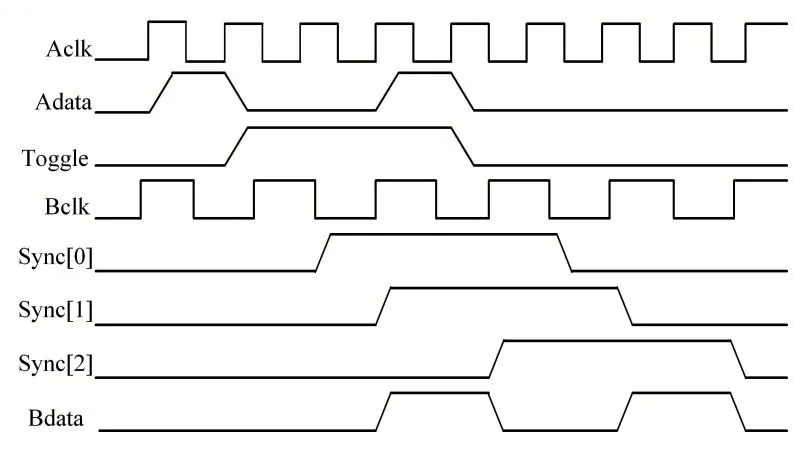

从前面的分析可以得知:从快时钟域电路传递数据信号到慢时钟域电路的时候,直接使用电平同步法和边沿同步法就不能满足同步处理的前提条件,可能存在采样失效的问题。为了解决这种问题,必须保证前级时钟域电路输出的数据信号必须具有足够长的保持时间,即至少在后级时钟域电路中保持一个时钟周期。在这种情况下,通常采用脉冲同步法,它的电路原理如图8 所示。

图8 脉冲同步法

从图中可以看出,脉冲同步法是在边沿同步法基础上,对前面时钟域电路增加了一部分边沿处理电路。脉冲同步法首先将前级时钟域电路的触发器输入数据Adata 由电平信号处理成一个时钟周期的脉冲信号,接着对脉冲信号进行翻转锁存,输出数据Toogle 具有足够长的数据保持时间,使之能够被后续时钟域电路中的时钟Bclk 进行有效采样。因此,脉冲同步法并不关心两个时钟域之间的关系,它可以适用于任何时钟域之间的数据传递。使用Verilog 硬件描述语言来实现脉冲同步法的关键代码如下所示:

脉冲同步电路的时序仿真如图9 所示,从时序分析可以得出:跨时钟域信号Adata 相邻两个脉冲信号的间隔至少为后续时钟域电路的两个时钟周期以上。同步输出数据信号Bdata 也是脉冲信号,它与Adata 的变化保持一致。

图9 电路时序仿真图

3.2 双向同步处理方法

所谓双向同步是指一个时钟域电路不仅对来自异步时钟域的数据信号进行同步处理,还要向原时钟域返回同步数据信号。据反馈信号的类型,双向同步方法主要分为信号同步法和握手同步法两种类型。从本质上说,双向同步处理方法是建立在单向同步方法的基础上。

(1)信号同步法

在某些应用中,数据传递之前通常要判断异步时钟域电路反馈的状态标志。只有得到异步时钟域电路的允许,它才会对数据进行同步处理。在同步数据输出之前,向原时钟域返回数据当前接收状态的标识。这种情况通常采用信号同步法,信号同步法的典型应用如图10 所示。

图10 信号同步法的功能图

使用Verilog 硬件描述语言来实现信号同步法的关键代码如下所示:

从功能图和实现代码可以分析出:时钟域A 首先锁存了Adata 和Alag 的异或值,然后再将它输出到时钟域B 进行同步处理。在同步处理过程中,它采用了脉冲同步法。接着时钟域B 又将同步后的数据重新返回到时钟域A 中,同时设置对应的状态标识Aflag。在返回状态标志时,它采用了边沿同步法,返回一个脉冲信号Aflag。

(2)握手同步法

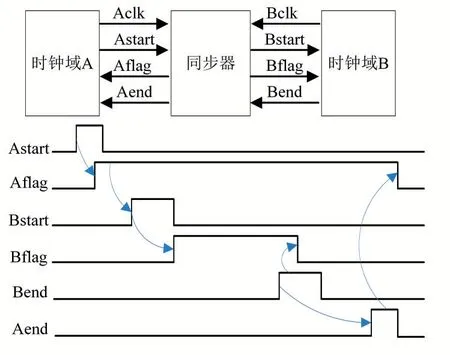

虽然信号同步法能够保证时钟域A 传递的数据能够被时钟域B 正确采样或有效接收,但是如果时钟域B 的功能处理电路比较复杂,可能出现以前接收的数据还没有被完全处理,而即将处理新数据的情况。在这种情况下,通常采用握手同步法,它的典型应用如图11 所示。

图11 握手同步法的功能图

使用Verilog 硬件描述语言来实现握手同步法的关键代码如下所示:

首先,当标志信号Aflag 为低电平时,时钟域A 声明它的请求信号并锁定Aflag 为高电平。接着时钟域B 检测到该请求信号有效后,声明它的响应信号Bstart,并锁存Bflag 为高电平。当时钟域B 电路完成后续的功能处理后,返回完成状态标识Bend,同时清除Bflag 的锁存标志。Bend 被时钟域A 同步处理为Aend,同时清零Aflag。握手同步法的关键代码如下所示,其中Astart 和Bend 都必须是各自时钟域中的脉冲信号。

4 结语

在大规模集成电路设计中,异步电路之间的数据通信是一个设计重点和难点问题。针对不同的应用场合,选择适当的同步方法不仅能有效减少亚稳态问题的传播,还能显著降低产品设计成本。本文以位信号为研究对象,在前人研究的基础上,总结归纳了跨时钟域传递位数据问题的解决方法,即对跨时钟域传递数据进行同步处理。根据跨时钟域传递数据的方向,同步处理方法大致分为单向同步和双向同步。

电平同步法、边沿同步法和脉冲同步法是三种基础的单向同步处理方法。电平同步法连续使用两级触发器锁存跨时钟域的数据信号,从而实现数据同步。使用这种同步方法的前提条件是输出数据的时钟域要比接收数据的时钟域更快的时钟频率。电平同步法可以降低亚稳态的出现机率,增大MTBF 的数值,从而提高了系统的稳定性和可靠性。边沿同步法是以电平同步法为核心,通过增加部分后级电路来实现输出脉冲信号与原数据信号在波形变化上保持一致。为了克服电平同步法的使用限制,脉冲同步法在边沿同步法的基础上,通过增加部分前级电路来锁存输入的脉冲信号,从而使它可以适用于任何时钟域之间的数据传递。

信号同步法和握手同步法是两种具有代表性的双向同步方法。信号同步法仅仅关心后续时钟域电路是否接收到发送的数据,而并不理会后续时钟域电路能否及时处理这些数据。为了保证数据传递的准确性和可靠性,握手同步法在信号同步法的基础上,通过增加处理状态标志来判断是否继续发送新数据。