基于LHB155304的高速1553B 总线RT 设计与实现

甄国涌, 关瑞云, 武慧军

(中北大学仪器与电子学院,太原030051)

0 引 言

1553B总线是一种指令/响应式串行总线标准。在国内已得到广泛应用。1553B总线抗干扰能力强、实时性好,且采用双冗余备份设计,能够显著提高数据传输的可靠性[1]。近年来,随着航空综合电子系统性能需求的不断提高,国际上掀起了高速1553总线研究的高潮,其目的是在现有的物理传输方式下突破1553B 总线1 Mbit/s的传输速率[2]。我国高速1553B总线控制器LHB155304,在不改变其原有传输方式、网络结构及传输协议的情况下,传输速率可达4 Mbit/s[3]。高性能浮点DSP TMS320C6713是专为高性能、数字密集型电力电子控制而设计的,与LHB155304总线控制器直接通信的方式提高了数据传输的效率和可靠性,LHB155304工作电平为3.3 V,相较BU-61580而言,与DSP通信无须电平转换,使设计过程更为简单,也降低了设计的复杂程度和设备体积。

1 LHB155304工作原理

LHB155304采用了和BU-61580全兼容的软件界面,相对于BU-61580而言,LHB155304提供了更加灵活高效的主机接口方式,增大了内部存储器空间,不仅可以实现BU-61580支持的接口方式,还具有主机访问等待时间更短的特点。LHB155304内部有16 Kbyte的共享存储器。通过独特的设计技术,LHB155304的主机接口和内部协议接口对共享存储器的访问不会发生冲突,主机任何时候都能访问总线[5]。

LHB155304是一款4 Mbit/s 1553总线控制器混合电路,集成了时钟与复位管理单元、双曼彻斯特Ⅱ型编译码器单元、BC/RT/MT多协议处理单元、存储管理单元、中断管理单元、主机接口单元和16 Kbyte×16 bit的双端口存储器单元,完整实现了1553B协议中规定的总线控制器(Bus Controller,BC)、远程终端(Remote Terminal,RT)、总线监视器(Bus Monitor,MT),可实现具有双冗余总线通道的4 Mbit/s1553总线通信。

1553B总线上的信息是以消息的形式调制成曼彻斯特码进行传输的,每条消息最长由32个字组成,所有的字分为3类:命令字、数据字和状态字[6]。LHB155304的1553B总线特性见表1。

表1 1553B数据总线特性

2 1553B总线接口硬件电路设计

LHB155304总线控制器(ACE)通过不同的硬件配置工作于不同模式。8/16 bit缓冲零等待/非零等待是最常用的工作模式。每种模式的硬件设计、软件读写访问时序各不相同。LHB155304灵活的处理器接口允许其直接连接32bitDSP处理器TMS320C6713,文中给出了LHB155304的16 bit缓冲非零等待模式的硬件设计。TMS320C6713与LHB155304的硬件连接图如图1所示。

图1 DSP与LHB155304硬件连接原理图

由图1可见,DSP通过SELECTn、STRBDn、MEM_REGn、RD_WRn信号启动对LHB155304的内部寄存器或存储器的访问,要存取内部寄存器或存储器SELECTn必须为低电平,STRBDn信号与SELECTn相连控制着访问周期的长度[7]。使用6713的GPI/O(通用输入输出)对MEM_REGn信号进行控制,访问存储器时MEM_REGn为高电平,访问寄存器时MEM_REGn为低电平。POLARITY_SEL用来选择RD/WRn的极性,当POLARITY_SEL 接逻辑‘1’时,RD/WRn 低电平为写,高电平为读;当POLARITY_SEL接逻辑‘0’时,RD/WRn高电平为写,低电平为读。将LHB155304的RAM地址与TMS320C6713的CE3地址空间(0xB0000000-0XBFFFFFFF)映射,地址线A[11:0]与6713 地址线A[13:2]相连进行地址译码,数据线D[15:0]与6713 数据线D[15:0]相连进行数据读写,图中RT地址的配置通过外接上/下拉电阻设置,如RT地址为22,即RTAD4-RTAD0=10110,1的个数为奇数,则RTADP=0。LHB155304的READYn信号低有效,读操作时,READYn为低表示D15-D00上的数据已经准备好,写操作时,READYn为低表示数据已写入寄存器或数据存储器。

LHB155304读写时序如图2所示。

图2 LHB155304读写时序

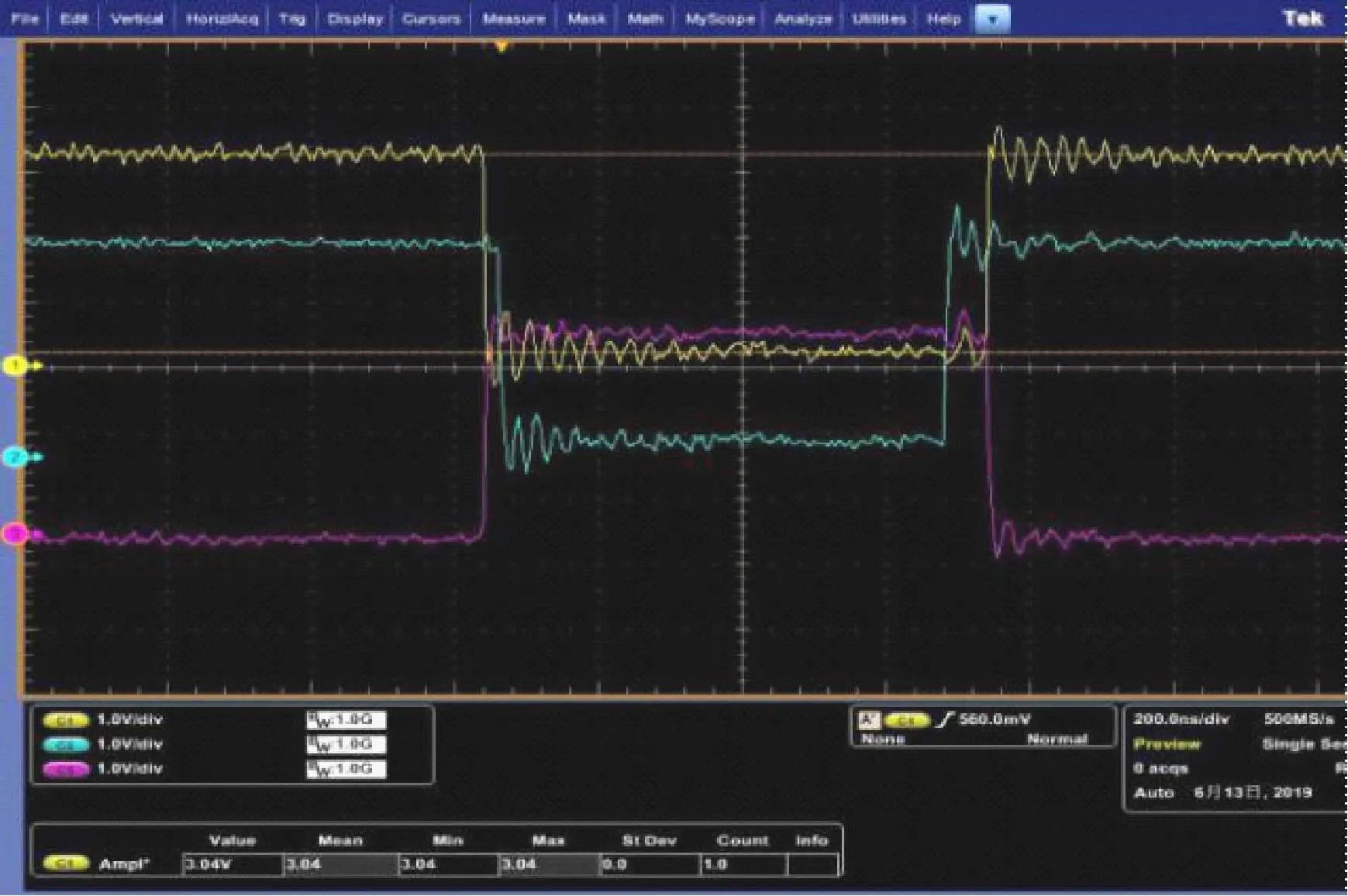

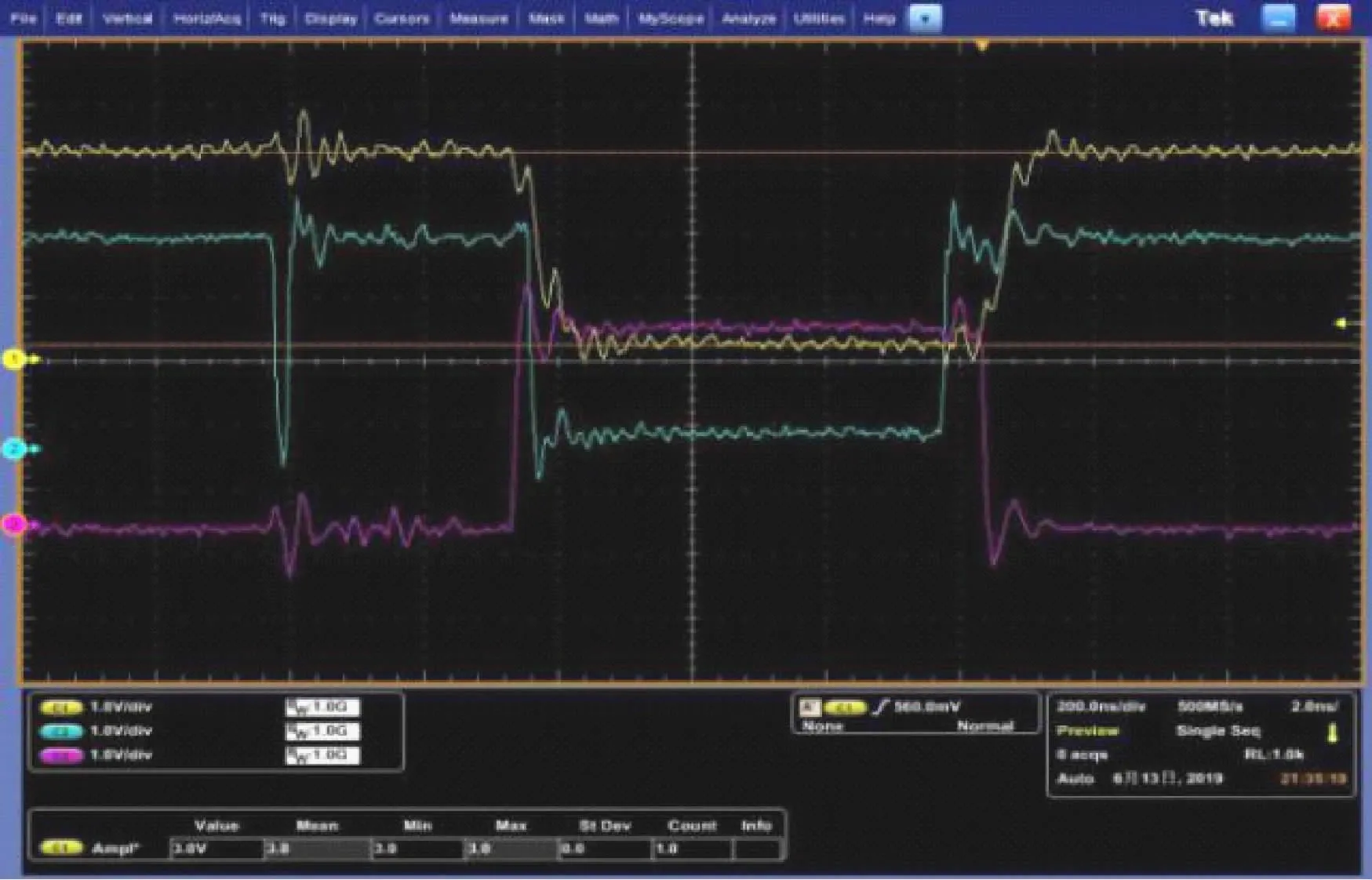

LHB155304进行写操作时,在SELECTn和STRBDn同时为低的第1个时钟上升沿锁存WE信号,在第2个时钟下降沿锁存地址和数据,根据DSP的EMIF接口时序(见图3),第1条波形为CE信号,第3条线为锁存数据,数据在锁存时并未达到稳定,导致锁存出错,故将SELECTn信号对地接1 nF电容,与10 kΩ电阻组成RC延时电路,延时时间T=-RCln((E -V)/E)≈33 ns,其中E =5 V 为串联电阻和电容之间的电压,V=1.2 V为电容间要达到的电压,延时33 ns等待数据稳定后进行锁存,保证数据读写的可靠性,延时后波形如图4所示。

图3 未加延时时序波形

3 1553B软件设计

3.1 LHB155304 RT模式的实现

图4 增加延时时序波形

配置和设置17个内部操作寄存器是软件接口设计的关键,对1553B数据通信具有重要意义[8]。设计中将LHB155304配置为RT模式,1553B通信由BC控制,BC发送包含特定RT地址的命令字,以便在总线上发送或接收数据。消息传输BC到RT时,如图5指令字传输格式中T/R bit设置为逻辑‘0’,RT接收指定个数的数据字并返回状态字,RT到BC进行传输时,T/R位设置为逻辑‘1’,RT传输一个状态字,并在其后传输数据字[9]。

图5 1553B总线字格式

LHB155304在RT模式下的工作流程如图6所示。

图6 LHB155304 RT模式工作过程

首先初始化配置LHB155304为RT工作模式,LHB155304作为RT远程终端的配置过程见表2。等待BC发送的命令字,判断命令字中的T/R位,T/R=1则根据指令字中的RT子地址发送相应的Data Block中的数据;T/R=0则将接收到的数据存储到堆栈中,在发送/接收动作完成后发出RT状态字并等待下一BC指令字,在接收数据的动作完成后,向CPU发出中断请求,请求CPU处理接收到的数据[10]。

表2 LHB15504 RT初始化配置流程

3.2 中断的实现

DSP主程序通过中断方式处理1553B数据。通过总线协议芯片LHB155304向DSP发送中断,DSP通过共享的4 KB RAM接收数据。DSP在RAM中传输接收到的数据并将其存储。将DSP接收到的数据传输到命令变量中,进行实时的数字控制回路处理[11-12]。

1553B使用DSP的外部中断INT5,LHB155304为下降沿中断[14],TMS320C6713中断服务程序如下:

Interrupt void RT_1553(void)

{

Receive_RT();//LHB155304 作为RT 中断接收数据

}

在进入中断服务程序前需先进行中断初始化[12-15],初始化函数如下:

voidinterrupt_init()

{

*(volatile short*)0x019C0008=0x0002

//EXTPOL寄存器配置1553中断下降沿

IRQ_setVecs(vectors);//指向定义的中断向量表

IRQ_map(IRQ_EVT_EXTINT5,5);

//映射事件到指定的物理中断号

IRQ_clear(IRQ_EVT_EXTINT5);

IRQ_enable(IRQ_EVT_EXTINT5);//中断使能

IRQ_globalEnable();

IRQ_nmiEnable();

}

4 性能测试与验证

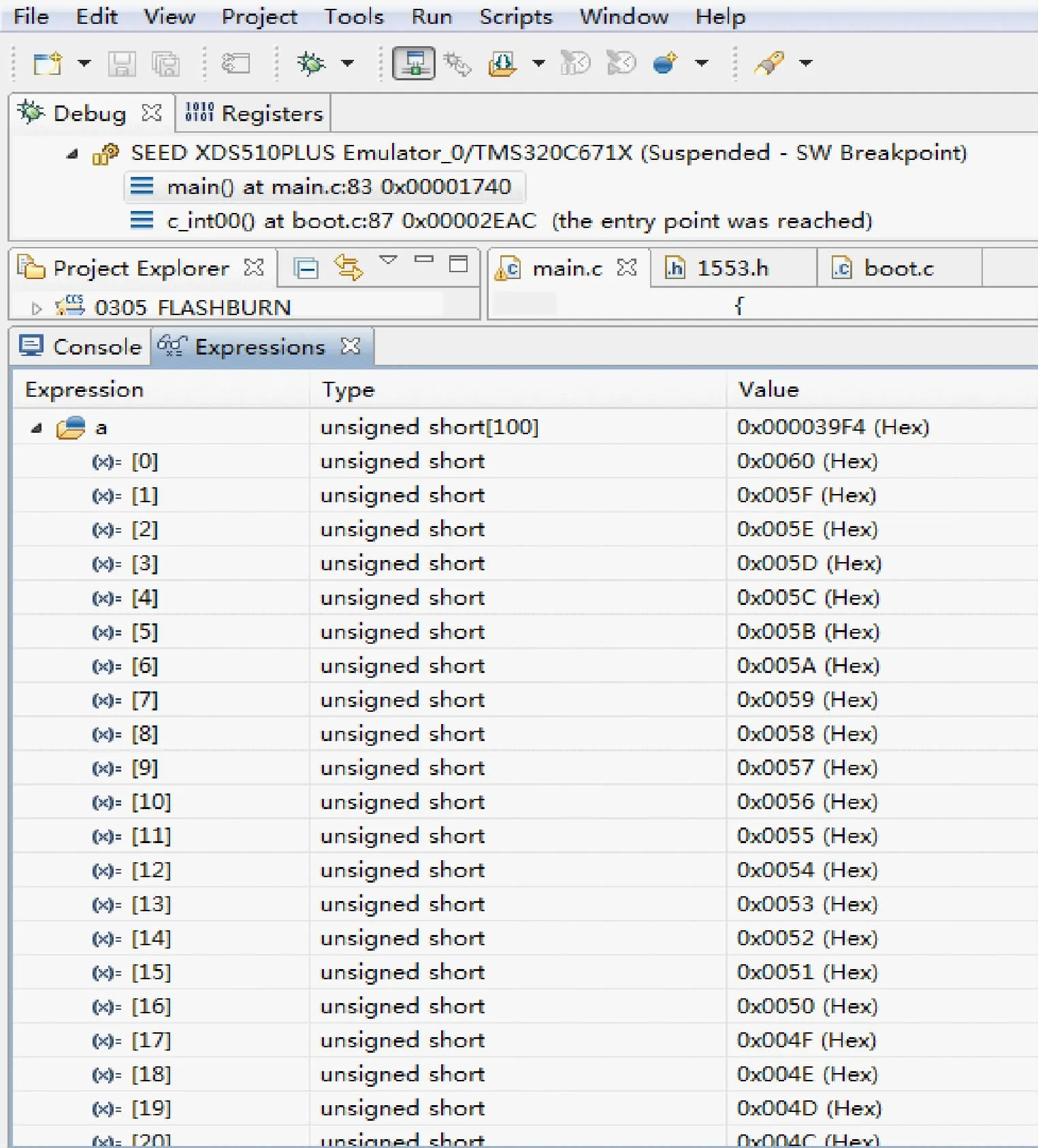

通过DSP芯片TMS320C6713对LHB155304寄存器与存储器的读写操作进行了测试,向LHB155304存储器地址空间0x0000开始写入自减数,将写入数据读出,对第2节中CE信号增加延时前后分别进行了读写测试,观察测试结果。

如图7所示,CE信号未加延时读写数据出现误码。

图7 CE信号未加延时读出数据

如图8所示,CE信号增加延时后读写数据正确。

图8 CE信号增加加延时后读出数据

对LHB155304的读写测试成功后,利用上位机软件配置为4 Mbit/s BC工作模式,对LHB155304 RT模式下的工作状态进行了测试,BC发送一条自检测试指令“0x5C03”,该指令字表示RT地址为11,RT作为接收端,发送子地址为15,方式指令为“00111”,LHB155304作为RT接收到该消息,若自检成功则将“0xAAAA”写入发送子地址15返回给BC,如图9所示返回指令正确,表明该1553B通信接口在4 Mbit/s传输速率下工作正常。

图9 BC读取RT发送的消息

5 结 语

本文将DSP强大的数据处理能力与1553B总线分布式处理、集中控制和实时响应的特点相结合[16],具有系统集成度高、处理速度快及通用性强的特点,利用DSP EMIF接口直接控制LHB155304总线控制器实现1553B通信,简化了设计过程,降低了设计难度,同时LHB155304总线控制器传输速率达到了4 Mbit/s,突破了目前1553B总线1 Mbit/s传输速率的局限性,通过对EMIF接口与LHB155304总线控制器的读写时序匹配,实现了该1553B接口的高速读写,经过后期测试表明,文中设计的1553B通信接口传输速率快,实时性好,通用性强,可用于诸多1553B通信的系统中。