嵌入式操作系统中基于MIPS处理器的内存管理机制实现

郭 锋,王宏伟,黄保垒,齐晓斌

(中国航空工业集团公司西安航空计算技术研究所,陕西 西安 710065)

1 嵌入式操作系统在内存管理中的特点

嵌入式操作系统通常具有实时性强、安全性高、资源受限等特点,因此,大部分嵌入式操作系统在内存管理方面具有以下特征:

(1)对存储器采用实地址平板方式进行管理,操作系统和用户应用都运行在核心态。当需要操作系统接管时,避免了用户态向核心态切换带来的开销,确保了系统响应的实时性。

(2)对堆空间统一进行管理,系统堆和用户堆不作区分,降低了系统维护的复杂度。

(3)提供页面管理功能,支持内存管理单元(Memory Management Unit,MMU)存储保护,防止用户对关键内存进行非法访问,保证了系统的安全。

2 MIPS处理器内存管理的特点

2.1 MIPS的基本地址空间

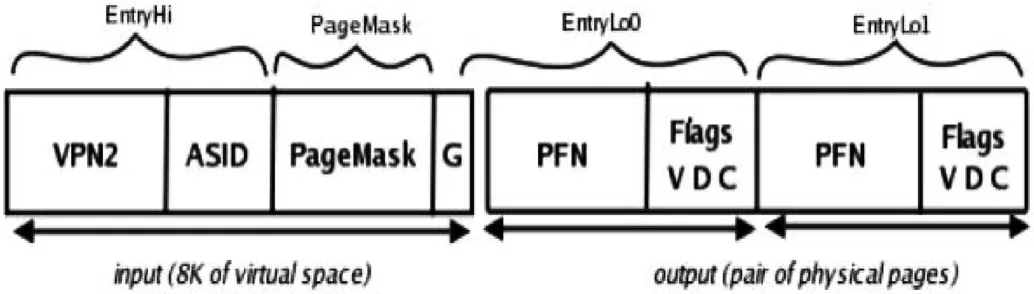

无内部互锁流水级的微处理器(Microprocessor without Interlocked Pipelined Stages,MIPS)运行在用户态或核心态,在32位模式下,程序地址空间被划分为4个区域。在不同模式下,程序可以访问的地址空间是有区别的:用户态只能访问低2G的地址空间,核心态可以访问所有4G的地址空间[1],如图1所示。根据各区域地址空间的特点,对空间访问属性进行总结:(1)Kuseg,只有用户态可以访问,经过cache,需要MMU映射。

图1 32位模式下MIPS处理器的地址空间

(2)Kseg0,用户态和核心态都可访问,经过cache,不需要MMU映射。

(3)Kseg1,用户态和核心态都可访问,不经过cache,不需要MMU映射。

(4)Kseg2,用户态和核心态都可访问,经过cache,需要MMU映射。

2.2 MIPS处理器的内存管理机制

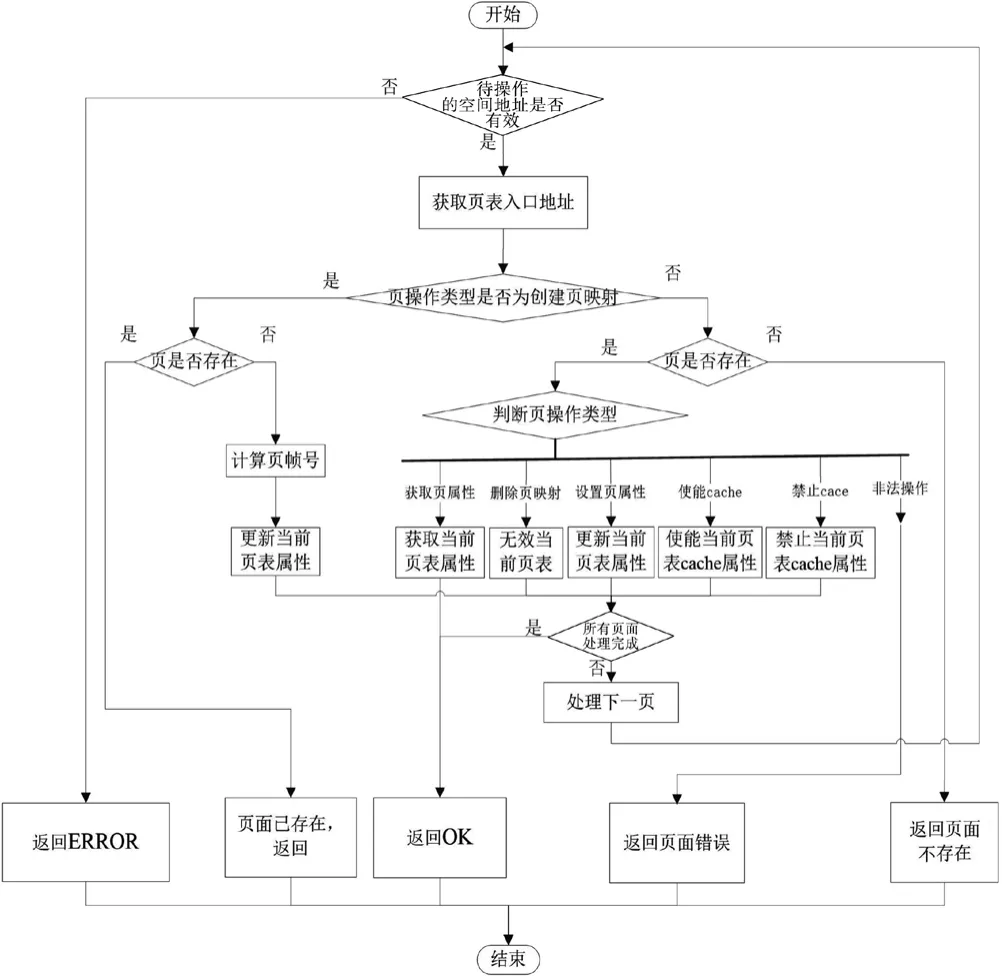

现在的计算机都是通过MMU把程序地址转换成存储器的物理地址,转译后备缓冲器(Translation Lookaside Buffer,TLB)是MMU中一个重要的加速转换部件。MIPS处理器采用双倍存储的TLB管理,每一个TLB表项可以容纳一对相邻的虚拟页面对应的两个单独的物理地址,TLB可管理的页大小为4~16 KB。4 K页大小的TLB结构,输入域中VPN2为虚拟页号,ASID为地址空间标识,PageMask用于设置页大小,G位表示进程共享的地址空间;输出域中的PFN对应两个连续的奇偶物理页,flag域包含3个页属性,分别为页有效(V)、写允许(D)和页的cache属性(C)。MIPS的TLB表项如图2所示。

图2 MIPS的TLB表项

3 嵌入式操作系统中MIPS处理器的内存管理机制实现

3.1 页面设计

传统的操作系统采用4 K页大小。在32位地址空间模式下,若采用一级页表方式,需要连续的4 MB内存来存放页表,这对内存资源的要求比较高;若采用二级页表的方式,最大连续空间只需要4 KB,虽然对存储的要求大大降低,但是在TLB未命中需要换页时,多了一次访存操作,系统的效率降低,二级页表也有可能引发TLB二次充填问题,增加了系统维护的复杂程度[2]。

在实际使用中,很少有程序用到整个32位的寻址空间,多数程序在自己的地址空间内部有巨大的空洞。基于这一特性,在地址映射时,避免对空洞的映射,可以有效减少页表带来的内存开销。

综合考虑存储效率与访问效率,本研究使用16 K页大小、一级页表的方式进行页面管理。在内存占用率方面,考虑到kseg0和kseg1地址区域不需要进行映射,每个页表项可以映射两个物理地址,因此,最多需要存储96 K 6个页表项,每个页表项占用4 B空间,最多需要384 KB的地址空间用于存储页表,如果能有效避开程序中的空洞映射,存储页表所需的空间还会大大减少。16 K页表比4 K页表能容纳更多的内容,因此,可以减少换页的次数,从而减少时间开销[3]。采用这种方式,既减少了换页时访存次数带来的时间开销,又可以避免TLB二次充填问题,因此,是一种合理的设计方案。

3.2 基于MMU的内存管理

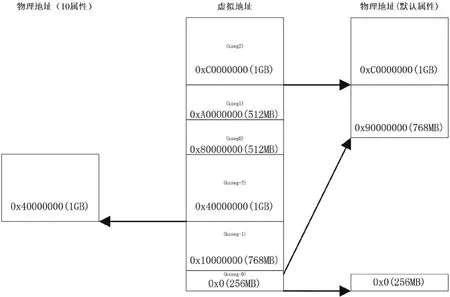

需要MMU进行管理的地址空间只能位于kseg2或kuseg区域,只有合法的地址空间才允许进行页面操作。对页面的操作主要有以下6种情况:(1)创建页映射;(2)删除页映射;(3)获取页属性;(4)设置页属性;(5)使能cache属性;(6)禁止cache属性。除了创建页映射外,其他几种操作仅当页面存在时才有效。页属性与上文中的描述一致,对cache属性的操作也属于设置页属性的范畴。对页面cache的设置是用户比较关心的操作,因此,将其单独提取出来。基于MMU的内存管理流程如图3所示。

图3 基于MMU的内存管理流程

3.3 嵌入式操作系统中的地址映射与虚实地址转换

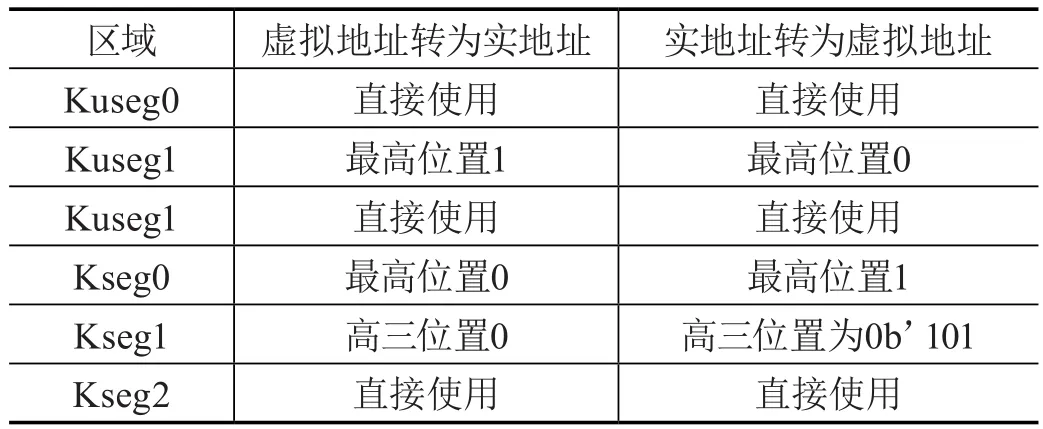

在嵌入式操作系统中MIPS处理器的地址映射中,kseg0区域和kseg1区域直接映射到低端物理地址,kseg2和kuseg区域可以映射到任意空间。以LS2H处理器地址映射为例,kseg0空间和kseg1空间都映射到0x0地址空间,其他地址空间的映射关系如图4所示[4]。以0地址开始的第一个页面不做映射,可以避免用户使用空指针带来的问题。

图4 一种MIPS处理器的地址映射关系

针对上述地址映射关系,在虚拟地址和实地址进行转换时,不同区域区别对待,其中,kuseg区域被分为3个部分,分别为kuseg0,kuseg1和kuseg2,具体转换方法如表1所示。

表1 虚实地址转换

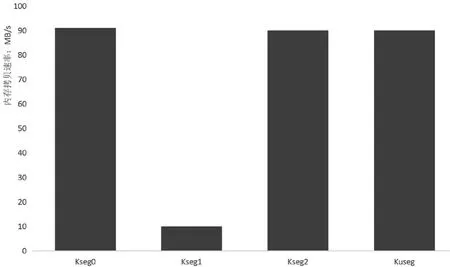

4 内存拷贝速率测试结果

本研究设计并实现了一种在嵌入式操作系统中基于MIPS处理器的存管理方法,在LS2H开发平台完成了测试。经测试验证,内存管理部分的功能基本正确。对各区域的内存拷贝速率进行了测量,如图5所示,使用MMU的区域存储访问速度和非映射cache区域的访问速率基本相当,表明MMU的功能正确且性能符合系统需求。kseg1区域的访问速度远小于其他区域,是因为该区域空间的访问是不经过cache的。

图5 内存拷贝速率测试结果