基于Artix-7 系列的eMMC 阵列控制器设计与实现

孙 巍,吕 勇,马士全

(1.中国人民解放军海军潜艇学院,青岛,266199;2.青岛海洋科学与技术试点国家实验室,青岛,266237)

引 言

eMMC(embedded multimediacard)是一种嵌入式存储器,其内部包含闪存、标准接口以及控制芯片,早期主要应用于手机、平板电脑等移动设备[1]。随着控制协议和生产工艺的不断升级,2013年三星电子率先推出了基于eMMC 5.0 标准的内存产品,其速度最高可达到400 MB/s[2]。目前Samsung,Micron 以及Sandisk等国外公司在eMMC芯片供应方面依旧占据主导地位,国内经过自主研发也实现了批量生产[3]。

随着eMMC 技术的不断成熟和完善,面向各类应用领域的嵌入式存储系统逐渐采用eMMC 作为存储单元。与此同时,eMMC 控制器开发也逐渐受到业界内的广泛关注。Arasan 公司作为JEDEC eMMC标准制定的组织成员已提出eMMC 4.5、eMMC 5.0 以及eMMC 5.1 协议的IP 解决方案,近期还将提供基于台积电7 nm 工艺技术的eMMC IP 解决方案。国内在相关方面也投入了大量研究工作,不仅提出可应用于图像采集、视频存储的eMMC 控制器方案[4-5],还实现了可集成于雷达、航天、武器发射等重要控制系统的eMMC 存储单元[6-8]。目前通用的eMMC IP 解决方案对外开放度十分有限,自主设计一种安全可靠的eMMC 控制器依然十分重要。为此,本文参照eMMC 5.1 协议在Artix-7 系列开发平台上实现了一种用户可配置的eMMC 阵列控制器,便于用户根据实际需要选择合适的工作频率和阵列操控方式。

1 操作原理

eMMC 阵列控制器中包含的操作主要有开放终点多块写、预定块数多块读以及数据擦除,下面分别介绍每种操作的基本原理和技术关键点。

1.1 开放终点多块写

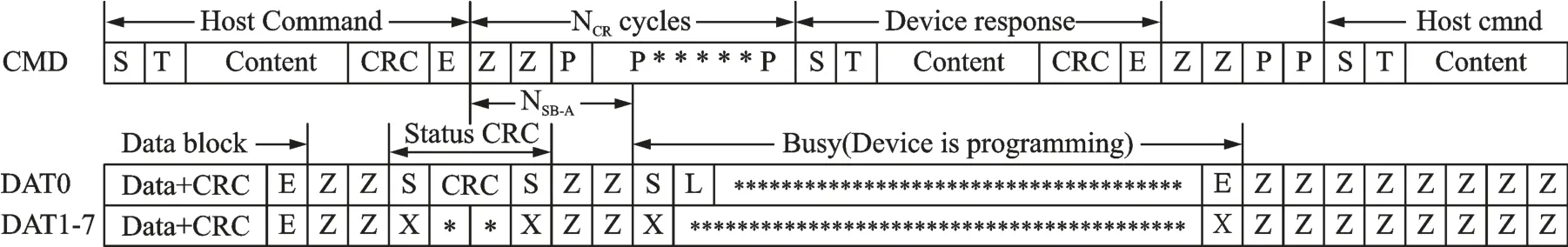

eMMC多块写主要分为预定块数多块写、开放终点多块写以及可靠型多块写[9],其中开放终点多块写的操作原理是让eMMC对数据进行连续接收和编程,直至接收到停止命令才终止传输过程[10]。相比于其他两种方式,不需要反复发送操作命令,数据写入效率较高。虽然开放终点式操作具有很强的灵活性,但在设计方面需要特别关注停止命令的发送时机。eMMC在接收数据过程中首先会判断数据的起始位,然后检验数据尾部的CRC校验结果,最后再对数据进行编程。根据eMMC 5.1协议的多块写停止时序,如图1所示。eMMC控制器可以在发送最后一个数据的过程中发出停止命令,使得eMMC在CRC校验结束后快速进入忙状态,有利于eMMC在数据写入完成的情况下及时结束多块写过程,为响应后续的其他操作命令节约时间。

图1 多块写停止时序图Fig.1 Timing diagram of multi-block writing stop

1.2 预定块数多块读

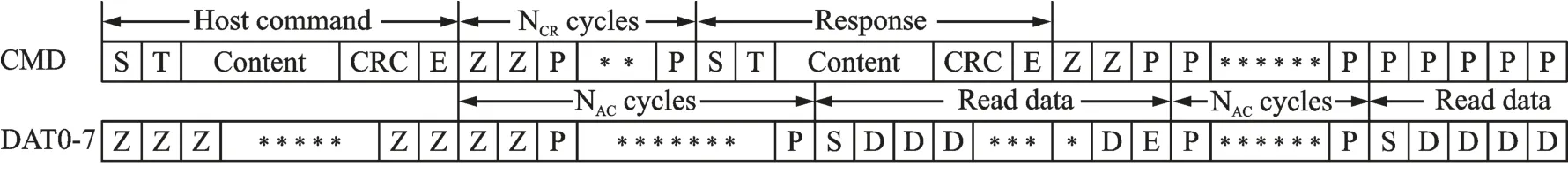

eMMC 读操作可分为预定块数多块读和开放终点多块读,其中预定块数多块读的操作原理是当数据传输量达到预定块数时传输自动停止[11],其操作时序如图2 所示。在eMMC 阵列多块读过程中更需要关注对读出数据的处理,为了检验eMMC 与FPGA 之间数据传输的准确性,本文在数据接收模块中加入了CRC16 校验模块,对从eMMC 读出的数据进行实时校验,及时发现传输异常,当数据发生错误时其他主控模块可以尝试重新读取或者数据舍弃等其他控制操作。当并行读取数据时,不同eMMC 芯片之间由于存在性能差异,通常会导致读出的数据无法直接对齐。最有效的处理方法是借助DDR3 对数据预先缓存,然后调整eMMC 读操作长度,使得eMMC 阵列读速率与DDR3 写速率达到匹配。为了使得控制器可以不依赖于DDR3,本文采用逐片操控方式实现eMMC 阵列的预设块数多块读,相比于并行操控速率较低,在DDR3 出现异常时可作为一种数据导出的备用方案。

1.3 数据擦除

数据擦除是eMMC 控制器设计中不可缺少的重要操作。eMMC 启动擦除需要按顺序依次发送CMD35、CMD36 以及 CMD38[12],如果 eMMC 没有按照顺序正确接收 CMD35、CMD36 和 CMD38,主控制器必须从CMD35 命令重新开始发送。如果CMD35 或者CMD36 地址参数超出eMMC 芯片的最大地址,eMMC 会反馈对应的错误类型并重置发送序列。eMMC 在擦除过程中会通过拉低DAT0 线来告知主控当前正处于忙状态,擦除完成后DAT0 会重新拉高,在eMMC 阵列擦除过程中可以根据每片eMMC 的DAT0 反馈来判断擦除是否完全结束。

2 总体设计

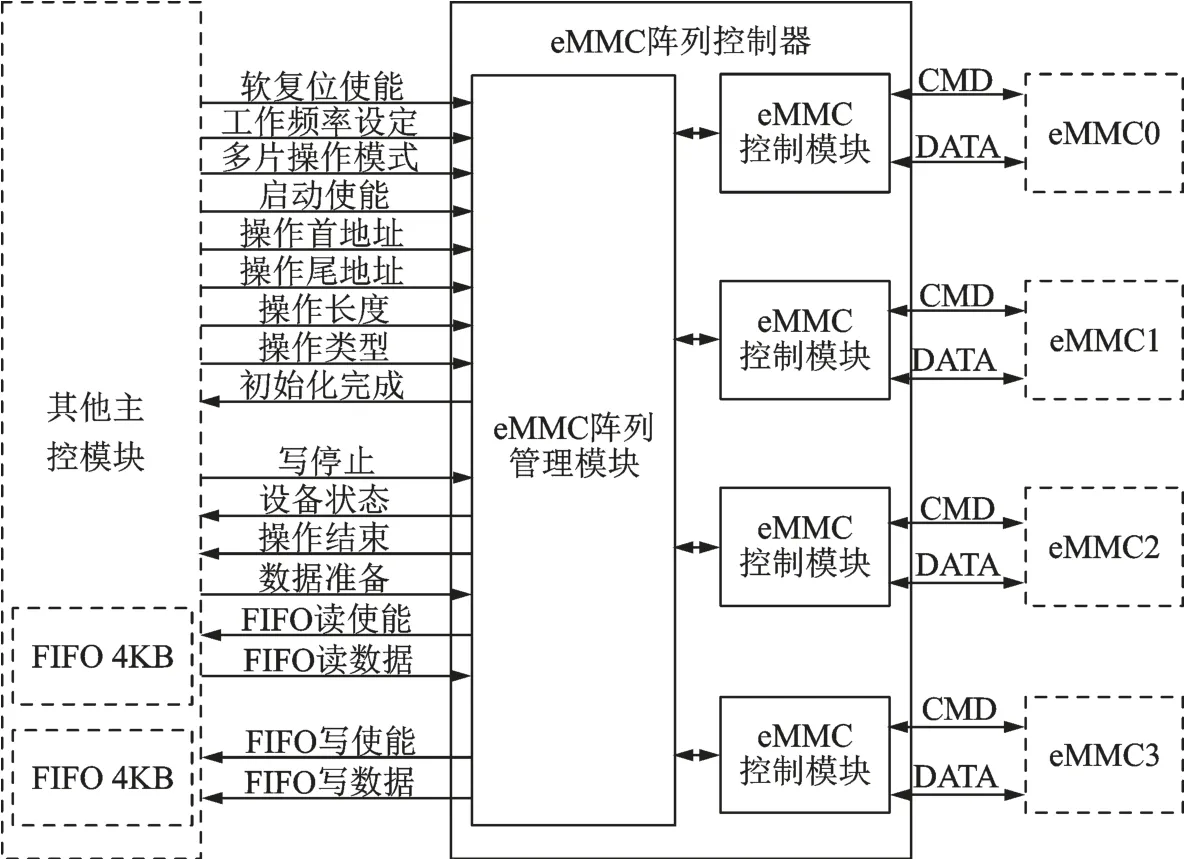

本文所设计的eMMC 阵列控制器以eMMC 5.1 协议为基础,实现了多种灵活的配置方式,内部结构如图3 所示。用户利用软复位使能可以实现eMMC 阵列的复位操作,在复位时还可以利用工作频率设定接口和多片操作模式接口重新选择eMMC 阵列的工作频率和阵列操控方式。此外,用户还可利用操作首地址、操作长度以及操作类型等3 种配置接口实现eMMC 阵列的单块读写,预定块数多块读写以及开放终点多块读写,如果需要数据擦除还需要配置操作尾地址。为了提高实际使用效率,本文将单片eMMC 的控制逻辑封装于eMMC 控制模块,有利于用户根据实际eMMC 的使用数量修改eMMC控制模块的实例化数量,图3 展示了应用于4 片eMMC 的配置情况。本文还将阵列控制逻辑封装于eMMC 阵列管理模块,一方面处理来自其他主控模块的操作参数,明确操作任务后直接控制每个eMMC 控制模块。另一方面,其他主控模块可通过读取工作状态来实时监测eMMC 阵列的工作状态,有利于及时处理异常情况,保证eMMC 阵列控制器在长时间工作过程中始终处于可控状态。

图3 eMMC 阵列控制器结构框图Fig.3 Block diagram of eMMC array controller

3 eMMC 阵列管理模块

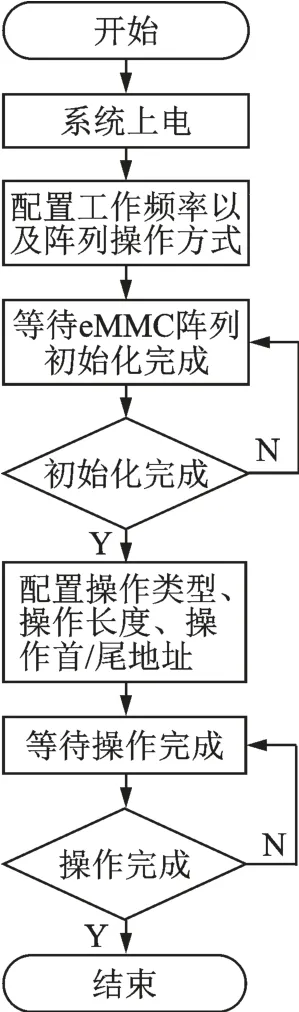

eMMC 阵列管理模块主要负责用户与eMMC 阵列之间的信息交互,其工作流程如图4 所示。首先在上电初始化阶段,eMMC 阵列管理模块会根据设定的工作频率和阵列操作方式完成对eMMC 阵列的初始化操作,并等待每个eMMC 控制模块的初始化结束。初始化全部结束后向其他主控模块反馈初始化完成信号,此时其他主控模块可以开始配置参数。其他主控模块发出启动使能信号后,eMMC 阵列管理模块根据阵列操作方式继续将参数下发到各个eMMC 控制模块,等待所有操作结束后向其他主控模块反馈操作结束信号,接下来如果需要切换工作时钟或者阵列操作方式可通过软复位信号来实现重新配置。如果继续在当前状态下工作可直接重新设置操作的起始地址、终止地址、操作长度以及操作类型。接下来,介绍eMMC 阵列管理模块的工作参数配置接口和数据传输控制接口。

图4 eMMC 阵列管理模块流程图Fig.4 eMMC array control module flowchart

3.1 工作参数配置接口

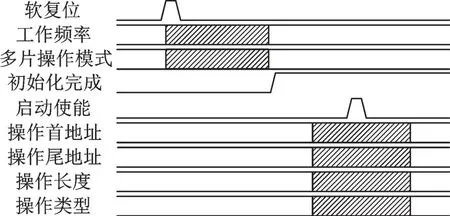

为了实现工作参数的实时配置,本文设计了一种操作便捷的工作参数配置接口,其接口操作时序如图5 所示。首先在复位阶段其他主控模块需要在发出软复位信号后保持工作频率和阵列操作方式参数有效,直到eMMC阵列初始化完成。eMMC 阵列初始化结束后,其他主控模块可以在操作参数有效期间发出启动使能,eMMC 阵列管理模块根据启动使能的上升沿获取操作首地址、操作尾地址、块的数量、操作类型等参数。

3.2 数据传输控制接口

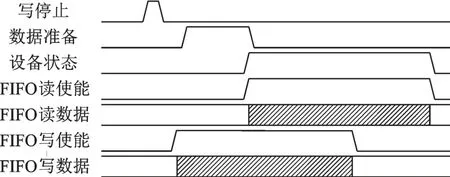

为了实现eMMC 阵列的开放终点多块写,本文在FIFO 读写控制信号的基础上增设写停止、数据准备以及设备状态等信号,控制接口操作时序图如图6 所示。eMMC 阵列管理模块在写数据操作前需要等待其他主控模块的数据准备信号,数据准备好后立即发出FIFO 读使能并向其他主控模块反馈当前设备正处于数据写入状态,其他主控模块接收到设备忙信号后可释放数据准备信号。当开放终点多块写结束时,其他主控模块需要在数据准备信号有效前发出写停止信号,避免向eMMC 阵列写入多余数据。当其他主控模块需要读eMMC 阵列数据时,eMMC 阵列管理模块按照阵列操作方式将数据与写FIFO 使能信号同步发送,保证数据能够准确写入FIFO 寄存器。

图5 参数配置接口操作时序图Fig.5 Timing diagram of parameter configuration interface operation

图6 数据传输控制接口操作时序图Fig.6 Timing diagram of data transmission control interface operation

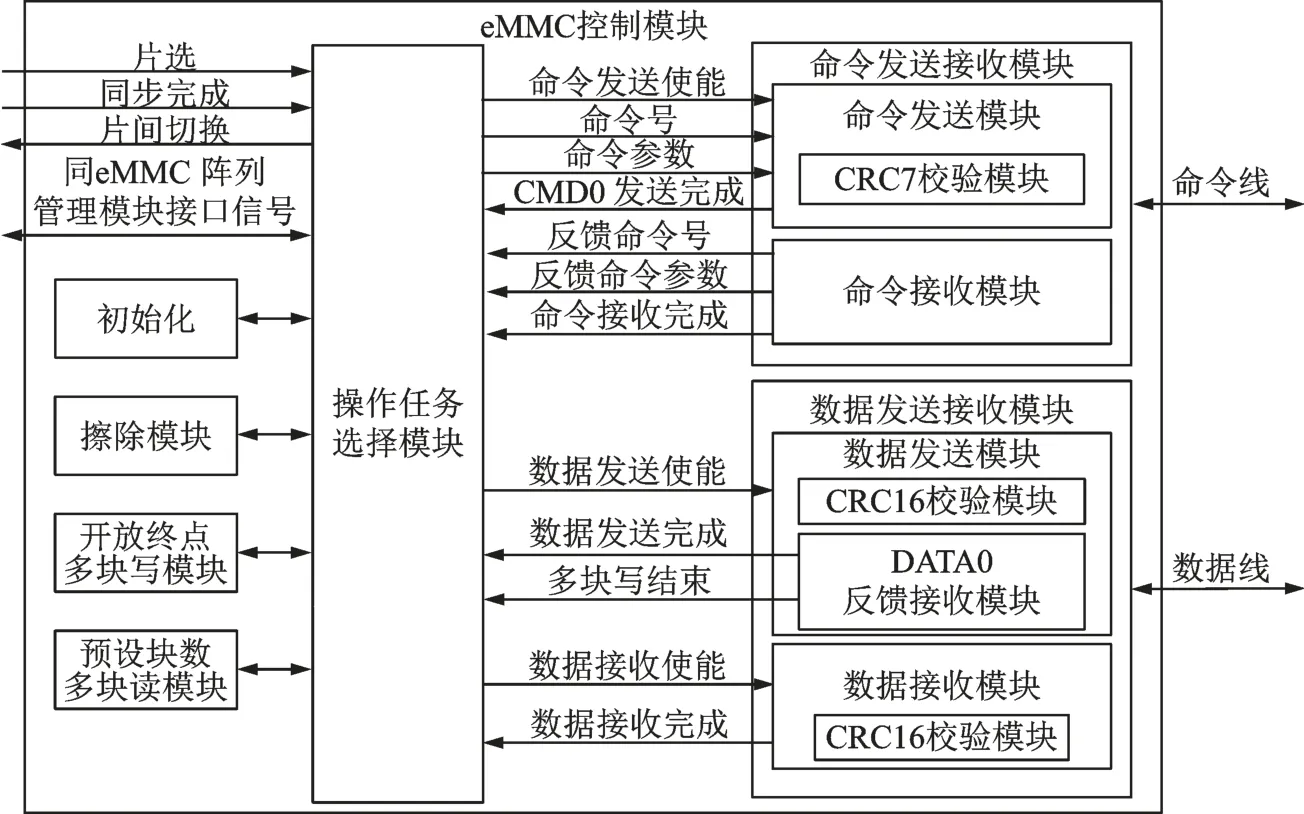

4 eMMC 控制模块

eMMC 控制模块主要实现单片eMMC 的初始化、数据擦除和数据读写等控制操作,内部模块可分为3 部分,内部结构如图7 所示。首先与eMMC 阵列管理模块对接的是操作任务选择模块,操作任务选择模块的主要功能是根据工作参数将对应的命令生成模块与底层收发模块进行对接。命令生成模块能够按照协议要求的命令发送顺序自动产生所需要的命令参数,其中包括初始化模块、擦除模块、单块读写模块、预定块数多块读写模块以及开放终点多块读写模块,这里仅列出其中两种读写模块。命令发送接收模块和数据发送接收模块分别控制eMMC 的命令线和数据线,模块内部附加CRC7 和CRC16校验检查硬件传输异常。片选和同步完成信号主要用于eMMC 阵列片间切换和eMMC 控制模块的状态机重置。接下来主要介绍eMMC 控制器中开放终点多块写和预设块数多块读的工作流程。

图7 eMMC 控制模块结构图Fig.7 Structure diagram of eMMC control module

4.1 开放终点多块写工作流程

开放终点多块写的工作流程如图8 所示。开放终点写模块首先等待操作任务选择模块的写使能信号,然后通过控制命令发送接收模块向eMMC 发送CMD16 和CMD25[13],使得eMMC 处于数据接收状态,之后判断是否有停止信号。如果有停止信号,则向eMMC 发送CMD12,然后通过检测data0 信号线的上升沿来判断eMMC 是否回到transfer 状态。如果没有停止信号,则继续等待片选使能信号。当片选信号有效时,等待其他主控模块数据准备好。当其他主控模块给出数据准备好信号后,开放终点多块写模块开始读取其他主控模块中FIFO 数据,再通过数据发送接收模块发送给eMMC 芯片,在写入过程中使用计数器同步计数,当达到操作长度时向阵列管理模块反馈切换信号,选择其他eMMC 芯片作为操作对象继续写入。

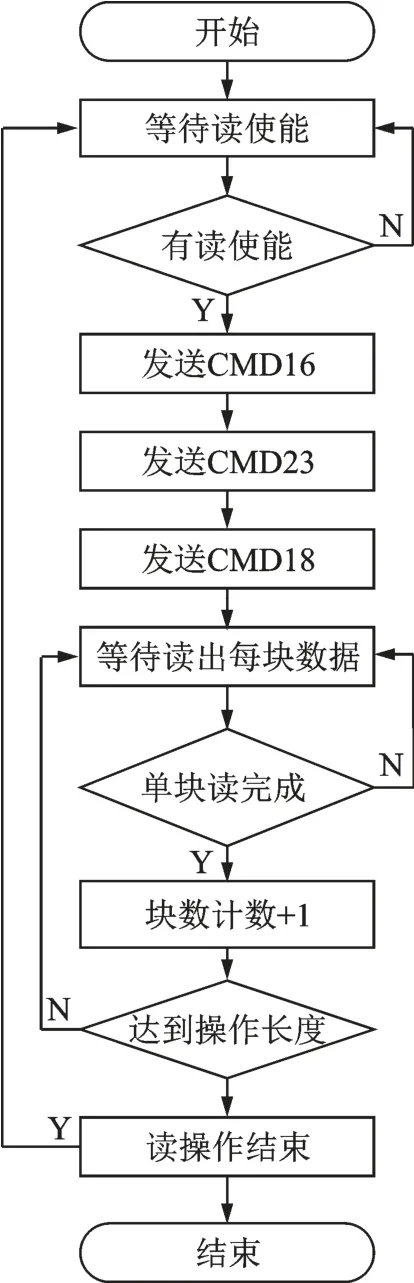

4.2 预定块数多块读工作流程

预设块数多块读的控制流程如图9 所示,预设块数多块读模块首先等待操作任务选择模块的读使能信号,然后通过命令发送接收模块依次向eMMC 发送CMD16、CMD23 以及CMD18[14],使得eMMC处于数据发送状态,然后通过数据发送接收模块接收从eMMC 读出的数据并进行CRC16 校验。如果没有达到操作长度计数器继续累加,当计数器达到操作长度后读操作结束,预设块数多块读模块重新回到等待读使能状态。

图8 eMMC 控制器开放终点多块写流程图Fig.8 Flowchart of eMMC controller open-ending multi-block writing

图9 eMMC 控制器预定块数多块读流程图Fig.9 Flowchart of eMMC controller multi-block reading

5 测试与验证

5.1 测试模块设计

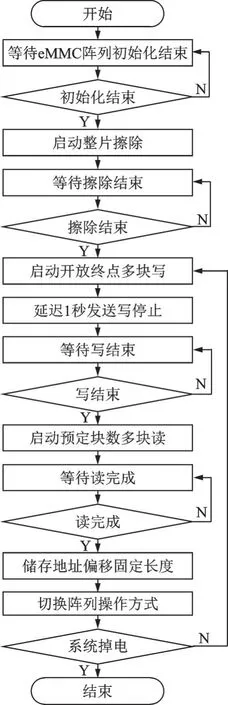

为了测试eMMC 阵列控制器的整体工作流程,本文独立设计了一种循环测试模块,该测试模块作为其他主控模块向eMMC 阵列控制器不断发送配置参数和数据,测试模块的工作流程如图10 所示。

测试模块首先等待eMMC 阵列初始化结束,阵列操作方式默认选择逐片顺序操作,然后发送擦除命令擦除eMMC 阵列的全部内容。擦除结束后发送开放终点多块写命令,延迟1 s 后发送写停止信号,等待写操作结束,同时利用计数模块累计循环次数。为了比较读写数据的一致性,继续发送预定块数多块读命令,然后等待读操作结束,如果数据一致则可说明eMMC 阵列读写功能正常。在下一次循环读写开始前改变操作地址和阵列操作方式,实现在全部储存空间下的读写性能检验。

由于chipscope 抓取的时序图长度有限,为了更好地展示测试结果,本文将操作长度设为3,即每次读写操作的数据量为3 块,每块为两组0~255 的连续递增数,具体数据结果在测试结果图中不再展开。为了实现长时间测试,在触发条件中加入计数模块的计数变量,将抓取时间调整在48 h 后触发,然后在200 MHz 工作频率下测试eMMC 阵列分别在两种阵列操控方式下的工作性能。

5.2 测试结果分析

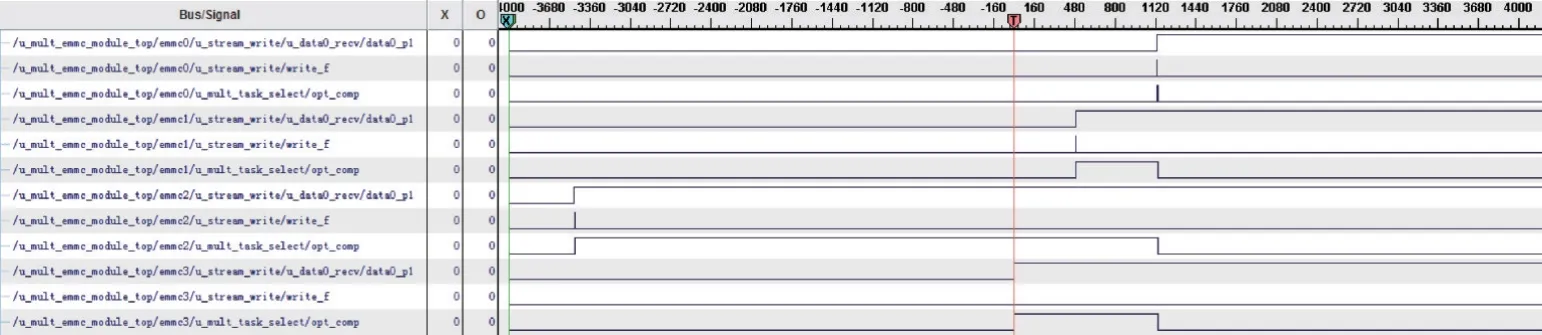

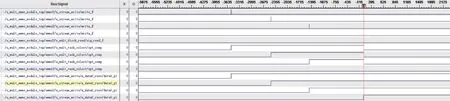

5.2.1 逐片操控方式下的读写功能测试

在数据准备好的条件下,eMMC0 首先进行开放终点多块写,写完3 块数据后,向上层反馈了片间切换信号,之后eMMC1、eMMC2、eMMC3 分别依次进行相同操作,测试结果如图11 所示,当eMMC3 操作结束后,数据准备信号无效,此时eMMC0 处于等待状态循环检查数据准备信号和停止信号。经过1 s 后接收到停止信号,主控向eMMC 阵列发送停止命令,每片eMMC 在结束写过程中,DAT0 线始终保持低电平,DAT0 线在多块写结束后重新拉高,当最后一片eMMC 写结束时向上层反馈操作结束信号,测试结果如图12 所示。逐片操控方式下的读过程同样按照写入顺序将数据依次读出,每片读出数据逐一通过数据传输控制接口写入其他主控模块,测试结果如图13 所示,从测试结果可以看出逐片操控方式下数据读写功能正常,每片eMMC 的数据读写速率可以达到200 MB/s,eMMC 阵列整体的读写速率为200 MB/s。

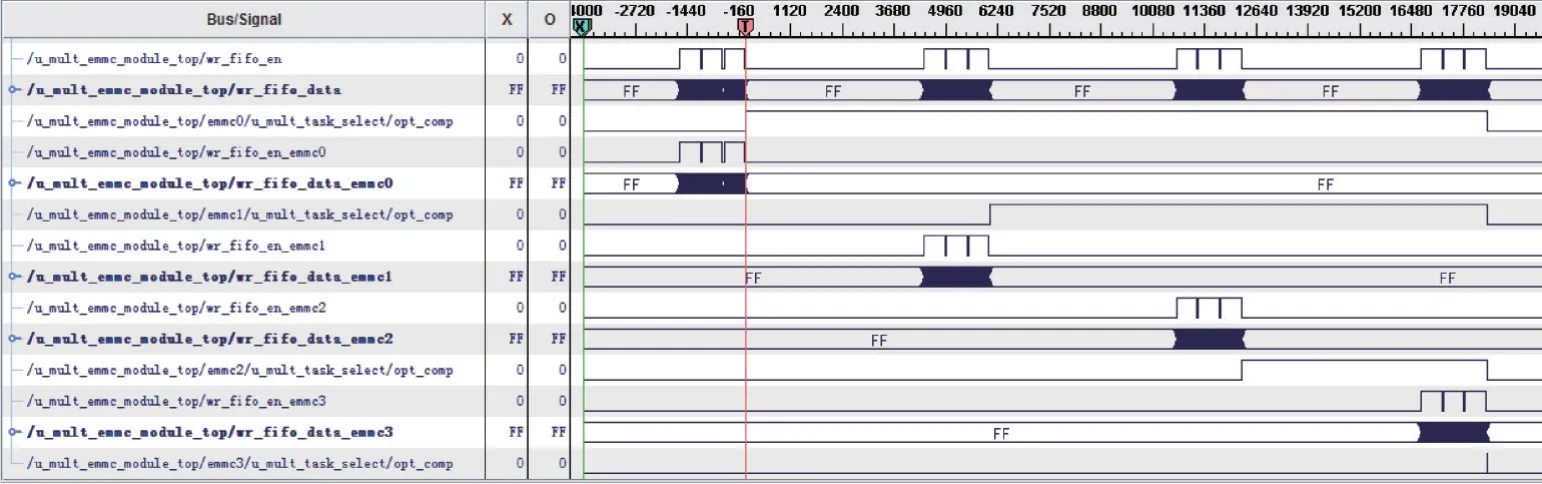

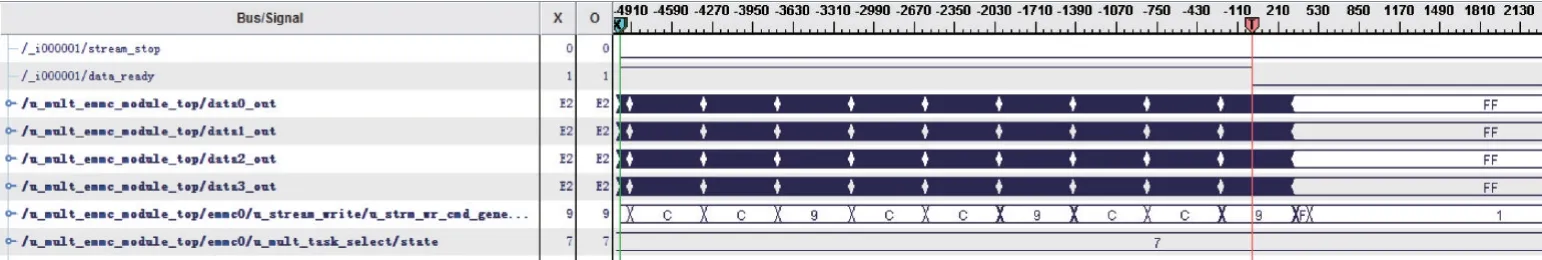

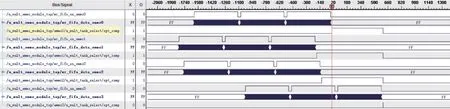

5.2.2 并行操控方式下的读写功能测试

在数据准备好的条件下,eMMC 阵列控制器首先控制四片eMMC进行开放终点多块写,从图14 中可以看出四片eMMC 能够同步写入数据,并且整体数据写入速率可稳定在800 MB/s。在传输最后一块数据的过程中接收到停止信号,之后立即停止数据传输,等待4 片eMMC 结束写操作,测试结果如图15 所示。启动多块读后,每片eMMC 能够读出3 块数据,并且读数据速率稳定在200 MB/s,由于每片eMMC 的响应速度不同,各片eMMC 之间启动读数据的时间会存在延迟,从整体上看数据读速率可达到800 MB/s,测试结果如图16 所示。从测试结果可以看出并行操控方式下数据读写功能正常,每片eMMC 的数据读写速率可以达到200 MB/s,eMMC 阵列整体的读写速率可以达到800 MB/s。

图10 测试模块工作流程图Fig.10 Flow chart of test module working

图11 逐片操控方式下的开放终点多块写时序图Fig.11 Timing diagram of open-ending multi-block writing in chip-by-chip operation mode

图12 逐片操控方式下的开放终点多块写结束时序图Fig.12 Timing diagram of multi-block write-ending in chip-by-chip operation mode

图13 逐片操控方式下的预定块数多块读时序图Fig.13 Timing diagram of multi-block reading with predetermined number of blocks in chip-by-chip operation mode

图14 并行操控方式下的开放终点多块写时序图Fig.14 Timing diagram of open-ending multi-block writing in parallel operation mode

图15 并行操控方式下的开放终点多块写结束时序图Fig.15 Timing diagram of open-ending multi-block write-ending in parallel operation mode

图16 并行操控方式下的预定块数多块读时序图Fig.16 Timing diagram of multi-block reading with predetermined number of blocks in parallel operation mode

6 结束语

文章的创新点主要有3 个方面,首先是设计了一种可兼容开放终点读写和预设块数读写的操作接口,减少了eMMC 阵列控制的逻辑设计复杂度;然后是利用软复位来实现工作频率和阵列操控方式的重新选择,提高了eMMC 阵列的应用灵活度;最后是在控制器内部多处加入了故障信息反馈,有利于用户及时处理存储异常情况。本文提出的eMMC 阵列控制器可以实现多种配置方式,能够满足同一平台的多种存储速率需求。为了测试长时间工作的稳定性,独立设计了一种循环测试模块,测试了多种操控方式之间的切换功能,验证了方案设计的可行性和可靠性,在eMMC 控制器性能验证方面具有一定的参考意义。