适用于微小卫星在轨更新与模式切换的FPGA 配置方案设计*

李林瞳,石云墀,张 凯,陈瑞龙,程庆林

(上海航天电子技术研究所,上海 201109)

0 引言

微小卫星对星载设备的集成化要求很高,一般要求在单一模块完成双机备份、多种功能模式切换以及在轨可重配置等功能。高效稳定的FPGA 远程更新方案正是微小卫星设计的关键一环。设计师往往在硬件空间、实现复杂度以及价格成本等因素的困扰下难以平衡各个方面。本文分析了3 种FPGA在轨重构的设计方案和配置原理,即通过FPGA 直接读写更新、双镜像更新和用户自定义切换更新,比较得出更加适合于微小卫星在轨更新应用的配置方案。

结合项目需求,本文搭建基于Artix-7 与SPI Flash 的硬件平台,通过调用ICAPE2 传输同步字、重加载命令以及加载地址等指令信息,实现了对该配置方案的验证[1]。

1 FPGA 直接读写更新Flash

可以通过FPGA 读写FLASH 实现远程更新的方案,Xilinx 平台需要根据时钟、数据位宽和Flash操作命令等信息实现Flash 读写控制器,通过FPGA直接控制Flash 的读写,充分挖掘FPGA 和Flash 的潜力。

但是,当写入Flash 的操作出现错误或者Flash中部分地址中的数据出现错误时,将导致无法正确写入或者存储的数据出现错误而使FPGA 无法加载成功。

当FPGA 无法加载成功或者工作不正常时,FLASH 的读写操作也无法得到保证。此时,远程更新的方案无法重新读写Flash 来纠正之前的错误。所以,当Flash 直接由FPGA 控制读写且远程更新出现错误时,卫星在轨无法安排现场更新,很可能导致远程更新彻底失效。

2 双镜像更新

可以使用双镜像的方案解决写入Flash 出错的问题。在Flash 中放置两个镜像文件,即M 镜像(Multiboot Image)和G 镜 像(Golden Image)[2]。启动时先加载M 镜像,当M 镜像出现错误时,则启动G 镜像。由于G 镜像从来没有被更新过,出现错误的概率会非常小。加载流程和镜像在Flash 中的相对位置如图1 所示。Xilinx 7 系列FPGA 的双镜像方案是从基地址开始存放G 镜像的,后续存放M 镜像。完成配置后如果配置成功,则运行M 镜像;如果运行失败,则重新加载G 镜像。

图1 双镜像配置模式加载流程

可以看出,双镜像方案的关键是完成两个任务:一是正常情况下加载完成时应该是M 镜像在运行;二是出现错误时需要返回G 镜像。

2.1 加载完成时运行M 镜像

FPGA 上电完成后,会按照设置进行加载操作。主动模式下,FPGA 会自动完成对Flash 中存储的镜像数据的读取,该过程用户无法控制。一般的,FPGA 会从基地址开始读取数据,所以为了完成加载完成时从M 镜像加载,需要引入一条加载命令——内部重加载指令(Internal program_B,IPROG)。具体而言,FPGA 直接从基地址开始加载,先读取G 镜像数据。但是,这里G 镜像的开始部分添加了IPROG 指令和M 镜像的起始地址,所以尽管从基地址加载,但G 镜像只是运行了最前面的几条加载命令,M 镜像只是等待了几条命令后就开始加载,可以认为加载完成时是M 镜像在运行。

2.2 加载出错回退G 镜像

M 镜像加载不成功时,需要退回G 镜像,双镜像方案称这一步骤为Fallback。以下4 种错误会触发Fallback:(1)IDCODE 错误;(2)CRC 校验错误;(3)看门狗溢出错误;(4)BPI 地址越界。IDCODE 错误是指配置文件中的器件型号与当前器件不匹配;CRC 校验指配置数据送入FPGA 后会进行校验,如果数据不一致导致CRC 校验出错;看门狗溢出错误发生在规定时间内无法配置成功的情况;当逐步增长的BPI 地址超过最大值发生溢出时,会触发BPI 地址越界的错误。

当发生Fallback 后,工程会跳回0 地址开始加载,即重新加载G 镜像。值得注意的是,FPGA 内部状态寄存器会记录触发问题等信息。根据在状态寄存器中记录的值,FPGA 会在发生Fallback 后自动忽略IPROG 命令和加载地址等信息,直接加载G镜像后面的部分,从而保证G 镜像被完整加载。表1 记录了当G 镜像内置IPROG 命令,M 镜像由于CRC 错误导致触发Fallback 时状态寄存器的变化。状态1 表示IPROG 被执行,但在M 镜像中检测到CRC 出错;状态0 表示Fallback 被成功地加载。

表1 G 镜像内嵌IPGOG 且M 镜像CRC 出错触发Fallback 时状态寄存器值

双镜像方案的优点在于快速跳转、加载和返回,尤其是在加载初期就进行跳转,适合对配置时间有要求的场合。但是,该方案的原理和设置较为复杂,配置方式固定,无法完成微小卫星远程更新时多种模式下的任意切换。

3 用户自定义切换更新

相对于双镜像方案,用户自定义切换更新可以根据需要在多个镜像中任意跳转,而不限于两个;用户也可以选择合适的时间触发微小卫星的远程在轨更新和模式切换。通过对内部配置访问端口的分析,可以得出用户自定义切换更新的实现方案。

3.1 内部配置访问端口

内部配置访问端口(Internal Configuration Access Port,ICAPE2)可以在FPGA 中以原语的方式被调用。ICAPE2 允许用户在FPGA 阵列层面访问配置功能,配置命令或数据可以从FPGA 阵列的配置逻辑中被读写。ICAPE2的模块结构如图2所示,模块的端口描述见表2。可以通过ICAPE 可以向FPGA 发送IPROG 指令和热启动的起始地址(Warm Boot Start Address,WBSTAR)等信息,进而实现配置切换[3]。

图2 内部配置访问端口结构

表2 端口描述

3.2 用户自定义切换更新的设计实现

通过ICAPE2 传输重加载命令必须在一次成功的配置之后。命令序列为传输同步字,传输热启动起始地址和传输重加载命令。值得注意的是,为了保证ICAPE2 收发正确的指令,实际传送的每一个收发的命令和指令必须遵循SelectMAP 数据顺序。SelectMAP 数据顺序是将每一个指令都按照字节划分,划分后每一个字节的数据都按照比特位翻转,保证配置文件成功加载到FPGA 中[4]。表3 为实现用户自定义远程更新的一次成功加载的比特流序列,列出了配置数据和按字节翻转后的配置数据。

在发送重加载指令之前,需要对ICAPE2 进行预配置。在收到外部控制重加载的触发信号后,第一个时钟周期将ICAPE2 的写信号和片选信号置高电平,在第二个周期再将写信号置低电平,片选信号置高电平,第三个周期将写信号置低电平,片选信号也置低电平。随后,在接下来的8个时钟周期里,将表3 中指令队列中的控制命令通过状态机逐一发出,实现一次重加载。

在基于Artix-7 与SPI Flash 的硬件平台上完成用户自定义切换更新的设计实现,SPI Flash 的型号为Micron 公司的N25Q128A,容量128 MB。触发重加载的信号通过硬件上按钮的方式实现。实际的微小卫星在轨工作时,可以通过内总线的方式访问FPGA,实现对重加载过程的控制。在SPI Flash 中存放两段程序,第一段比特流起始于基地址,第二段比特流从地址00400000 开始,将两段.bit 文件合并生成.mcs 文件并下载到SPI Flash 中。在第一段程序加载成功后,通过按钮触发状态机的运行,向ICAPE2 中写入控制命令,从而成功转入第二段程序的加载;第二段程序加载成功后,再通过一次按钮触发,状态机开始运行,从而能够回到基地址加载第一段程序。实验完成了在不同模式下自由切换的目的,用户可以通过修改WBSTAR 中的内容自由切换加载地址,完成不同模式下的任意切换。图3 为用户自定义切换更新方案的加载流程[5]。

用户自定义切换更新方案需要在一次成功的加载完成后完成切换,该方案的更新手段更加灵活,用户自由度更高,更加适用于微小卫星在轨更新的应用场景。

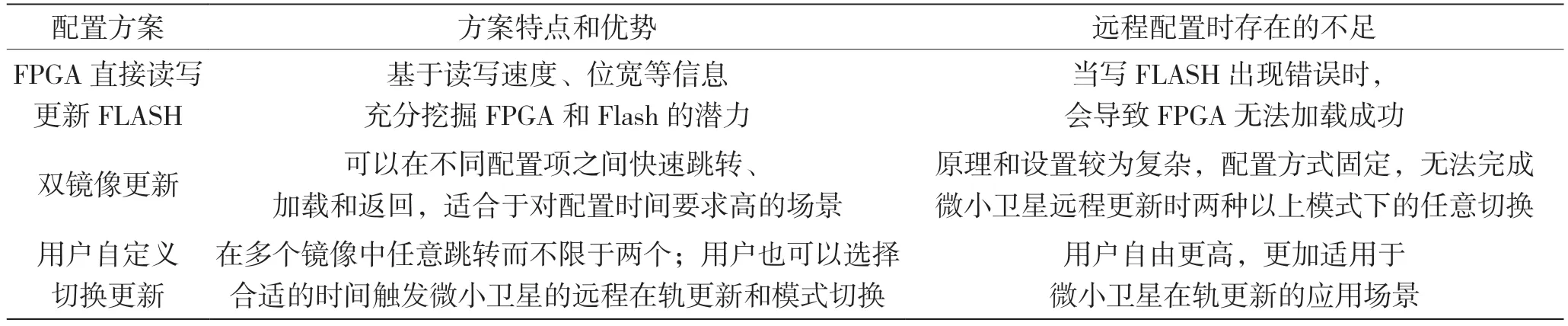

4 3 种FPGA 远程配置方案比较

3 种FPGA 远程配置方案的综合比较如表4 所示。可见,相较于FPGA 直接读写更新FLASH 和双镜像更新方案,用户自定义切换的更新方案更加适合于微小卫星在轨更新的应用场景。

图3 用户自定义切换更新方案的加载流程

表4 3 种FPGA 远程配置方案比较

5 结语

本文通过对FPGA 直接读写更新FLASH、双镜像更新和用户自定义切换更新3 种FPGA 的远程配置方案的论述,阐述了FPGA 直接读写更新FLASH和双镜像更新方案用于微小卫星远程更新场景的不足,并基于Artix-7 与SPI Flash 的硬件平台完成用户自定义切换更新的设计实现。实验结果表明,用户自定义切换的更新方案更加适用于微小卫星在轨更新的应用场景。