基于FPGA的多通道视频采集系统设计实现

隋旭阳,李妍妍,向学辅,田瑞娟

(中国兵器装备集团自动化研究所, 四川 绵阳 621000)

随着微电子技术的发展,基于多相机的应用系统,如基于多摄像机的数据采集分析系统、多传感器图像融合系统和基于分布式摄像机的大范围视频监控系统等日渐丰富。这些系统的共同点是都需要同时处理多通道同步或异步视频数据流,实现高带宽、大容量图像数据高速、实时处理。传统的图像采集系统往往只有一个数据通道,每一次的数据采集只能面向单一传感器,并且数据采集速率有限,实时性较差[1];基于DSP的多通道视频处理系统的资源配置不够灵活,不能很好地实现视频格式转换、颜色编码转换等功能[2];由此,多通道视频处理系统需要与之相匹配的稳定、可靠的数据采集和缓存系统。

本文研究了基于FPGA的多通道视频数据采集系统,设计了一套完整的多通道视频数据采集硬件平台,该平台可以获取多通道视频流,并对视频数据进行缓存,通过数据优先级仲裁模块进行多通道视频流调度,并引入DDR3 SDRAM作为高带宽、大容量图像数据高速缓存设备,实现了多通道同步或异步视频数据流的帧缓存,最后利用显示模块将采集到的视频流进行分屏或拼接显示。多通道视频数据采集系统模块化设计,可加入数据传输、图像预处理算法等模块,适合绝大多数的视频处理环境,能够为后续的多通道图像融合和图像实时边缘处理等算法提供稳定的数据采集环境。

1 系统方案设计

1.1 系统硬件平台方案

由于FPGA具有很强的并行处理能力和时序控制能力,因此被广泛的应用于高速并行数据处理领域[2-4]。FPGA可方便扩展、可随时编程的特点,更适合用于开发周期短的工程应用[5]。因此,选用FPGA作为多通道视频数据采集缓存设计方案的主控芯片,实现多路相机图像数据流输入、读写DDR3芯片、显示等功能。

DDR3 SDRAM作为高带宽、大容量图像数据高速缓存设备是当前常用的设备存储解决方案[6]。因此,本文采用Xilinx公司7系列FPGA的DDR3存储控制器(Memory Interface Generator)IP核辅助完成数据缓存设计[7]。为提升用户使用的方便性,本文采用类FIFO的封装方式优化了与MIG IP核信号互联的用户接口[8];采用基于DDR3 SDRAM存储地址的读写控制方法设计数据读写控制模块:将多通道的数据分别写入用户指定的DDR3的地址空间位置中,并通过读写切换操作读出使用,更加灵活地处理数据在DDR3中的缓存[9]。

1.2 系统逻辑方案设计

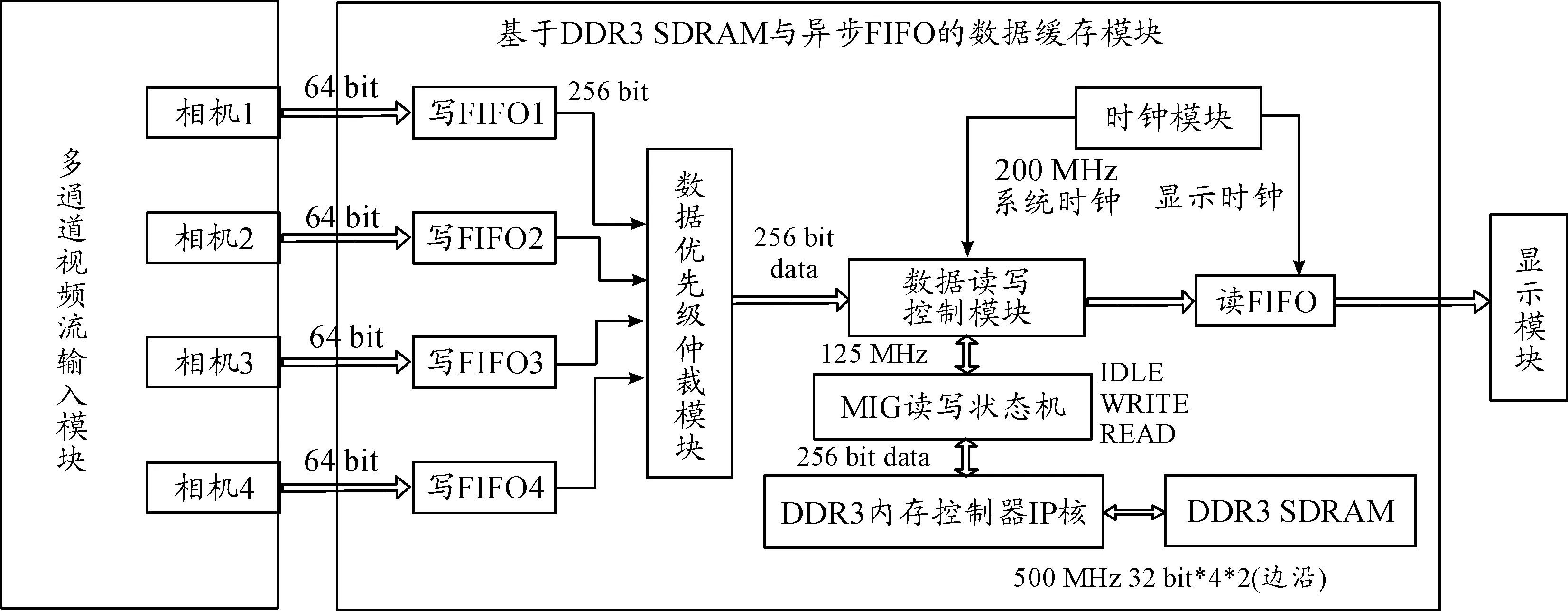

在系统进行数据采集时,多通道视频流输入模块将同步或异步视频数据流缓存在相应的异步FIFO中,数据优先级仲裁模块比较每一路视频源的有效数据信息是否超过阈值,判断各通道图像数据是否触发优先级信号,从而选择一路视频源,从相应的异步FIFO中读取数据,传输给FPGA数据读写控制模块,经过DDR3存储控制器完成数据在DDR3 SDRAM相应地址区域的缓存,并根据读命令和读地址,读出所需的视频源数据,以便后端采用相应的图像处理算法对多通道视频数据进行深入分析。系统逻辑方案设计如图1所示。

图1 系统逻辑方案设计框图

2 多通道视频采集系统设计

2.1 系统工作流程

系统工作流程如图2所示。系统工作流程包括:首先进行主程序运行,然后完成系统的上电复位操作,再利用系统判断DDR3控制器的校准信号是否完成,若未完成,继续等待;若完成,FPGA控制各路视频源的有效数据分别实时缓存在FPGA异步FIFO中。再利用数据优先级仲裁模块根据优先级信号、阈值信息控制FPGA从相应的异步FIFO中读取数据,然后通过DDR3数据读写控制模块接收视频源信息,并产生DDR3读写控制命令,根据读写操作命令、视频源通道编号和用户设定的读写操作空间计算给出DDR3读写操作相应的地址,最后,FPGA根据设置的显示参数从DDR3 SDRAM存储器相应的地址空间中读写所需的视频源数据,并根据用户需求进行分屏或拼接显示。

2.2 DDR3读写状态切换

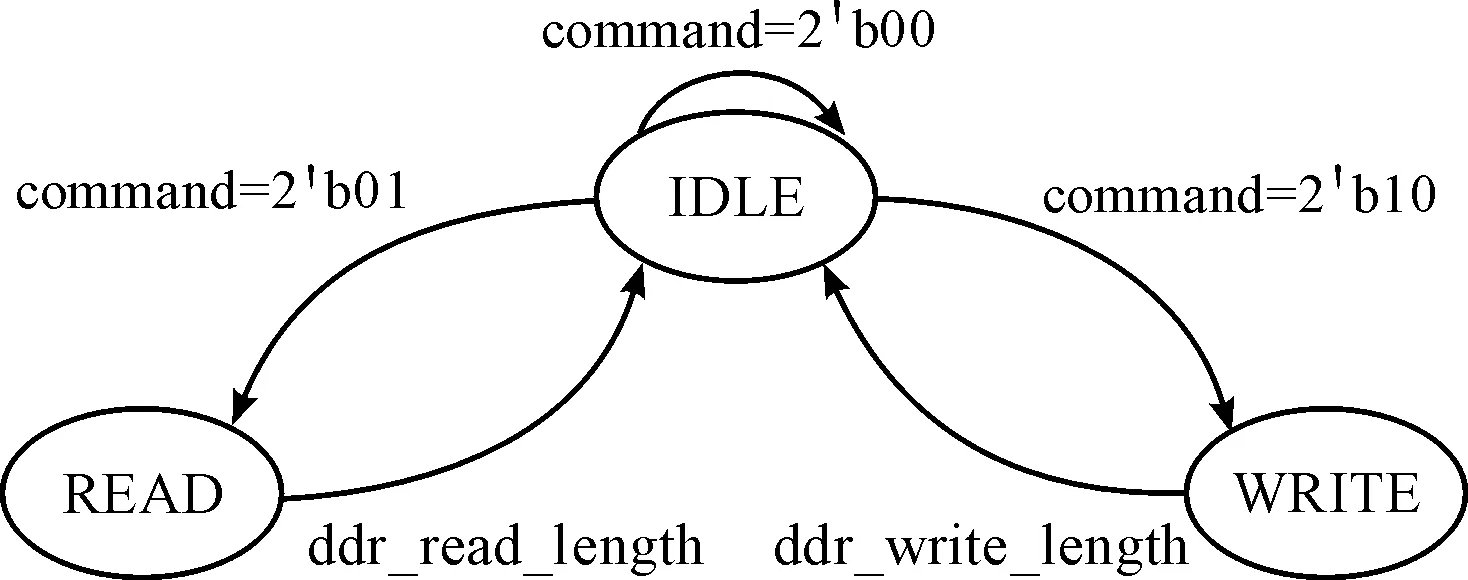

设计的DDR3读写状态机共有3种状态(见图3),每一次的写操作都可以将相应通道的ddr_write_length数量的视频数据存储到用户指定的存储地址位置中,读操作将相应地址空间的数据读出使用,充分发挥出DDR3存储的灵活性[9]。

图2 系统工作流程框图

图3 DDR3读写状态机

2.3 系统跨时钟域处理

本系统涉及相机输入时钟与DDR3数据输入时钟,DDR3数据输出时钟与显示模块时钟等跨时钟域操作。为降低系统亚稳态[10]出现概率,系统在跨时钟域处采用异步FIFO,一方面解决数据位宽变换问题,另一方面,异步FIFO的存储过程可描述为:把A时钟域的数据存储到RAM中,稳定后再由B时钟域读取RAM中的数据,从而实现从A、B时钟域的跨时钟域数据、信号的安全传输。

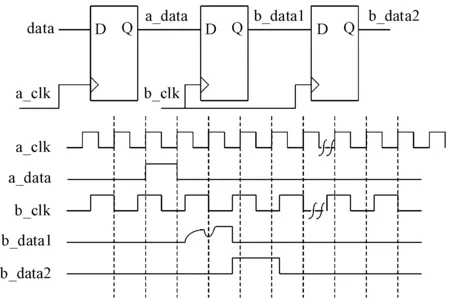

系统中涉及复位、DDR3校准等控制信号也需要进行跨时钟域的信号传输,采用两级触发器同步处理控制信号(见图4),可以防止亚稳态传播[10]。

图4 两级触发器同步处理控制信号示意图

3 系统测试及系统效率分析

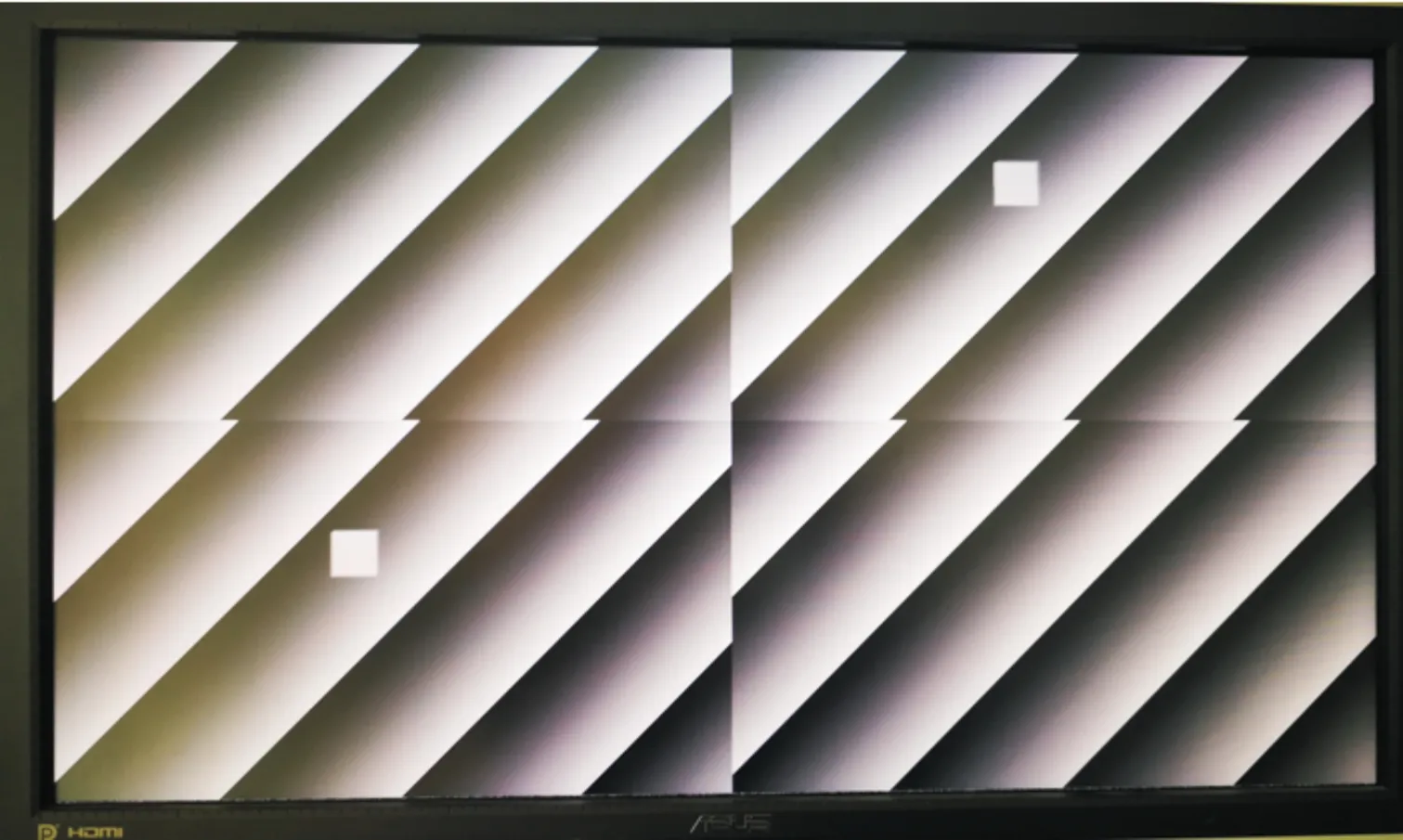

在Xilinx Kintex-7 系列FPGA上进行多通道视频数据采集与显示时选用的DDR3 SDRAM型号为MT41K256M16XX-125。高带宽视频图像来源于模拟源生成器生成的4路异步视频数据流,其帧频为60FPS,而分辨率为1 920×1 080P。视频图像经DDR3缓存后进行截取拼接显示,得到稳定的 1 080P VGA显示,如图5所示。由于模块通用化设计,可以通过顶层模块的参数配置实现常见的多种分辨率多路同步或异步视频采集缓存。

图5 4通道异步视频数据流采集拼接显示图

DDR3 SDRAM在IP设计时采用500 MHz的系统时钟,其数据位宽为32 bit,用户时间周期为8 ns,理论带宽为500×2÷8×32 bit=4 000 MB/s。采用VIVADO软件的ILA抓取一段数据进行带宽测试,如图6所示。

从图6可以发现,在数据缓存过程中,由于工程的可扩展性设计,有很大一段时间是在IDLE状态等待视频源数据,造成了带宽的未利用,如图7所示。

由于DDR3 SDRAM属于动态随机存储器的一种,使用电容存储,必须每隔一段时间对存储单元加载比较电压,对相应的数据重写,如若不然,存储的数据就会丢失。预充电命令、激活命令、动态刷新操作会影响DDR3 SDRAM的读写效率[3];DDR3控制器在设计时,为了保证更低的出错率,采取了读写状态切换时IDLE状态等待措施,这些措施也会降低效率;在多通道视频数据采集应用方面,需要控制每一路视频缓存在相应的地址空间范围,每一帧图像完成精确的存储地址定位,考虑到FPGA内部资源的合理利用,每一次缓存在异步FIFO中的数据长度不宜过多,DDR3需要完成频繁的读写地址切换,效率有所降低。同一地址空间读写切换测试表明,对DDR3连续进行N次写操作,再进行N次读操作测试效率如下:N为1时,效率为10.3%,N为64时,效率为74.8%,N为240时,效率为80.2%。频繁的读写地址切换,使得多通道视频数据采集在连续240长度读/写操作时效率必然低于80.2%,但随着用户设计的单次读写数据量增大,读写效率将有所提升。相比于多通道A/D信息采集方面的应用中连续读写能够达到理论带宽80%以上的效率[3],多通道视频数据采集受频繁的同Bank行切换、Bank间切换影响,效率有所降低。

图6 4通道异步视频采集带宽计算界面

图7 4通道异步视频写入带宽计算界面

4 结论

通过系统硬件平台方案选择、系统逻辑方案设计、系统工作流程实现、系统跨时钟域优化处理等角度阐述了多通道视频采集系统的设计与实现,并经过板级验证,实现了4通道异步视频数据流采集、缓存与视频截取、拼接显示。在考虑控制操作延时传递、存储器动态刷新等情况下,数据读写带宽可达到近3 000 MB/s,效率在理论带宽的70%左右。模块化、参数化的工程设计具有较强的可移植性。