基于FPGA内存数据保护技术的设计与实现

李仁刚,任智新 ,王江为,阚宏伟,张 闯,公维锋

1.高效能服务器和存储技术国家重点实验室,济南 250013

2.浪潮电子信息产业股份有限公司,济南 250013

1 引言

随着“云计算”在学术及工业界的成功,数以万计的服务器分布在国内外各云平台厂家的数据中心中,而且数量和规模还在不断的增长[1-2]。高可靠性是云计算平台的一个重要指标,很多重要的应用,比如金融软件、医疗服务、电子商务等部署在这些服务器集群中。这类应用一旦发生故障,会造成不同程度的经济损失甚至影响生命安全[3]。

内存故障虽然已不如计算机发展早期时那样普遍,但是在数据中心里,即便是小概率的故障,一旦发生,可能就是灾难性的、无可挽回的,所以在内存发生故障时,高效保护内存数据是一项不容忽视的工作。虽然业界已经提出了各种各样内存数据保护技术,但在普遍性、通用性、开发难度上很难做到兼容,故本文提出一种基于FPGA 的实现方法,不仅可以恢复大块故障数据,加入的设备对计算机系统透明无需在软硬件上做其他处理,并且支持在线替换。

2 内存故障及内存数据保护分析

Schroeder 等人曾经做了一次为期两年的内存故障追踪,样本是谷歌的数据中心Warehouse-Scale Computers(WSC)内数十万台服务器[4],实验发现,每年大约有三分之一的服务器遭遇过内存错误,平均22 000次可纠正错误和1 次不可纠正错误。对于这三分之一的服务器,每2.5小时就要纠正1次内存错误,而在一个仅有奇偶校验位错误保护的WSC 中,每发生一个内存奇偶校验位错误,服务器都必须重新启动,这一特性会将价值1.5亿美元的设施性能降低6%[5]。德国的一项研究数据表明,一些宇宙射线等会对内存数据造成软件破坏[6],除此之外,还可能发生内存芯片内部短路或其他原因导致内存的物理性损坏,总之,内存故障发生率远超过大多数人的常规认知。

为了降低内存故障引起的服务器重启或者宕机发生率,业界提出了在软件和硬件上更好保护数据的方法[7]。硬件上常见的是加入ECC(Error Correcting Code,错误检查和纠正)功能,可做到单bit 纠错多bit 上报,但是当大块内存数据出错时,无论是高级ECC[8]还是Chipkill[9](一种ECC 内存保护技术)技术,都无能为力。而内存热备份技术[10]是对工作内存进行完全的备份,当出现大块故障时,可使用备份内存的数据,保证系统正常工作。若使用计算机系统的内存控制器实现该功能,无疑会增加软件的工作量、系统研制难度及周期,若使用专用芯片代替软件处理方式,虽然在处理速度上更胜一筹,但是不具备良好的通用性,不同的服务器不同的内存协议,都需要开发新的芯片,造成成本和研发周期的增加。

FPGA 是目前最常用来处理高速数据传输的器件,具有良好的并行计算能力,支持电路重构和流水,并且其比ASIC(专用集成电路)有更好的通用性。本文提出基于FPGA实现内存数据保护的方法,不依赖服务器类型以及软件的操作系统,可以从硬件上提高内存可靠性,而且该方法支持热替换,内存发生故障后,热备内存直接代替故障内存继续工作,而故障内存在不关机的情况下可直接被拔掉,更换成新内存。另外,该方法对内存型号亦不做限制,升级内存时,可升级FPGA 的烧写文件,而不需要重新设计硬件,大大提高了开发效率。

3 实现原理

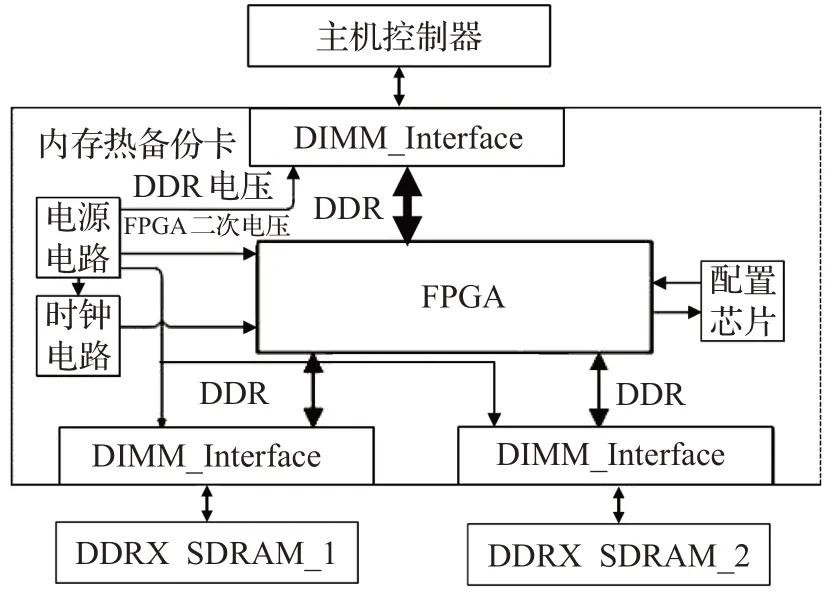

以FPGA做处理器的内存热备份技术,其工作原理是:具有内存热备份功能的板卡与主控制器接口采用标准的DIMM(Dual-Inline-Memory-Modules,双列直插式存储模块)接口(1路),服务器像访问标准内存一样访问内存热备份卡,而热备卡带两路内存条,数据备份和故障检测操作在FPGA中实现。利用这种方式,任意一个计算机都可以通过加入热备卡的方式实现内存热备份,而计算机硬件及软件不需要做改变。

系统实现框图如图1所示,控制指令和写数据从服务器端下发,FPGA将写数据加入校验码后同时写到两个DDR内存中;主机读取DDR数据时,FPGA同时读取两个内存的数据,进行校验,正常情况下会选择主内存数据反馈给服务器,当主内存出现故障时,FPGA 会自动将热备内存中的数据反馈给服务器,不会有数据延迟、断层等现象发生。

图1 系统实现框图

3.1 FPGA实现框图

内存热备份卡对服务器来说是一个标准内存,由FPGA 控制的备份内存对主机不可见。内存的上电初始化时序控制、预充电、刷新、读写等命令都由主机控制。FPGA 实现内存Physical(PHY,端口物理层)接口、命令解析、冗余控制以及解码和通路选择功能。逻辑实现功能如图2所示。

图2 FPGA实现的逻辑功能图

3.2 PHY接口实现

为了满足CPU操作DDR的读写时序[11],FPGA须保证在协议规定的时间内完成所有的操作。本文在设计之初对Altera和Xilinx两大FPGA厂商的相关IP进行对比分析[12],主要是对内部集成的DDR 控制器以及高速接口IP[13]的延时做了对比验证,结果如表1所示(单位是系统主频时钟周期个数)。

表1 IP延时值

经过仿真验证,使用FPGA内集成的DDR_Controller(MIG)或者其他接口IP,都无法满足CPU对内存读延时的要求。故本文采用FPGA 底层原语[14],用搭积木的方式实现PHY接口,实现双倍速率数据的采集。

PHY 接口根据所连接的对象不同而分成两种:(1)与服务器主板DIMM接口互联的作为“内存接口”的PHY_Dev;(2)与两个内存 DIMM 接口互联作为“控制器接口”的PHY_Host接口,两种接口因功能不同而采用不同的实现方式。

(1)PHY_Dev接口实现

根据DIMM 接口的数据频率和FPGA 工作频率之比,可选择I/ODDR 或者输入输出串并转换器(I/Oserdes)原语做数据串/并、并/串转换,文本为了达到最优的性能,采用了写侧通路频率比2∶1、读侧通路频率比1∶1的方式实现,具体如图3所示。

根据数据类型的不同,每种接口在FPGA逻辑内部又分为命令(CMD)通路和数据/数据选通(DQ/DQS)通路。控制器发起的命令数据CMD,在FPGA 内属于单向写通道,进入FPGA 后先经过输入缓存(IBUF);接着经过输入延迟模块(IDELAY)进入ISERDES,完成双倍速率及上下沿数据的采集(一个FPGA 周期采集4 Byte数据),最后进入逻辑命令解析模块;对于DQ 数据,是双向的,从控制器下发到逻辑时是写通路,同样使用ISERDES原语,完成双倍速率及DDR双沿数据的转换;而读通路即数据输出给控制器,此时逻辑工作频率与接口频率一致,使用ODDR 完成双沿数据的转换即可;对于DQS数据选通信号,虽然从属性上也是双向的,但从控制器下发到FPGA 逻辑后,数据并没有继续传递,当做单向数据处理;输出时同DQ 一样,使用了ODDR 原语,在与PAD 接口处使用了IOBUFDS 原语以产生差分信号。使用此方法实现的PHY 接口,延时仅需三个控制器接口频率周期,大大降低使用FPGA实现内存控制时带来的固有延时,是本文的关键之所在。

(2)PHY_Host接口实现

FPGA与内存设备端PHY接口是Dev侧的逆过程,但实现上要更复杂,因为要考虑DDR的特性,在进入正常数据操作之前先由FPGA 控制进行读写均衡初始化训练操作,PHY组成结构如图4所示。

其中,DQS的状态与Dev侧不同,是双向的,是由于在写通路时,由FPGA 产生与数据DQ 同步的数据选通信号,写入到内存中;而读通路时,为了保证DQ与DQS的同步,同时将二者经过内部逻辑后反馈给控制器,所以DQS双向。

3.3 热备份功能实现

本文仅实现内存热备份的功能,不做内存控制,故FPGA解析控制器发送的命令后,生成内部需要的控制信号,控制信号透传即可。而数据的处理是将写数据加入校验码之后同时写到两个内存中,两个内存的数据完全一致,互为备份。

当主机发起读操作时,FPGA 同时从两个内存读取数据,对两路数据进行解码以及故障判断,若两路均正确则选择主内存数据反馈给主机;若主内存故障,FPGA自动将备份内存数据反馈给主机,完成无缝的数据对接,很好地保证了内存数据的正确性和完整性。同时,FPGA 会发出故障报警,提醒更换故障内存,在不需要关闭服务器的情况下,可替换掉故障内存。

图3 PHY_Dev侧接口结构图

图4 PHY_Host接口结构图

但是由于两个内存保存的内容完全一致、互为备份,所以实际容量只有一半,带来功耗及成本的成倍增加,这也是为了满足高端容错需求,避免更新设备时宕机带来的损失,实现在线更换内存,同时也是满足了研发的原型机中主板控制器的读延时要求。另外,由于FPGA 的可重配性,当不使用热备份功能时,可以修改FPGA的逻辑功能,只控制一路容量*2的内存。

4 FPGA平台实现

4.1 功能仿真

本文使用DDR3内存作为测试验证对象,通过仿真对逻辑功能进行验证。将DDR3 内存颗粒模型与自有逻辑进行集成后,联合仿真。分别对DDR进行了刷新、预充电、激活、写-读、写-写、读-读等操作验证,功能均正确,且满足读延时时序要求,如图5 为一次读操作仿真结果,读数据与写入的数据一致。

4.2 FPGA平台验证

在以Xilinx Virtex-6芯片为主控的内存热备份卡硬件平台上进行了验证,硬件平台在设计之初要充分考虑电源及DDR 信号的完整性[15],以满足高速数据传输的特性。在验证初期,FPGA作为控制器发起对两个内存条的操作,除了基本的刷新、激活、预充电等操作外,还进行了读写操作验证。通过在如图6 ChipScope 中观测的验证结果可以看出,FPGA 可以正读写内存,PHY_Host接口的逻辑及硬件电路功能验证正确。

在与主机控制器对接测试之前,采用“自测”方式对内存热备份卡作为“内存”的功能进行测试,即采用一块功能完全一致的内存热备份卡充当“主机”,将被测板卡插入到“主机”热备卡的DIMM插槽中,“主机”热备卡的FPGA 发起控制DDR3 的一系列操作,验证“内存”响应是否正确,同样使用ChipScope 观测,结果与图6 一致,两块内存热备份卡自测的验证平台如图7所示,验证了PHY_Dev接口逻辑及硬件电路功能的正确性。

最后将内存热备份卡插入浪潮高端服务器原型机的主板上,验证与主机控制器进行数据交互功能的正确性。目前,插入内存热备份卡的高端服务器已经成功加载完BIOS,进入操作系统运行应用程序。向主内存注入故障,系统并没有因此宕机,可继续工作,从而验证了该方法在工程实践中的可用性。

图5 读操作仿真结果

图6 内存热备份卡Host侧接口功能测试结果

图7 两板自测连接图

5 结论

本文首次提出了使用FPGA 实现内存热备份的方法,特别地,对于DDR数据采集,使用底层IO原语方式实现PHY接口,有效降低了FPGA内高速接口数据处理的延时,解决了采用FPGA 实现内存热备份存在的瓶颈;同时基于IODELAY 单元实现自动调整时钟与数据Skew 的方法,解决了写均衡/读校准实现难的问题。利用本方法设计的内存热备份卡通过了与高端服务器天梭K1、TS580等机型适配的测试。该项技术在高可靠应用场景中,比如大规模部署服务器的云计算数据中心,可有效保护内存数据,减少由内存故障引起的宕机,提高服务器的可靠性和稳定性,进而保证特殊行业的高需求;而且可应用在服务器BIOS 不做任何改动,直接实现内存条备份的场景中,具有一定的易操作性及可扩展性。