基于W5300的高速数据传输系统设计与实现

杜志美,文 丰,张凯华

(中北大学 仪器与电子学院电子测试技术国家重点实验室,太原 030051)

如今信息技术发展突飞猛进,通信方式向着数据需求量大、实时性高、易于组网等方向发展[1]。集成有TCP/IP协议的以太网芯片W5300以其成本低、数据传输距离远、易于移植且简单快捷的实现高性能数据通信等优势得到了广泛应用[2]。开发者只需要对W5300应用层进行操作,就可以实现不同网络平台间的数据交互。传统的以太网系统存在数据传输不稳定,成本较高等缺点,且在实际应用中,其传输速率很难突破50Mbps[3-4]。

本研究所提出的系统设计采用“FPGA+W5300”组合模式,不仅实现了数据快速、稳定传输,而且极大地降低了开发难度、提高了数据传输的实时性。

1 系统硬件结构与设计

本系统需要设计一个客户端和一个服务器,并在两个相对独立的系统之间建立连接完成数据传输,传输速度要求达到80 Mbps,并且数据稳定可靠。

相比于DSP等控制类芯片,FPGA特有的并行处理能力、高速接口设计、丰富的I/O接口资源等优势,使其在高速数据处理和逻辑控制等方面具有很高的实时性,采用FPGA作为主控芯片,可以使不同网络系统中数据更高速传输。为满足数据传输速度要求,系统采用“FPGA+W5300”组合模式。系统硬件结构如图1所示。

图1 以太网系统硬件结构框图

FPGA可以根据W5300地址总线对寄存器寻址,按照W5300寄存器读写时序,通过数据总线配置和读取相应寄存器的值。本系统采用16位数据总线模式,所以BIT16EN接高电平,数据总线低8位和高8位都需要与FPGA I/O口连接,接收的数据通过FPGA存入Flash。W5300差分输入和输出信号对与外部接口之间增加对称变压器,保证芯片与外界的隔离与数据传输过程中系统的可靠性。

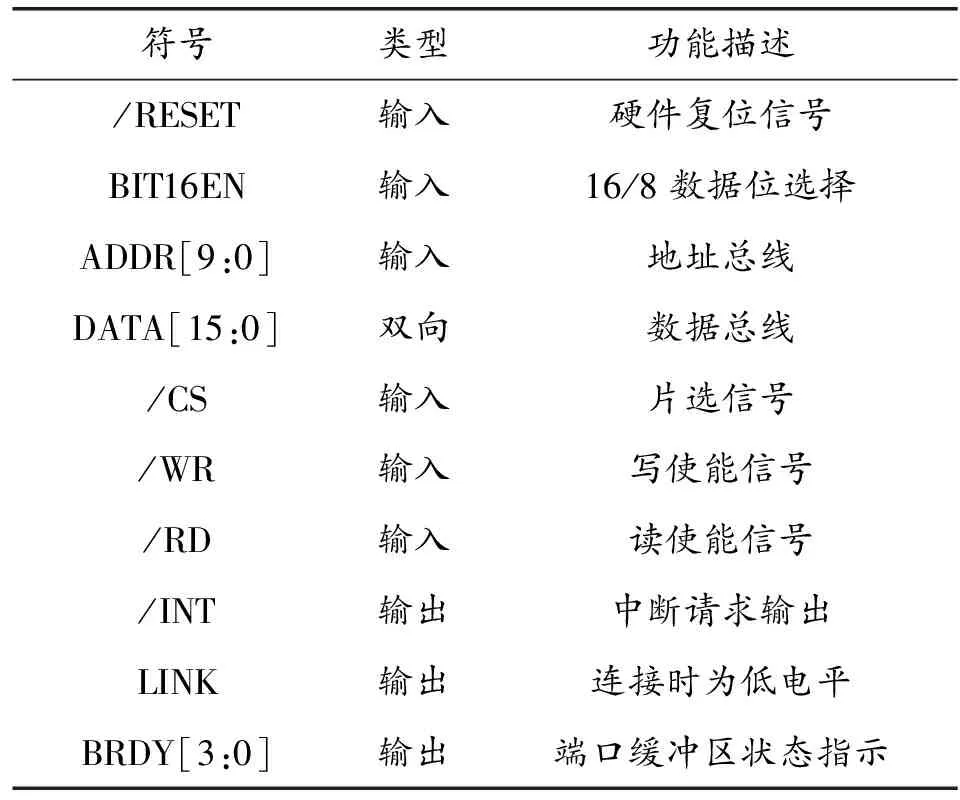

W5300硬件接口类型与功能描述如表1所示。W5300拥有8个独立并行端口,内部集成10BasseT/100BasseT以太网物理层[5],支持直接和间接地址模式。FPGA通过直接访问每个端口的FIFO寄存器,控制端口TX/RX存储器数据读取和写入,从而避免了以往采用FPGA直接处理TCP/IP协议时的负荷,极大简化了程序的编写,使系统对数据的传输和处理能力得到极大改善。

表1 W5300接口类型和功能表

2 W5300软件设计

本系统通过FPGA直接操作W5300内部寄存器。FPGA代码在ISE14.7编译环境下采用硬件描述语言VHDL编写。并根据W5300复位时序、寄存器读和写时序完成FPGA对W5300的控制。软件设计流程分为W5300初始化、端口连接、数据发送和接收3个模块。

2.1 W5300初始化

W5300初始化包括外部接口配置、网络参数和超时设置和端口TX/RX存储器分配[6]。

W5300采用/RESET硬件复位,复位信号在保持低电平大于2 μs后保持高电平时间大于10 ms,执行复位。其内部锁相环将外部25 MHz时钟源倍频后产生150 MHz工作时钟,在复位有效后锁相环锁定时钟频率[7]。

2.1.1外部接口设置

W5300接口设置包括模式寄存器配置和中断配置。

采用直接地址模式(IND=0),可将模式寄存器、通用寄存器和端口寄存器映射到内部存储空间,控制器通过访问对应映射地址来直接访问相关寄存器[8],间接地址模式则相反。FPGA在访问W5300内部寄存器时,寄存器地址从系统基地址开始以2字节递增方式连续映射在内部存储器空间。寄存器地址采用大端模式,即寄存器地址的低字节存储在实际物理地址的高字节。W5300寄存器实际物理地址为“存储器空间基地址+寄存器偏移量”,其中W5300寄存器的物理基地址为0x08000。

与W5300中断相关的寄存器包括中断寄存器(IR)和中断屏蔽寄存器。中断寄存器数据位表示当前中断类型,产生中断时相应数据位置1,如果中断屏蔽寄存器(IMR)相应位也为1,则中断请求输出引脚/INT置0,向FPGA发出中断请求,控制器通过查询中断寄存器数据位判断中断类型并处理中断。

2.1.2网络参数和超时设置

为实现数据在多个网络系统之间传输而不会造成数据传输混乱,需要对W5300进行网络参数配置,包括硬件地址寄存器、网关IP 地址寄存器、子网掩码寄存器和本机IP 地址寄存器。本系统各参数如表2所示。

表2 网络系统参数配置

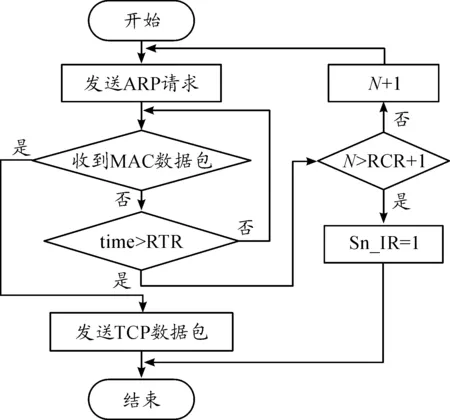

TCP是一种可靠数据传输控制协议。TCP协议在数据通信中经过三次握手验证,保证数据传输的准确性。为避免验证过程中长时间等待,需要进行超时设置,超时设置相关寄存器包括重复发送超时寄存器(RTR)和重复发送计数寄存器(RCR)。W5300超时分为ARP发送超时和TCP发送超时两种。以客户端向服务器发送ARP请求为例,流程如图2所示。

图2 ARP请求流程图

同样客户端向服务器发送TCP数据包后,等待服务器回应ACK响应,若客户端在RTR设置的时间后连续发送RCR+1次还未收到ACK响应,W5300端口状态寄存器(Sn_SSR)将变为SOCKET_CLOSED,并且数据发送端口中断寄存器(Sn_IR)相应位置1,发出中断请求。

2.1.3端口TX/RX存储器分配

W5300扩展了128K通信数据存储器,由16个8K字节存储单元组成[9-10]。这些存储单元可以由存储器单元类型配置寄存器以8K的倍数配置为发送和接收单元,再由存储器大小配置寄存器分配给每个端口TX存储器和RX存储器。

2.2 W5300端口连接

W5300初始化完成后,需要依据设计要求对端口进行配置并连接。W5300具有8个独立端口,可同时进行数据通信。以客户端SOCKET1为例,端口配置和连接流程如图3所示。

W5300有4个缓冲区监视外接引脚BRDY[3:0],用于实时监测SOCKETn数据收发状态。本系统配置了BRDY0和BRDY1分别对SOCKET1 TX/RX存储器监测。在TCP客户端模式下,客户端必须在执行连接命令之前配置目标地址。而服务器则在端口建立连接后,S1_DIPR和S1_PORTR自动设置为TCP客户端IP地址和端口号。端口模式寄存器S1_MR决定了端口通信方式,S1_MR功能描述如表3所示。

在TCP模式下,收到的数据包字节数为偶数时队列对齐数据位“ALIGN=1”,此时删除数据包中的PACKET-INFO,可以极大提高数据读取速度。为了使W5300只接收指定网络数据包,需要将MF位置1。而ND/IGMPv置1时,端口在收到对端发送的数据包后立刻发送ACK数据包响应,可以提高TCP通信性能。P0~P3即配置端口通信协议(TCP、UDP、IPRAW等)或PPPoE SOCKET与PPPoE服务器之间的操作,开发者可根据项目需求自行选择。

图3 端口连接流程图

表3 S1_MR功能表

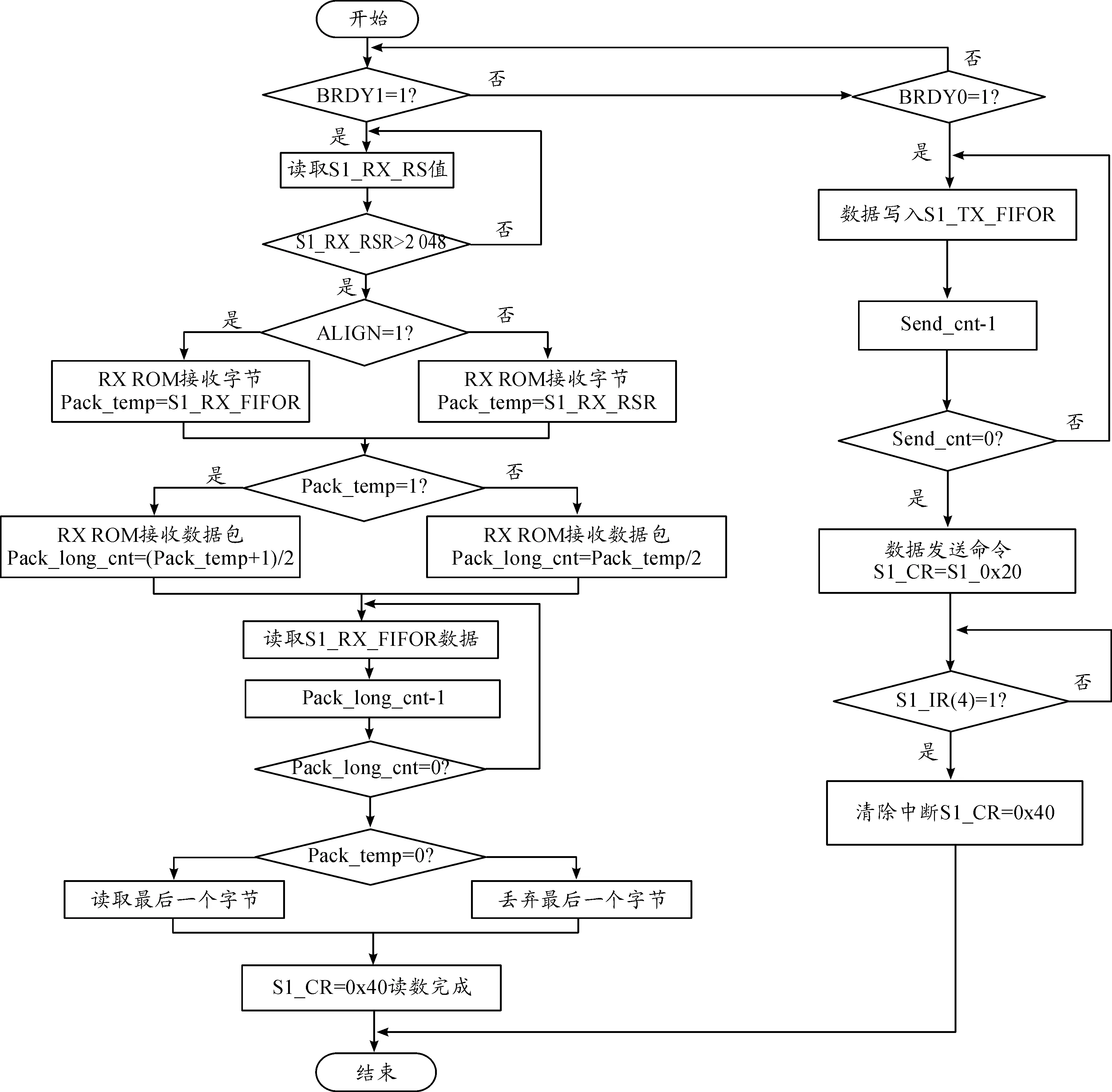

2.3 W5300数据发送和接收

在对以太网协议芯片W5300初始化和端口设置并连接成功后,便可以进行数据传输。首先客户端主动发送连接请求数据包SYN;服务器则执行侦听命令,等待客户端连接。图4以本系统中SOCKET1为例介绍W5300数据发送和接收流程。

在TCP模式下,当ALIGN=1时,RX接收到的数据包内只含有有效数据,主机可以从S1_RX_RSR寄存器直接获取RX的数据包长度;否则数据包由2Bytes的PACKET-INFO和有效数据组成,数据包信息包含在PACKET-INFO内,数据包长度保存在S1_RX_FIFOR寄存器中读取[11]。数据以包为单位读取,数据包长度作为数据读取循环控制量。当数据包字节长度为奇数时,数据最后一个字节为哑字节,需要直接丢弃。

当数据发送完成后,端口中断寄存器S1_IR(4)自动置1,并需要通过FPGA向W5300S1_IR(4)写1以清除中断标志位。

图4 W5300数据发送和接收流程

3 实验验证

本设计中,采用了TCP/IP通信协议,实现了客户端和服务器两个网络系统之间的数据传输。端口连接成功后,首先由客户端向服务器发送打包后的递增数,服务器收到数据后保存到Flash,再由测试台通过PXI总线传输到电脑保存,并通过上位机软件分解校验。接收数据时序图如图5,本系统控制器采用60 M时钟频率,11个时钟周期接收2 Byte数据,理论传输速度为87.27 Mbps。数据和校验结果如图6所示,结果无误码,无丢帧。

图5 接收数据时序图

图6 上位机软件报告和数据

此次测试共发送 5 150 437个数据包,其中1KB数据为一包。根据网络数据开始发送和数据发送停止时间可以算出以太网数据传输速度。在进行多次大量测试后,均无误码和丢帧现象出现,以太网数据实际传输速度可以达到85.79 Mbps,与设计指标相符。

4 结论

提出了采用“主控制器FPGA+网络协议芯片W5300”组成的网路数据传输系统,重点描述了W5300的寄存器配置流程。实践证明系统软件编写容易、结构简单、实用性强。经过大量实验验证,能够实现不同设备之间零误码传输,且速度达80 Mbps以上。该系统已经在高速数据图像传输工程中得到应用。